Optical modeling proximity correction method of SRAM (Static Random Access Memory) grid dimension

A technology of proximity correction and gate size, which is applied in the direction of optics, photolithography on the pattern surface, and originals for photomechanical processing, etc., can solve the problems of reducing the process window of lithography and device performance, and achieve large process window effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0017] The specific embodiment of the present invention will be further described below in conjunction with accompanying drawing:

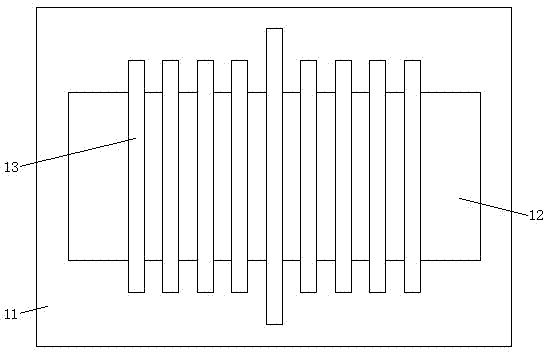

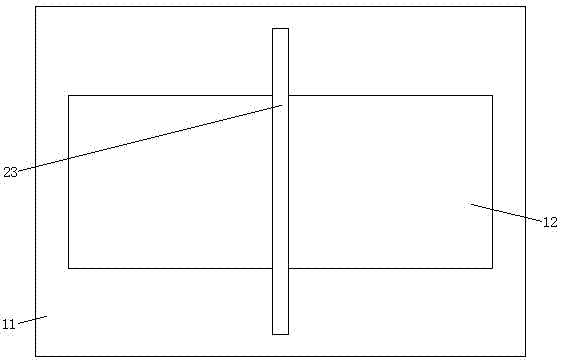

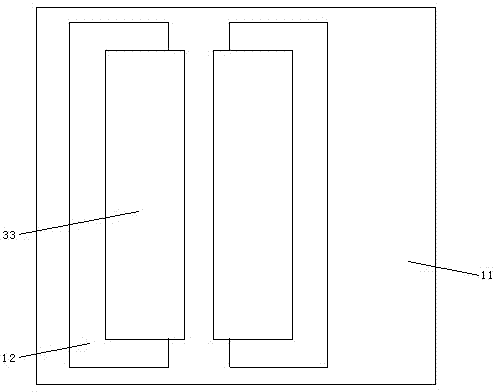

[0018] Such as Figure 1-5 As shown, the optical modeling approach correction method of the SRAM gate size of the present invention, first, prepare a test wafer, and design the line width size, spacing size, pitch, line end spacing size and active area according to the process requirements Design the pattern of the active area mask and the gate mask in terms of size, etc.; secondly, on the test wafer, use the active area mask to carry out the active area preparation process on the test wafer to form the active area 12; after that , continue the shallow trench process, after forming the shallow trench isolation region 11 surrounding the active region 12, the gate process is performed, and the gate mask is used to form the dense line size test structure design on the active region respectively during the photolithography process Domain 13 (as figu...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More