A test head for automatic inspection of wafer-level packaging chips and its implementation method

A wafer-level packaging and test head technology, applied in the field of test heads, can solve the problems of high cost and low efficiency of manual test methods, achieve high test efficiency and meet the requirements of automated testing

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0026] The present invention will be described in further detail below in conjunction with accompanying drawing and specific embodiment:

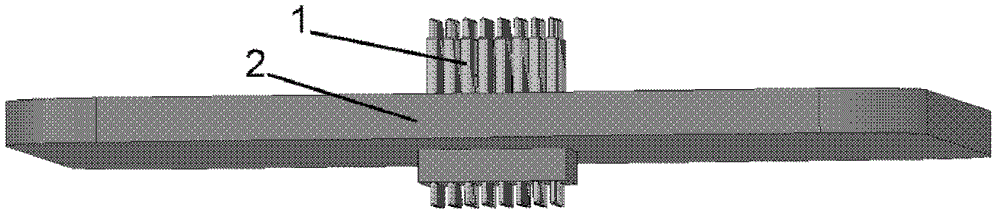

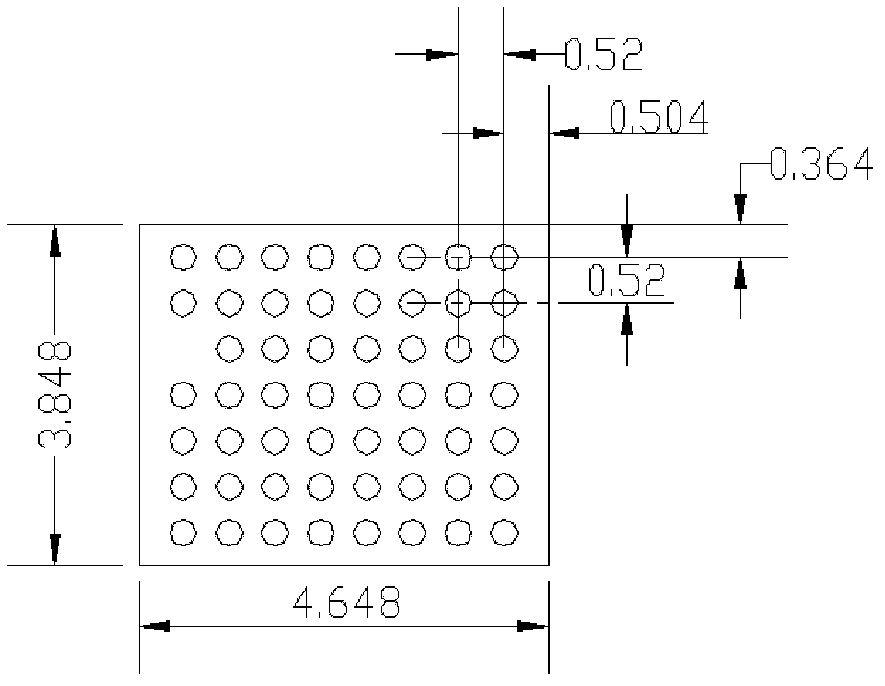

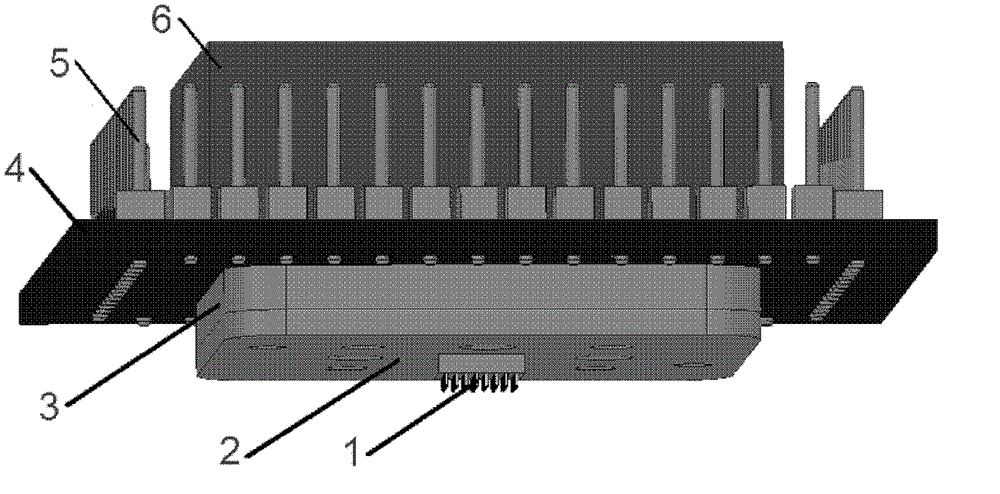

[0027] According to the test requirements of an IC chip, select the probe model, such as the selected probe is DE1-030EF40-010 double-headed probe, according to the package size and bump layout of a single IC chip on the wafer, such as figure 2 , design the corresponding fixed probes on the probe plate 2 of the array probe 1, such as image 3 , and then design the probe guide plate 3, (the specific structure of the probe guide plate is as follows Figure 4 As shown), in order to install and replace the probe array, design the PCB board 4, etch the connection point corresponding to the probe array 1 on the PCB board, and lead the wiring of the probe array to the periphery of the PCB through the wiring of the PCB board. And make the insertion pin 5, the signal of microarray probe test like this can be connected to the test box through the i...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More