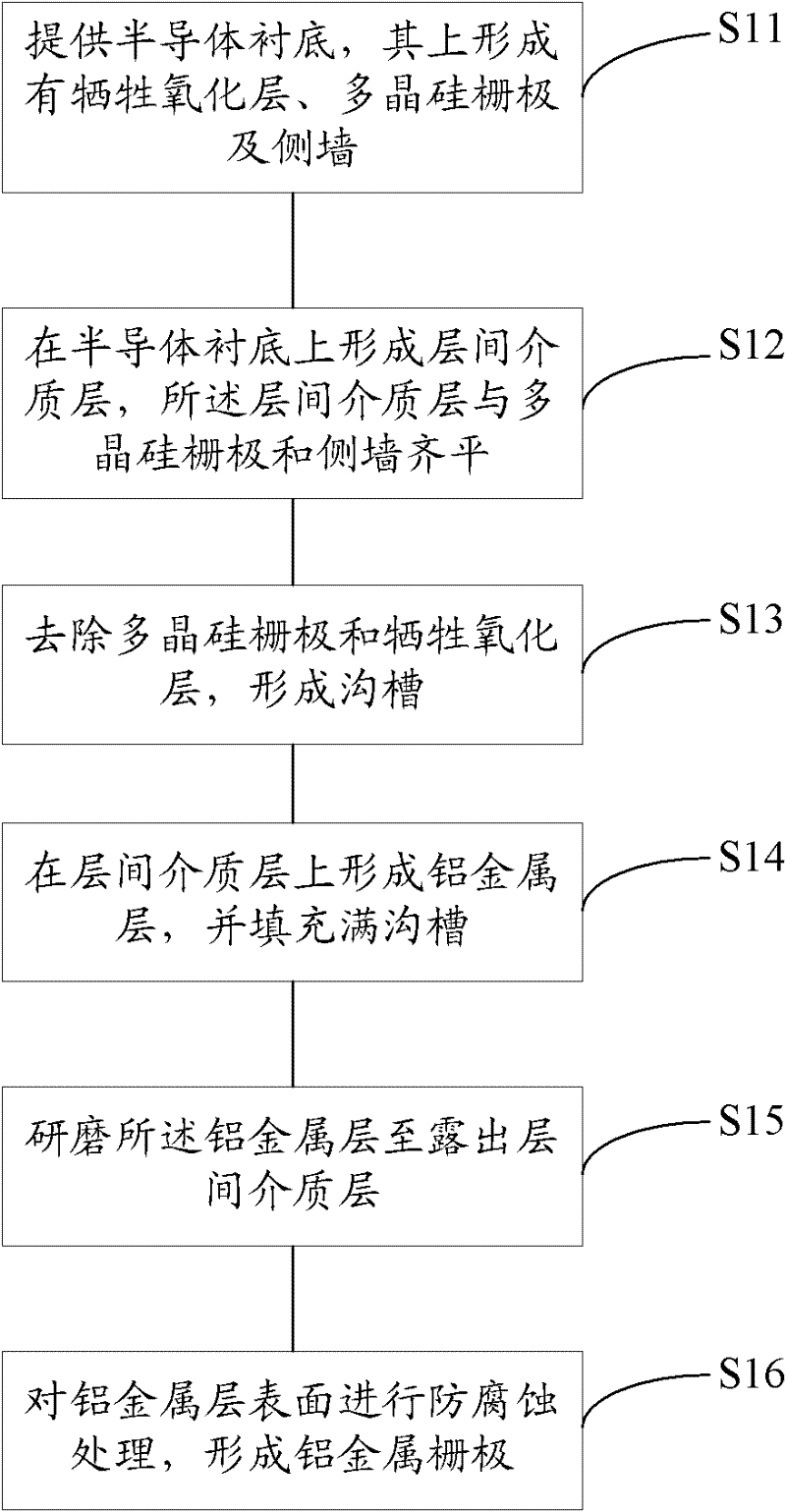

Method for forming aluminum metal gate

An aluminum metal and gate technology, which is applied in the field of semiconductor manufacturing process, can solve the problems affecting the reliability of semiconductor devices and the resistivity deviation of aluminum metal gates, and achieve the effects of ensuring normal resistivity, improving reliability and avoiding corrosion.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

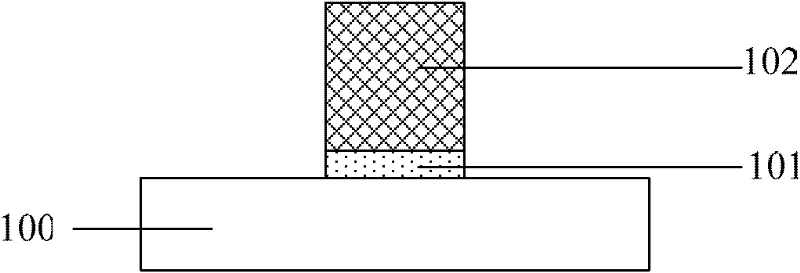

[0043] Figure 2 to Figure 4 It is a schematic diagram of the first specific embodiment of the method for forming an aluminum metal gate provided by the present invention. Such as figure 2 As shown, a semiconductor substrate 100 is provided; a sacrificial oxide layer 101 and a polysilicon gate 102 are sequentially formed on the semiconductor substrate 100. A sacrificial oxide layer 101 is formed on the sacrificial oxide layer; a polysilicon layer is formed on the sacrificial oxide layer 101; a first photoresist layer (not shown) is formed on the polysilicon layer, and a grid pattern is defined after exposure and development; The first photoresist layer is a mask, and the polysilicon layer and the sacrificial oxide layer 102 are etched along the gate pattern to expose the semiconductor substrate 100 to form the polysilicon gate 102 .

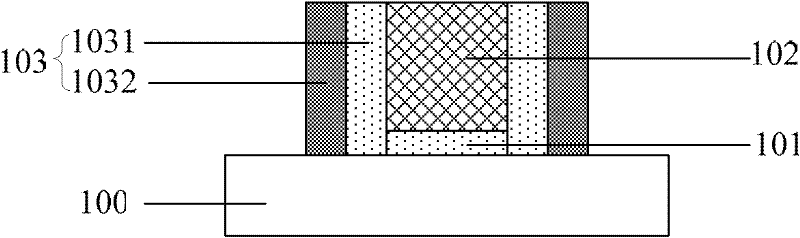

[0044] Such as image 3As shown, side walls 103 are formed on the semiconductor substrate 100 on both sides of the polysilicon gate 102; Th...

no. 2 example

[0055] Figure 8 to Figure 14 It is a schematic diagram of a second specific embodiment of the method for forming an aluminum metal gate of the present invention. Such as Figure 8 As shown, a semiconductor substrate 200 is provided; a sacrificial oxide layer 201 and a polysilicon gate 202 are sequentially formed on the semiconductor substrate 200 , and the specific process for forming the polysilicon gate 202 is as described in the first embodiment.

[0056] Such as Figure 9 As shown, sidewalls 203 are formed on the semiconductor substrate 200 on both sides of the polysilicon gate 202; the sidewalls 203 include a silicon oxide layer 2031 and a silicon nitride layer 2032 located on both sides of the polysilicon. Example.

[0057] Such as Figure 10 As shown, an interlayer dielectric layer 204 is formed on a semiconductor substrate 200; the surface of the interlayer dielectric layer 204 is flush with the tops of the polysilicon gate 202 and the sidewall 203, and the specif...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More