Instruction acquisition control method based on simultaneous multithreading

A control method and multi-threading technology, applied in program control design, concurrent instruction execution, instrumentation, etc., can solve the problems of introducing branch alias interference, limiting the performance of simultaneous multi-thread processors, and high conflict rate of instruction queues

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0075] The present invention is described in more detail below in conjunction with accompanying drawing example:

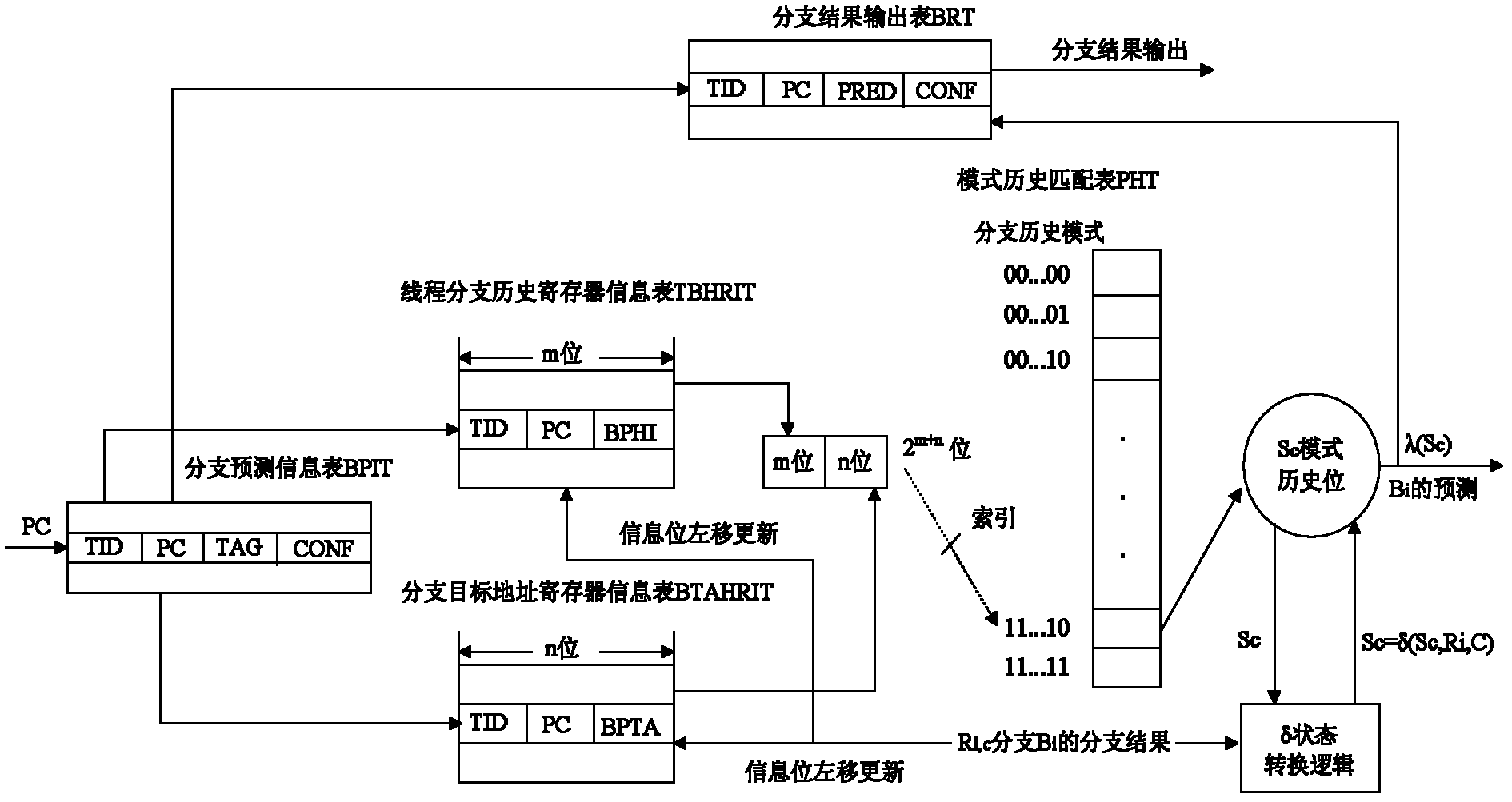

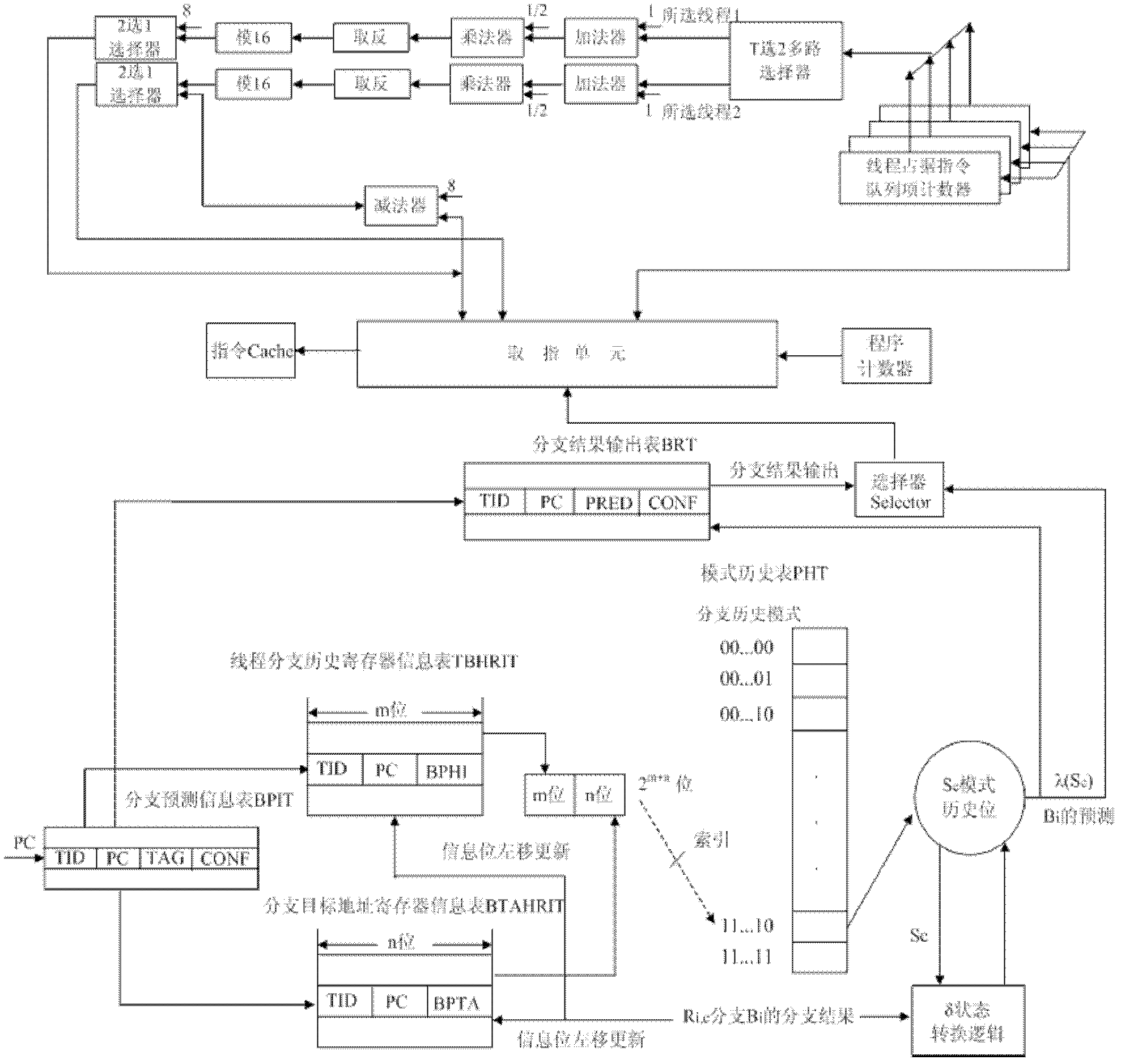

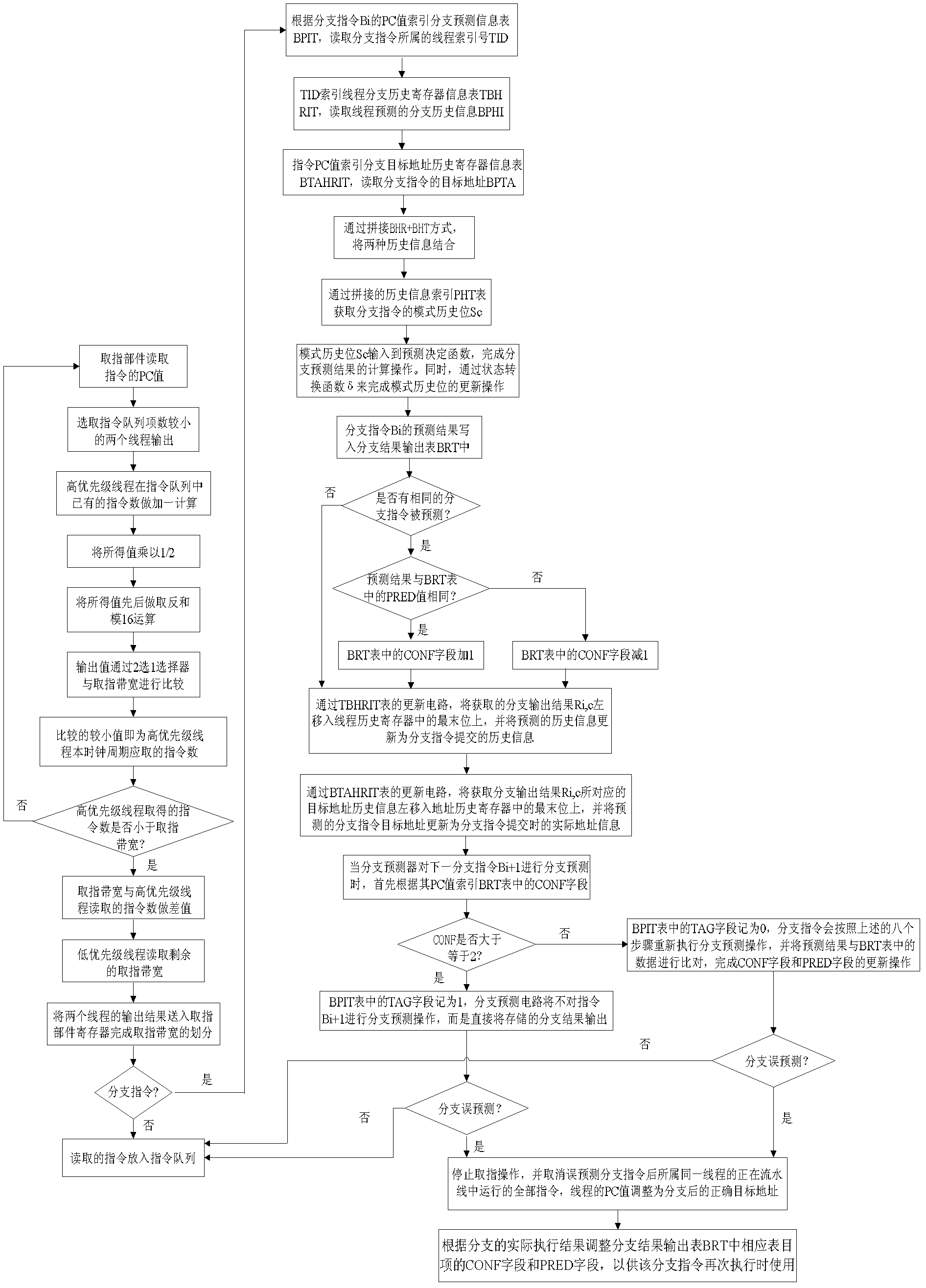

[0076] The entire implementation process of the FCMBSMT instruction fetching control method is divided into two stages: reading instructions, branch prediction of instructions, and the execution order of the two is not sequential, and the simultaneous multi-threaded processor is completed through the interaction of the two. Fetch operation. combine figure 2 with image 3 The specific implementation process of the invented control FCMBSMT based on simultaneous multi-thread instruction fetching is as follows:

[0077] Step 1: In each clock cycle of the processor, the fetching unit reads the PC value of the instruction according to the program counter.

[0078] Step 2: Select the two threads with the smallest counter values of the number of items in the instruction queue through the T selection 2 multiplexer for output, assuming that the priority of thread 1 is...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More