Patents

Literature

282 results about "Pattern type" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

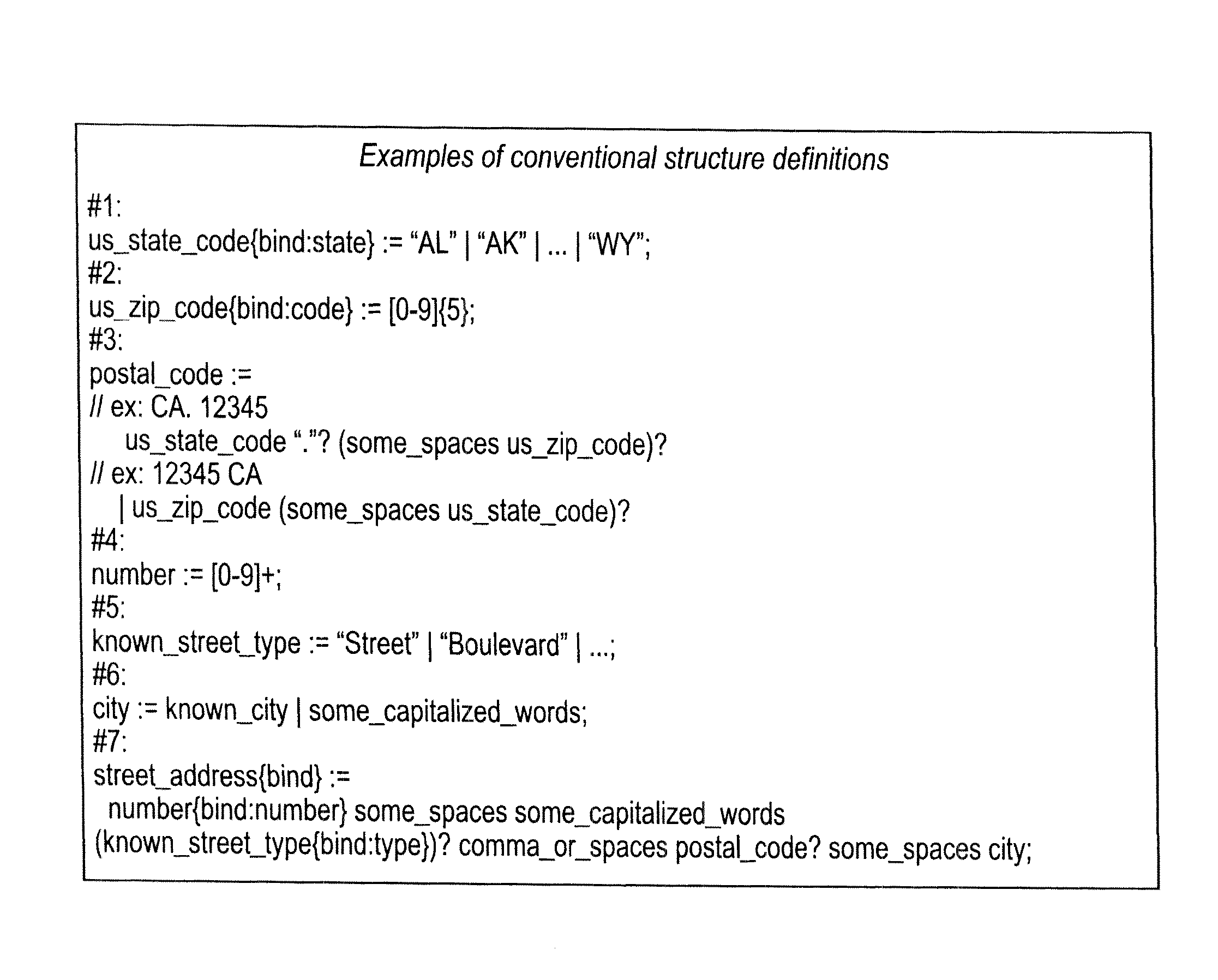

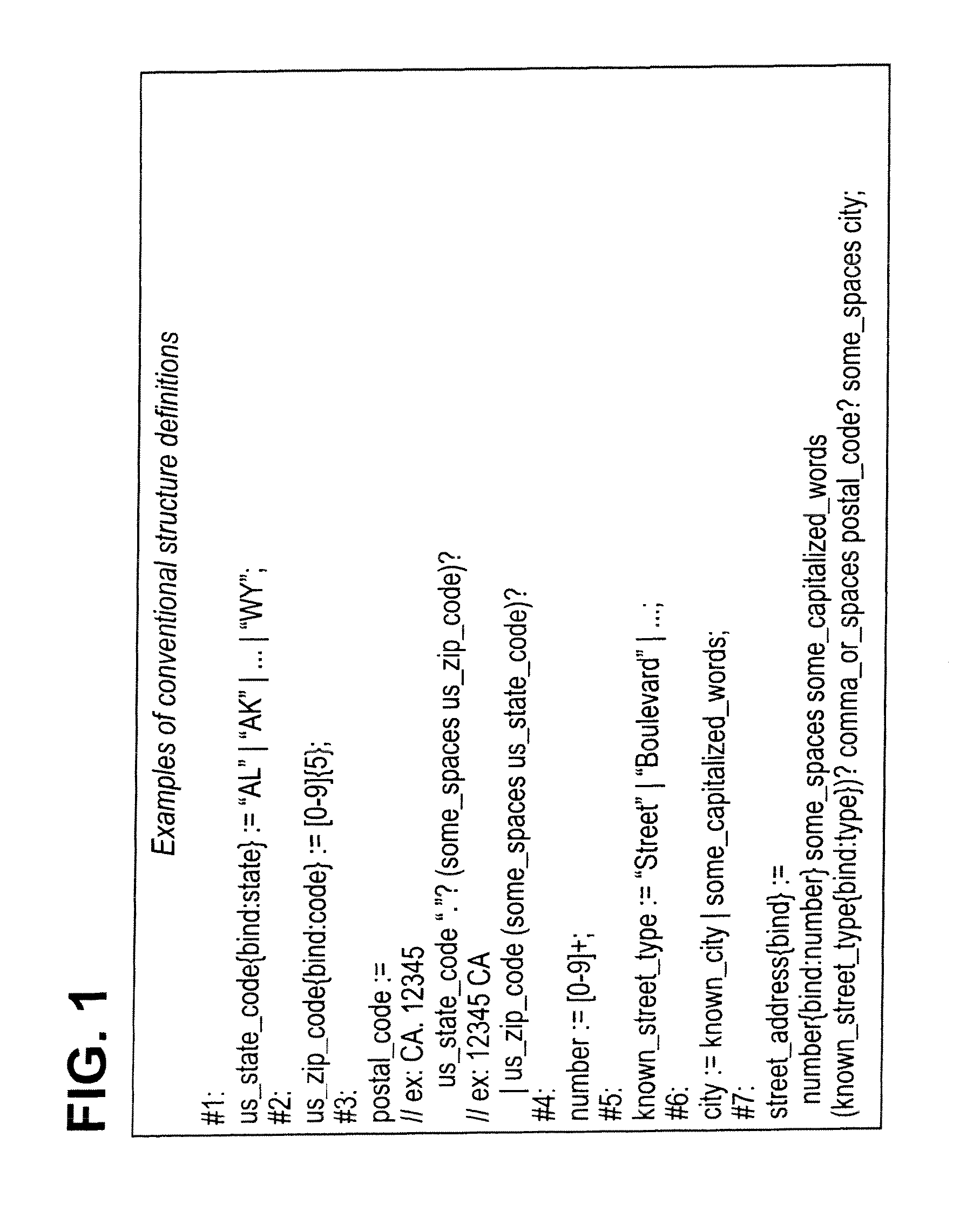

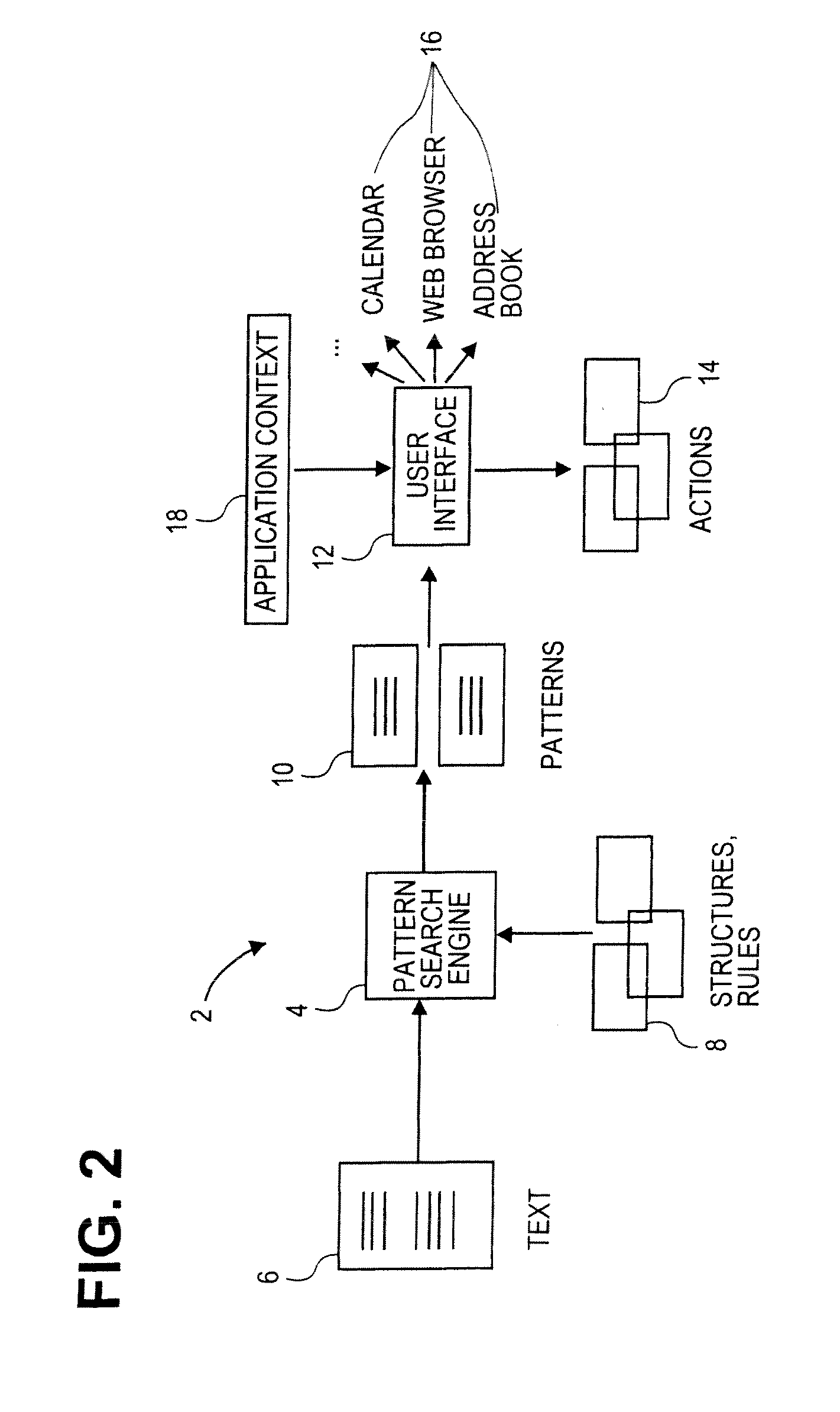

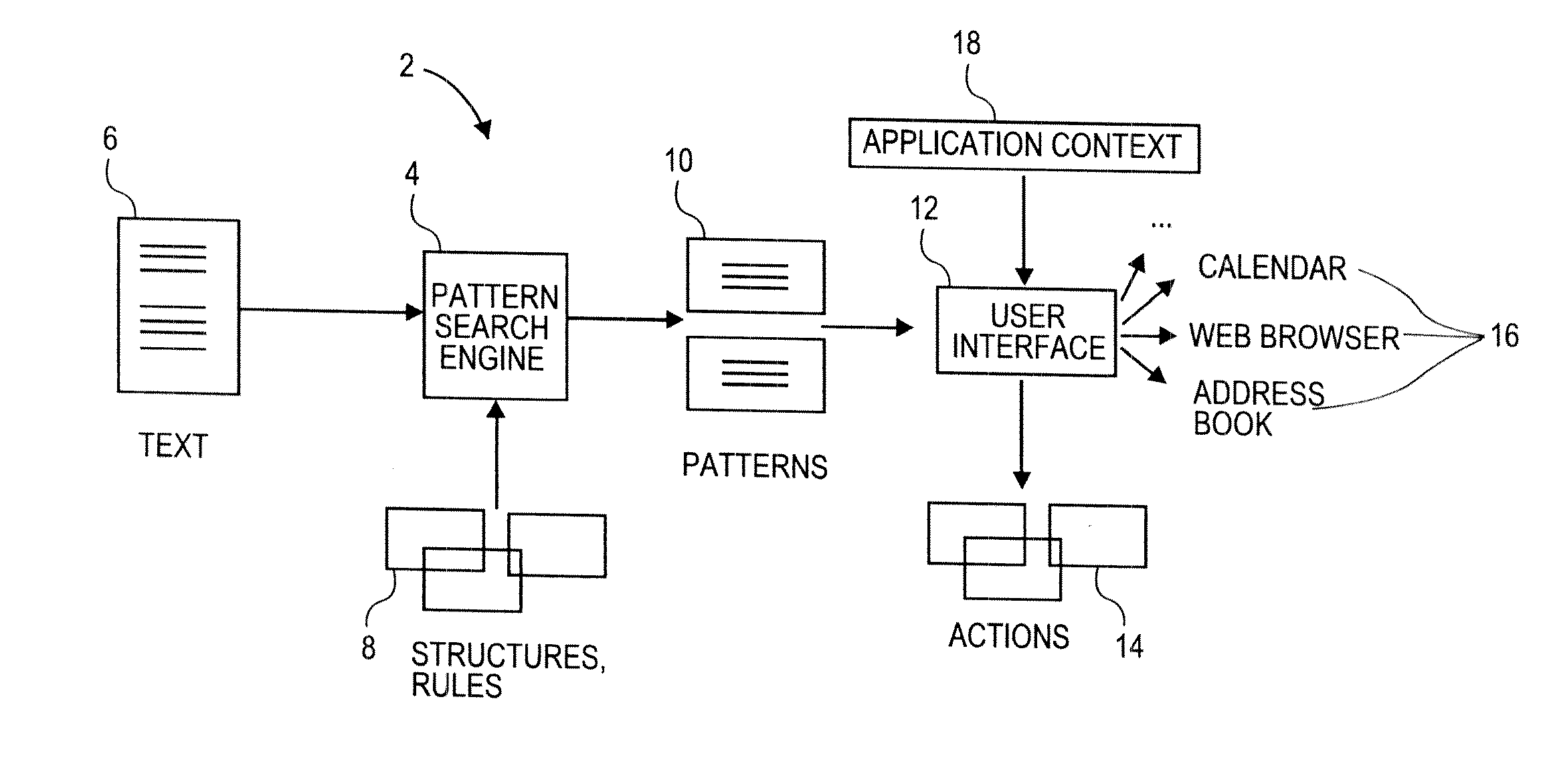

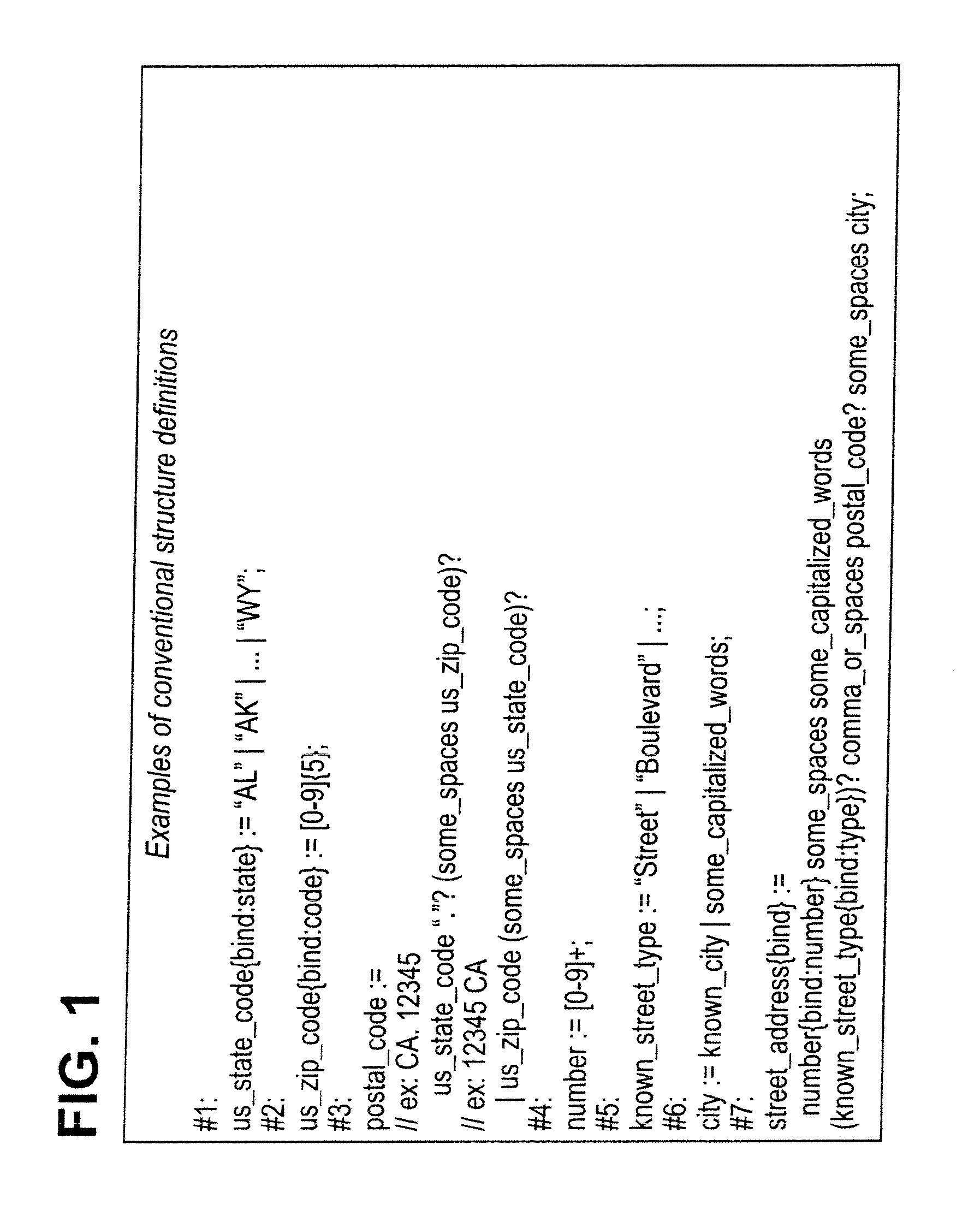

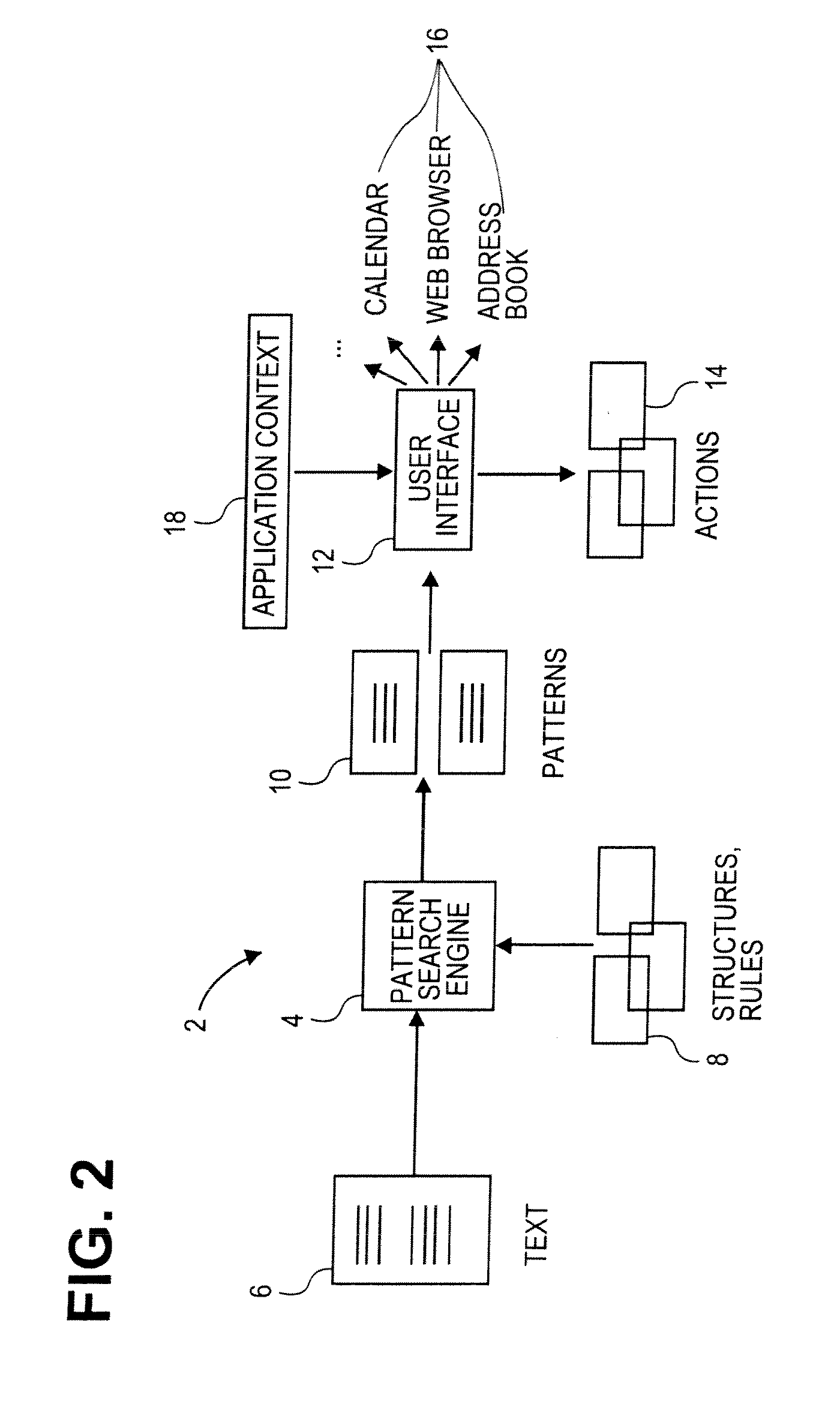

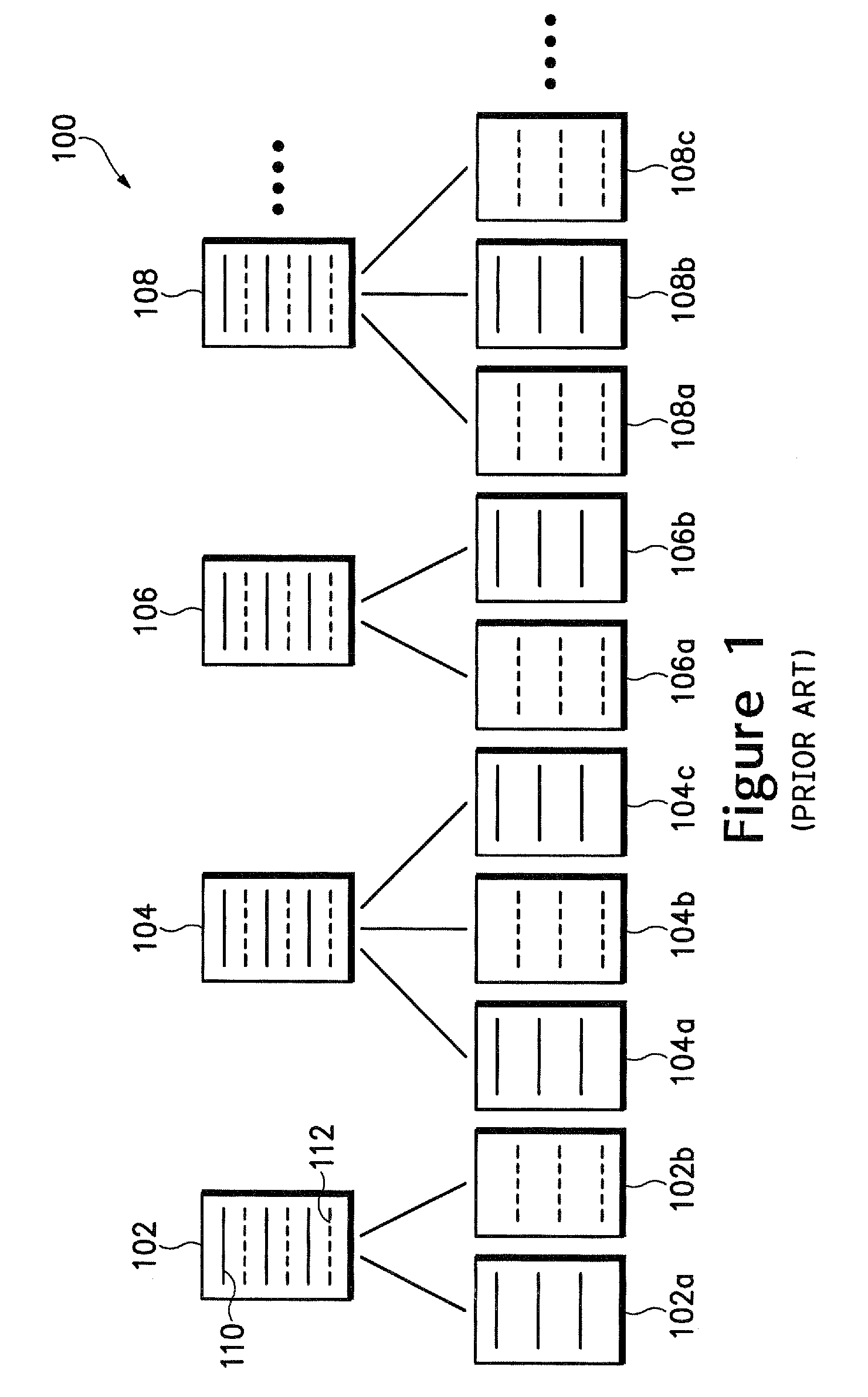

Pattern searching methods and apparatuses

InactiveUS7912828B2Avoid less flexibilityMore freedomDigital data information retrievalDigital data processing detailsStructure recognitionData mining

A computer-based method for identifying patterns in computer text using structures defining types of patterns which are to be identified, wherein a structure comprises one or more definition items, the method comprising assigning a weighting to each structure and each definition item; searching the computer text for a pattern to be identified on the basis of a particular structure, a pattern being provisionally identified if it matches the definition given by said particular structure; in a provisionally identified pattern, determining those of the definition items making up said particular structure that have been identified in the provisionally identified pattern; combining the weightings of the determined definition items and optionally, the weighting of the particular structure, to a single quantity; assessing whether the single quantity fulfils a given condition; depending on the result of said assessment, rejecting or confirming the provisionally identified pattern.

Owner:APPLE INC

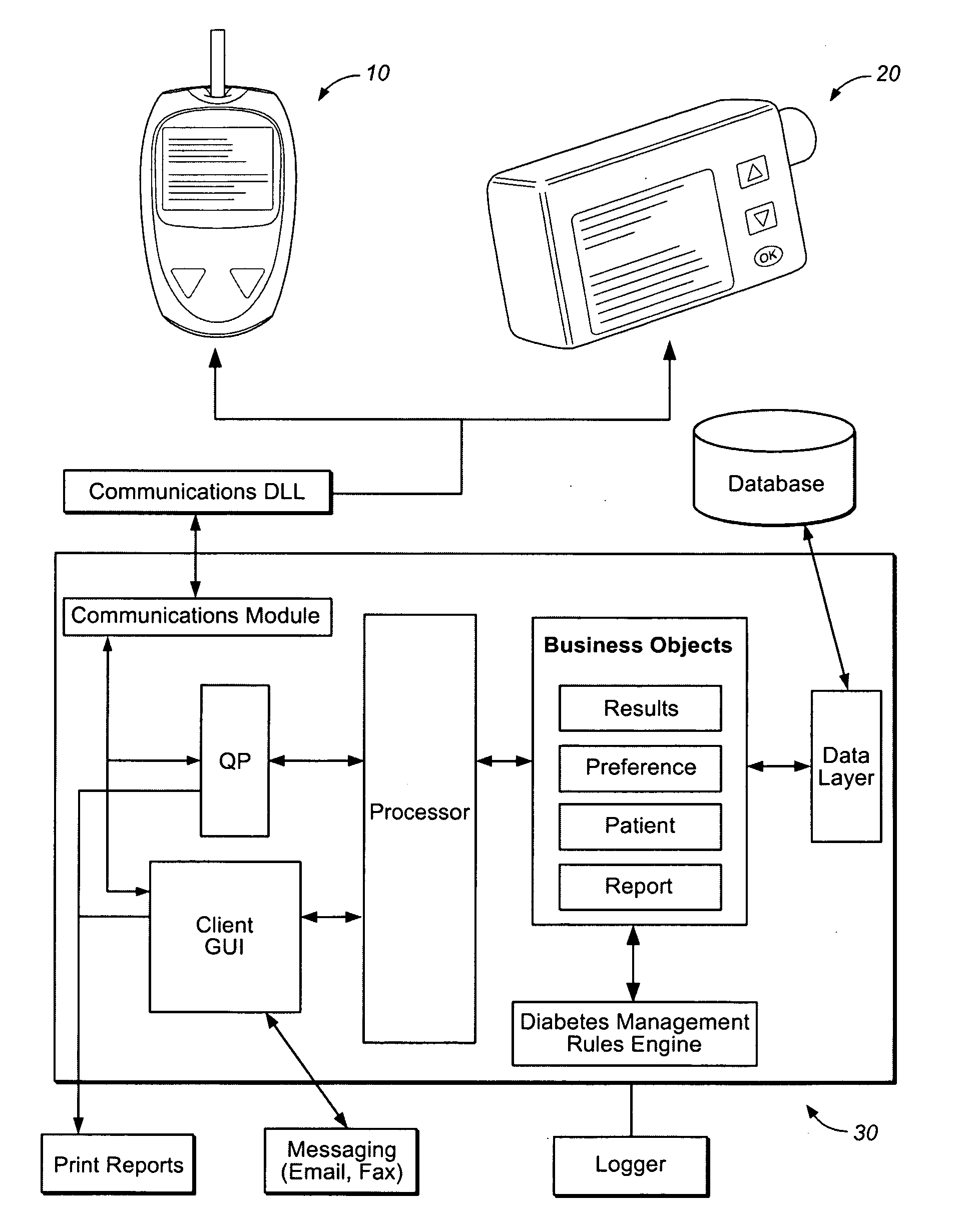

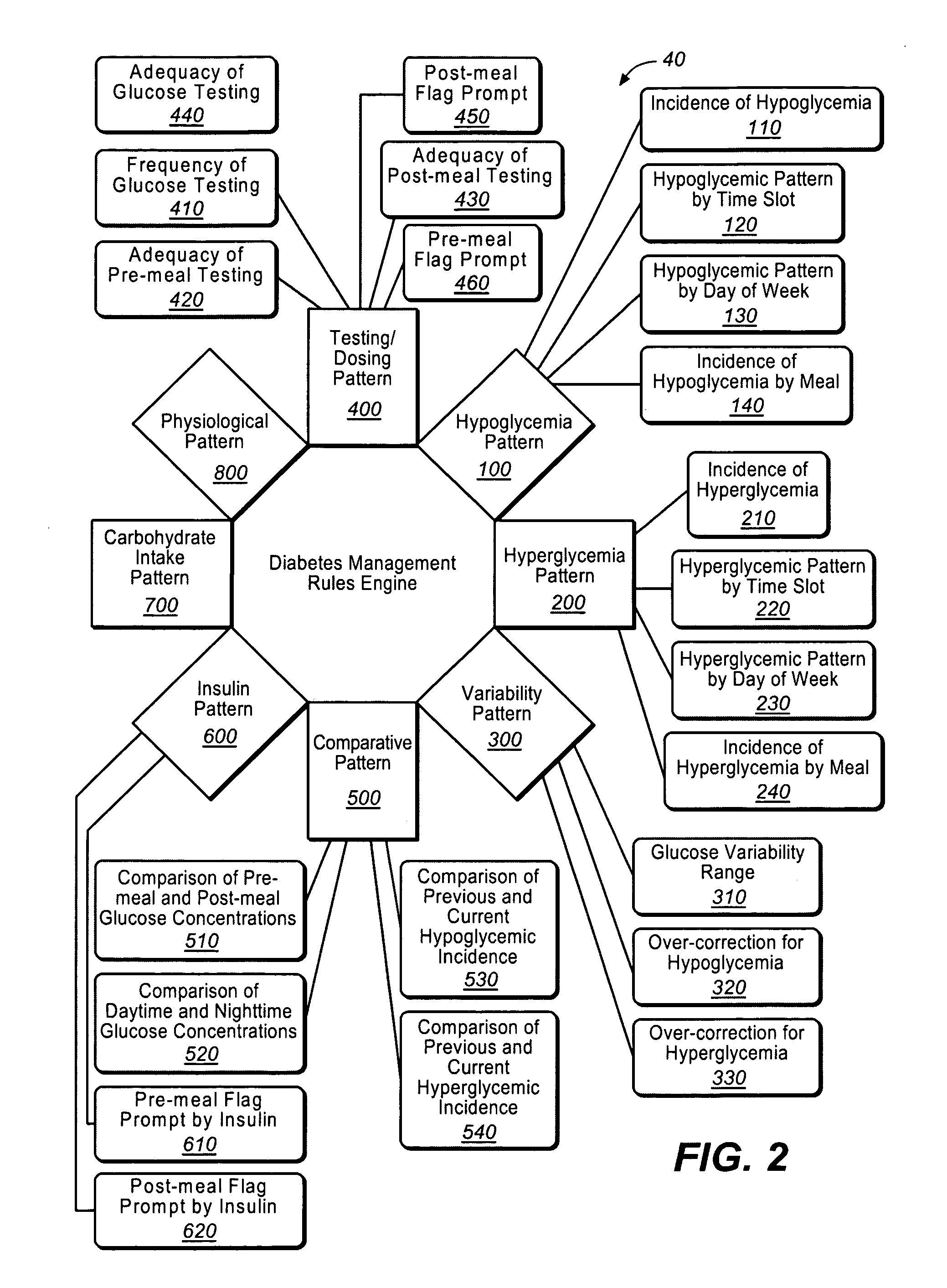

Methods of determining pre or post meal time slots or intervals in diabetes management

A diabetes management system or process is provided herein that may be used to analyze and recognize patterns for a large number of blood glucose concentration measurements and other physiological parameters related to the glycemia of a patient. In particular, a method of monitoring glycemia in a patient may include storing a patient's data on a suitable device, such as, for example, a blood glucose meter. The patient's data may include blood glucose concentration measurements. The diabetes management system or process may be installed on, but is not limited to, a personal computer, an insulin pen, an insulin pump, or a glucose meter. The diabetes management system or process may identify a plurality of pattern types from the data including a testing / dosing pattern, a hypoglycemic pattern, a hyperglycemic pattern, a blood glucose variability pattern, and a comparative pattern. After identifying a particular pattern with the data management system or process, a warning message may be displayed on a screen of a personal computer or a glucose meter. Other messages can also be provided to ensure compliance of any prescribed diabetes regiments or to guide the patient in managing the patient's diabetes.

Owner:LIFESCAN INC

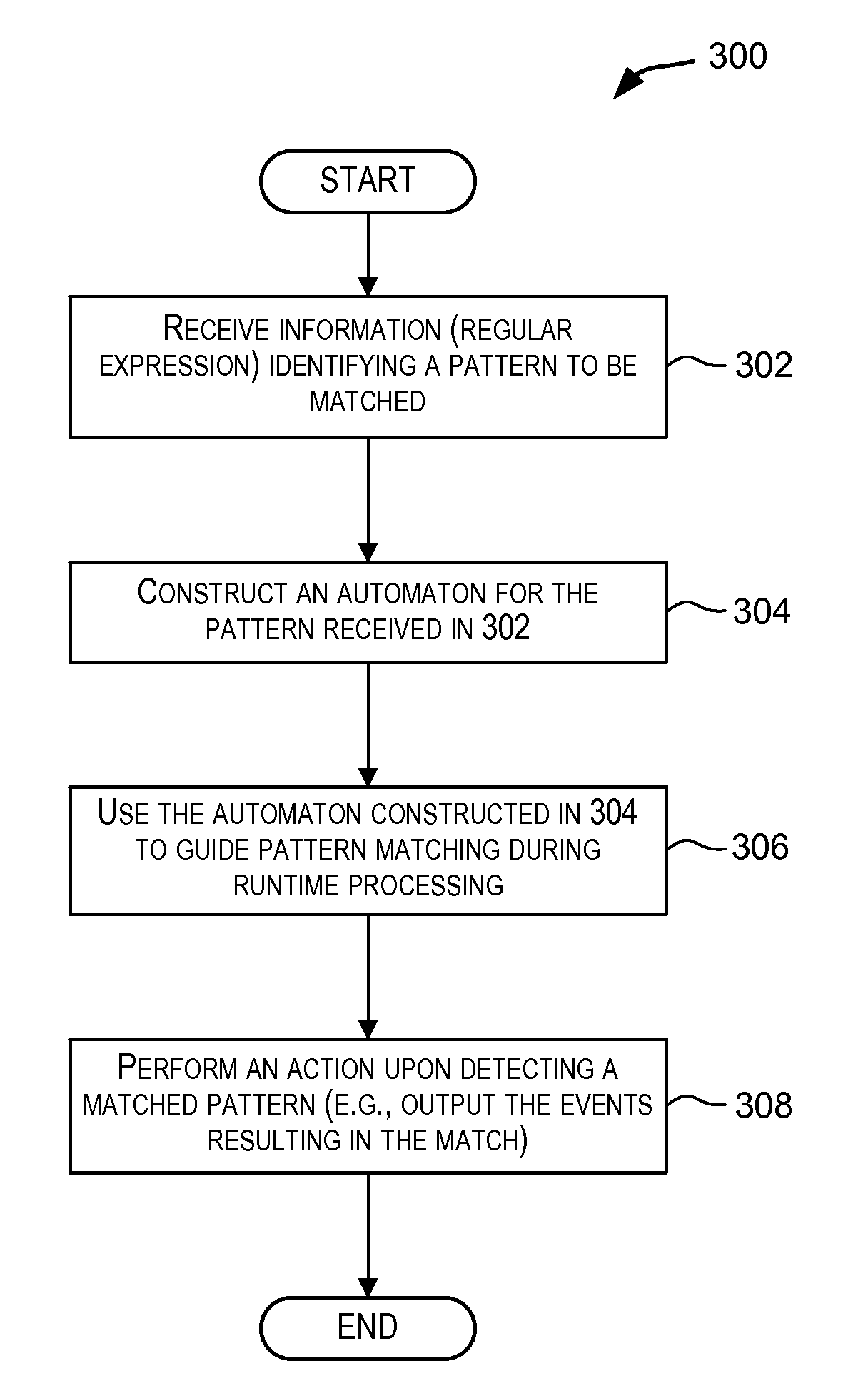

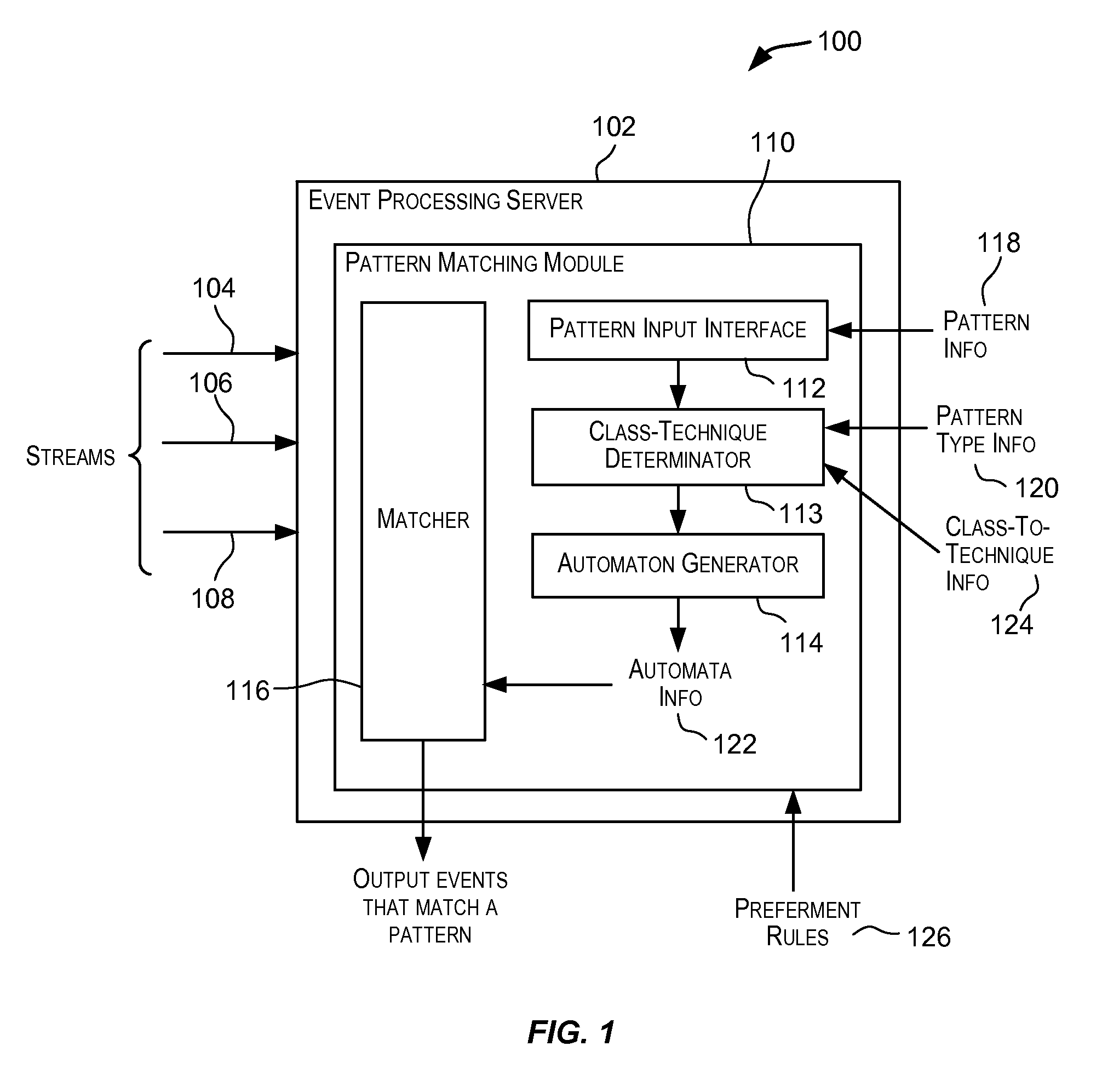

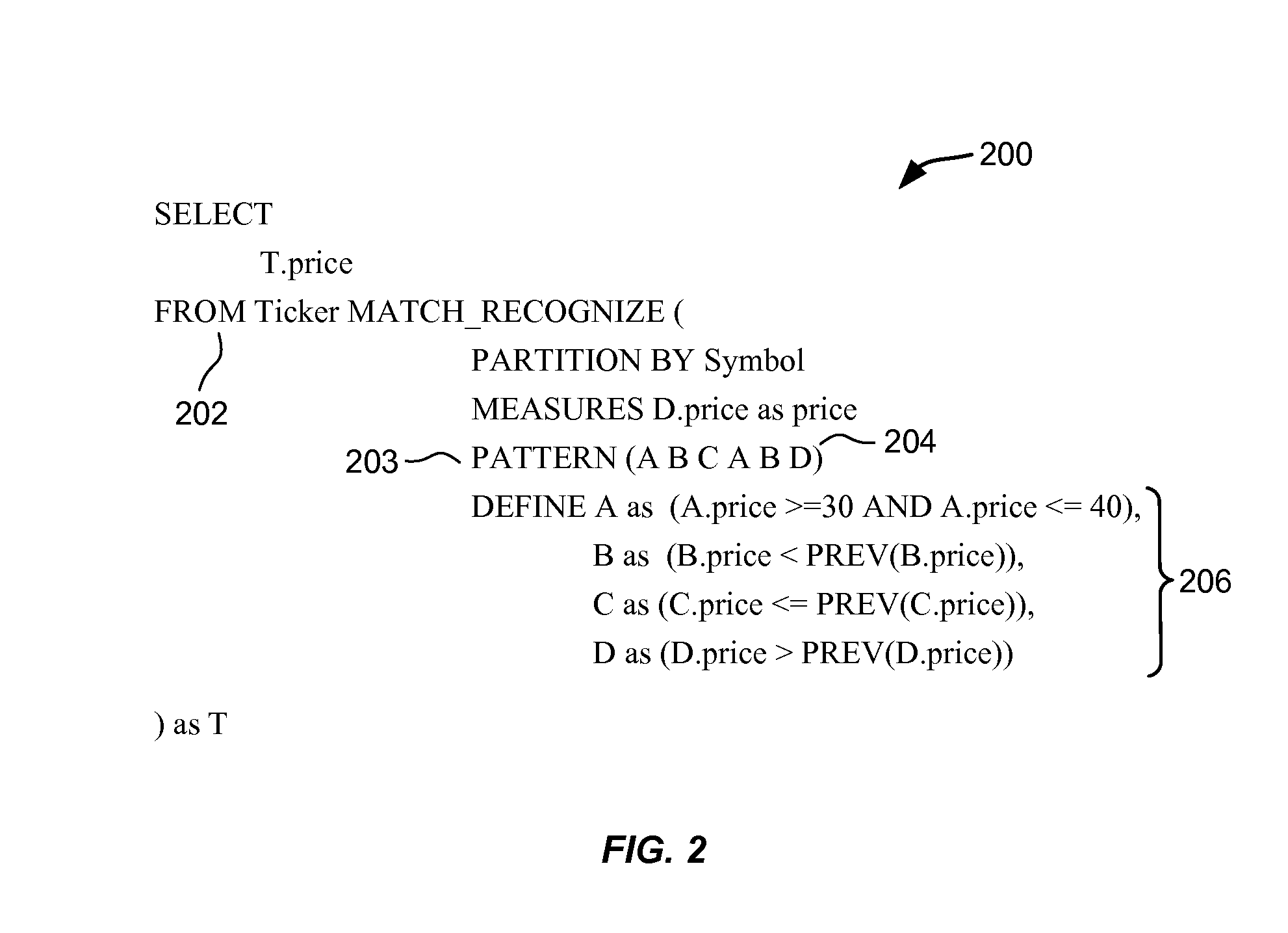

Framework for supporting regular expression-based pattern matching in data streams

ActiveUS20100057735A1Digital data processing detailsCharacter and pattern recognitionPattern recognitionData stream

Techniques for detecting patterns in one or more data or event streams. A pattern to be detected may be specified using a regular expression. Events received in a data stream are processed during runtime to detect occurrences of the specified pattern in the data stream. In one embodiment, a pattern type or class is determined for the specified pattern and pattern matching is performed using a technique selected based upon the type or class determined for the specified pattern.

Owner:ORACLE INT CORP

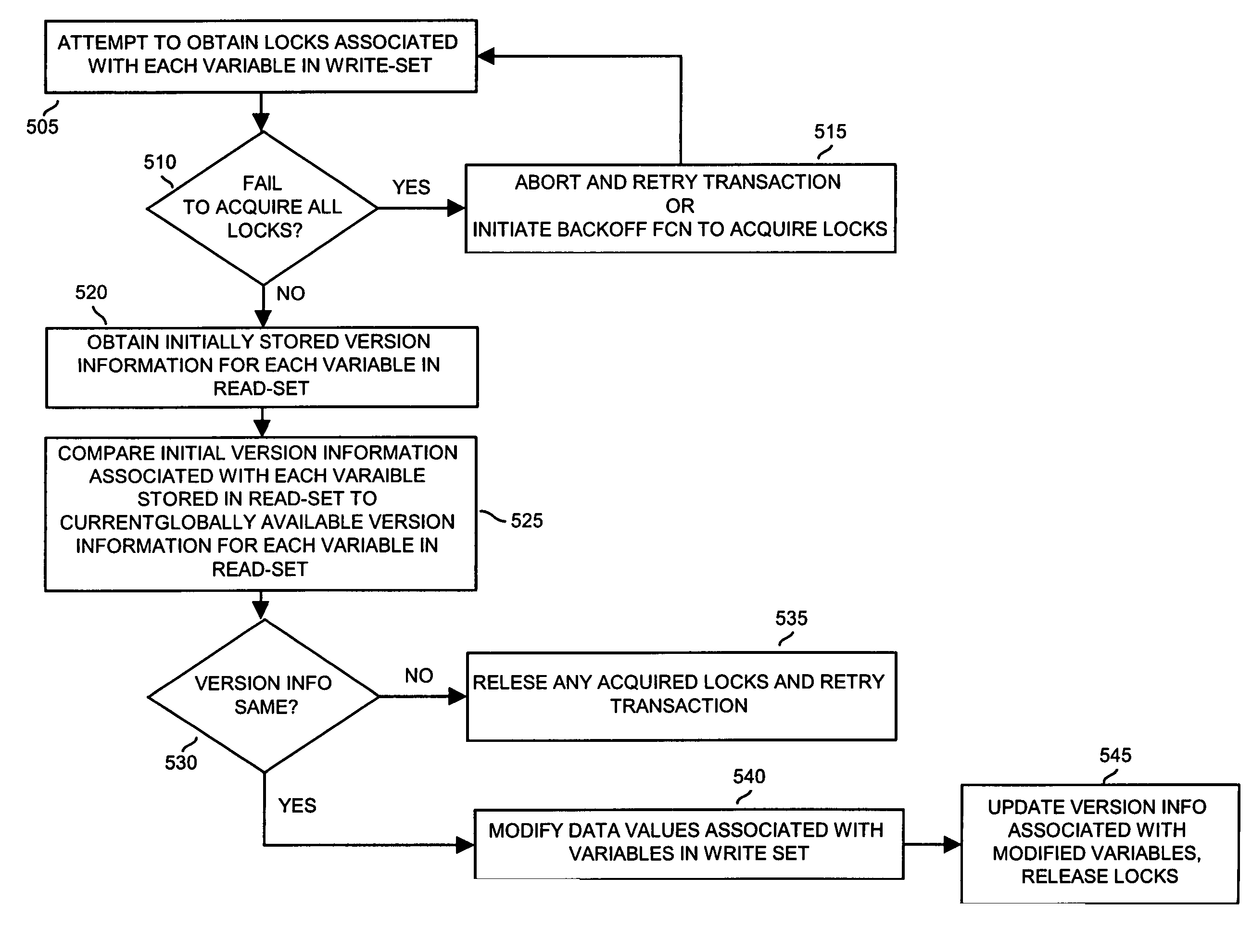

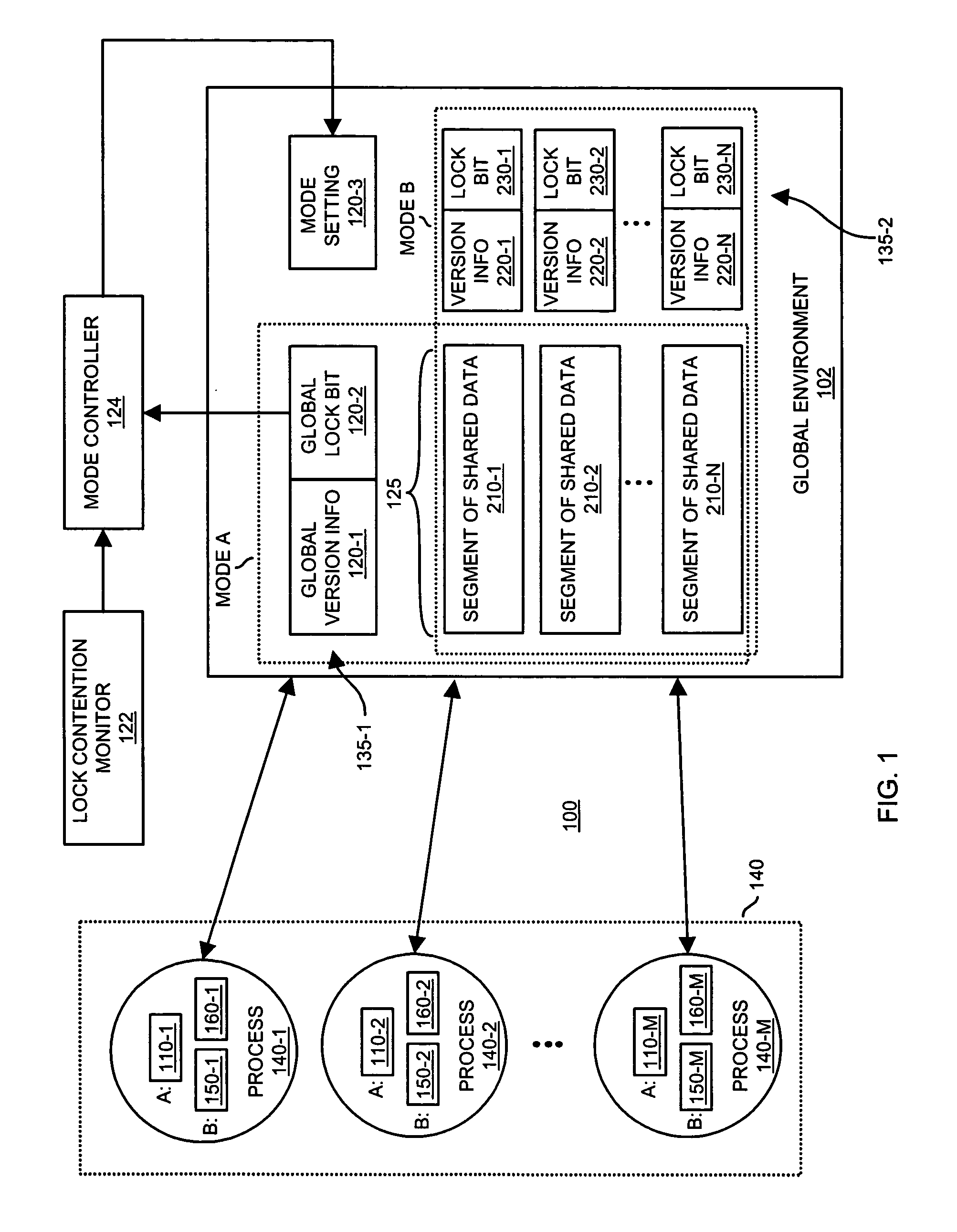

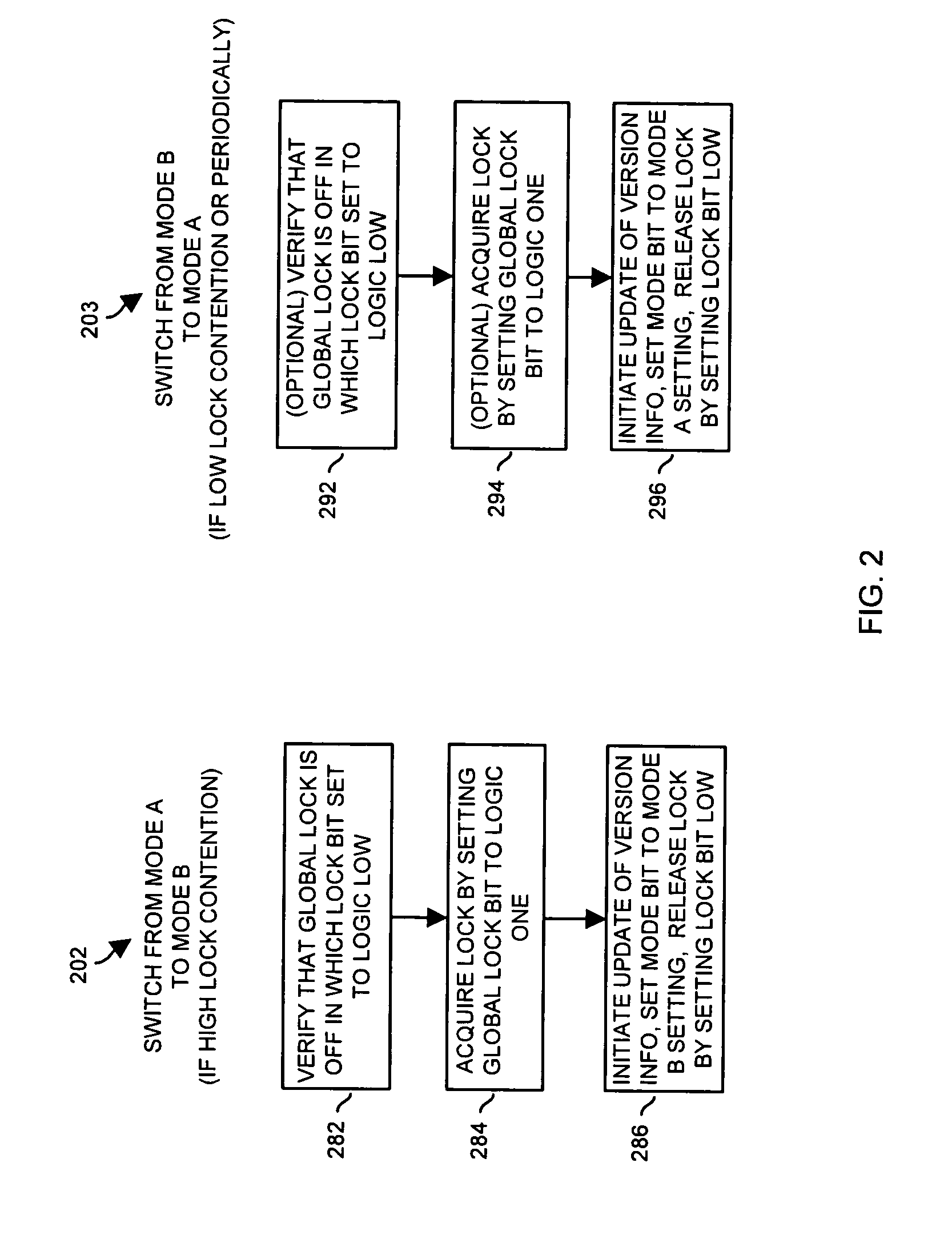

Methods and apparatus to implement parallel transactions

ActiveUS20070198792A1Program synchronisationUnauthorized memory use protectionMode controlParallel computing

A computer system includes multiple processing threads that execute in parallel. The multiple processing threads have access to a global environment including different types of metadata enabling the processing threads to carry out simultaneous execution depending on a currently selected type of lock mode. A mode controller monitoring the processing threads initiates switching from one type of lock mode to another depending on current operating conditions such as an amount of contention amongst the multiple processing threads to modify the shared data. The mode controller can switch from one lock mode another regardless of whether any of the multiple processes are in the midst of executing a respective transaction. A most efficient lock mode can be selected to carry out the parallel transactions. In certain cases, switching of lock modes causes one or more of the processing threads to abort and retry a respective transaction according to the new mode.

Owner:ORACLE INT CORP

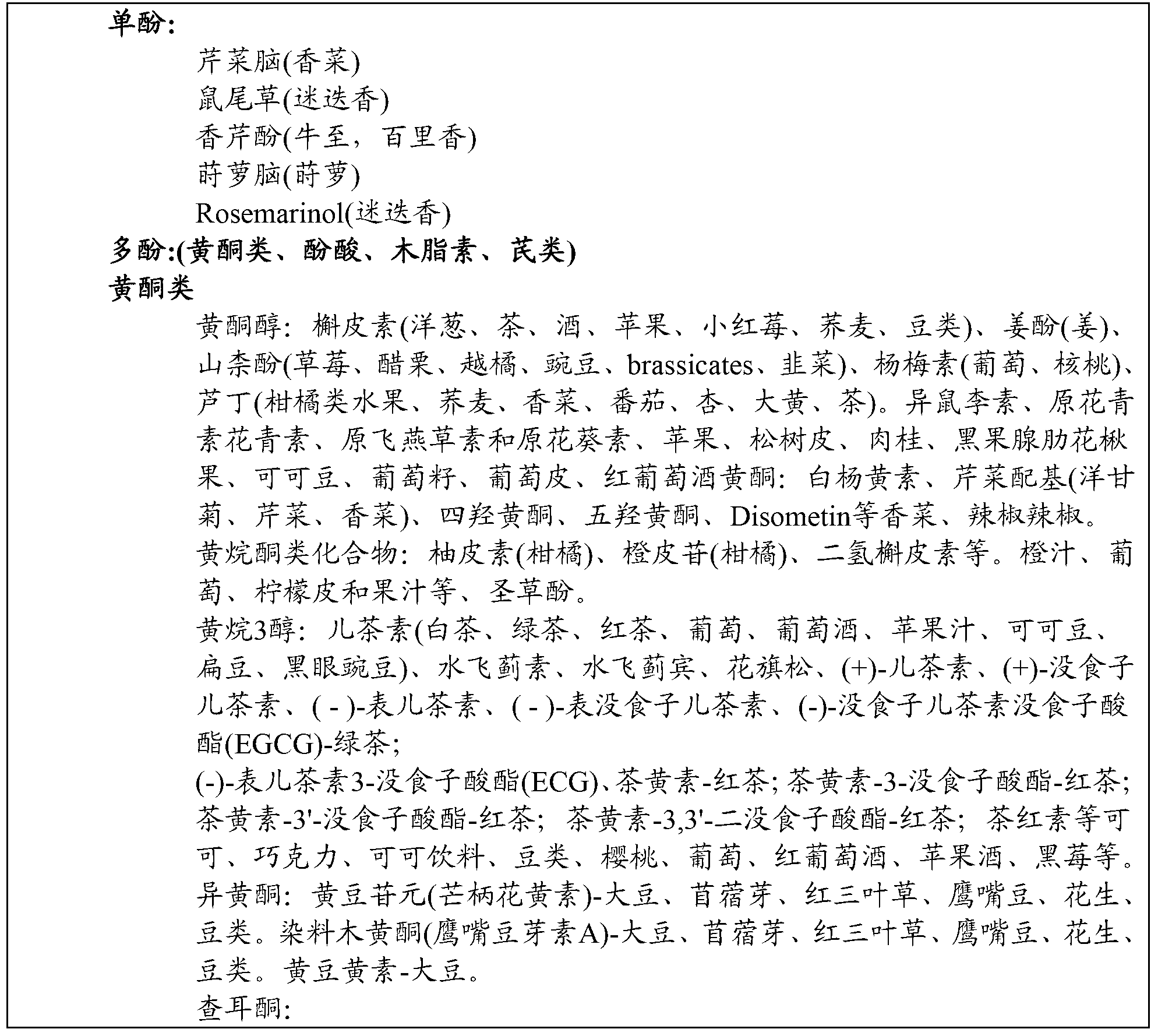

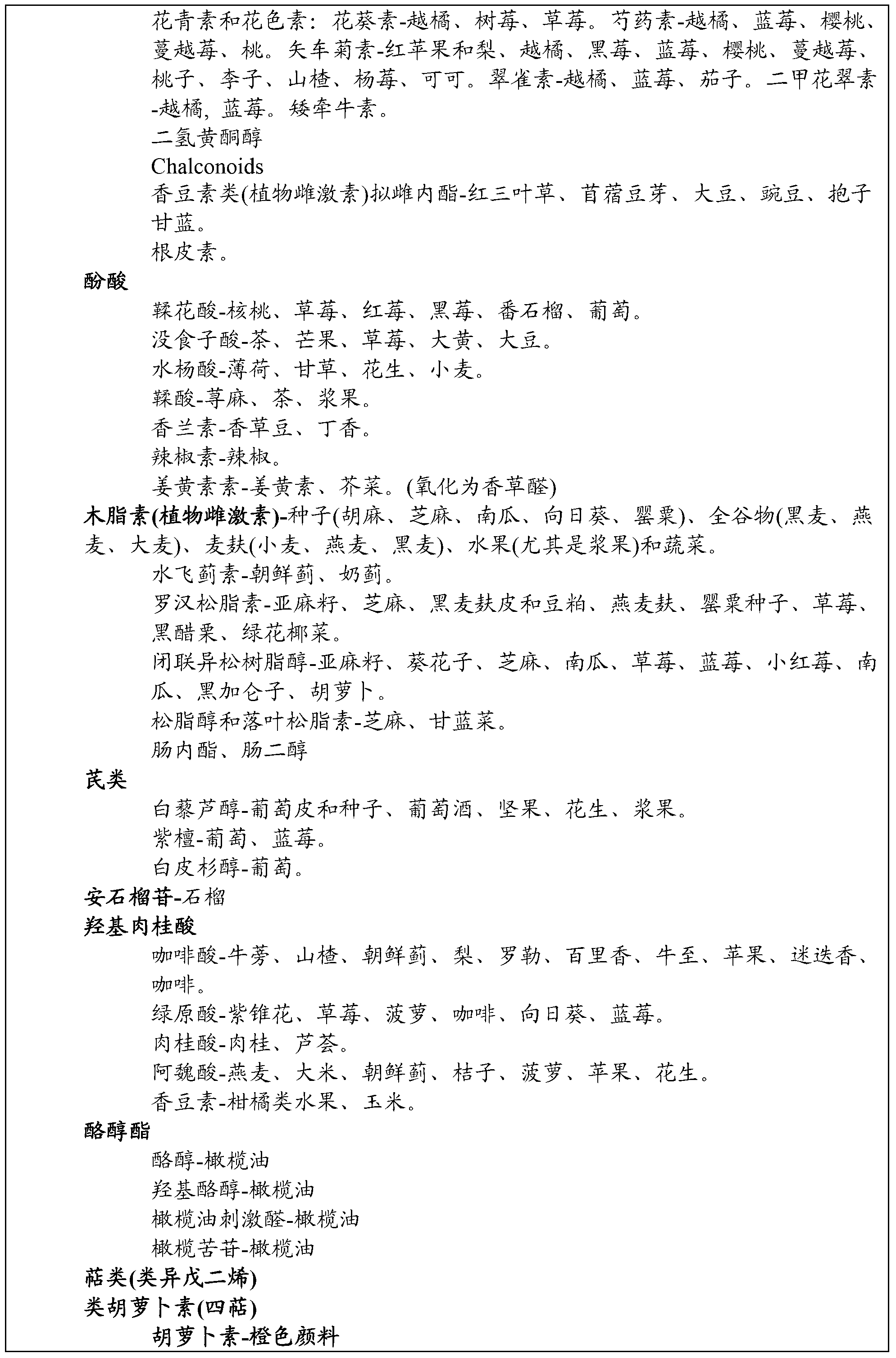

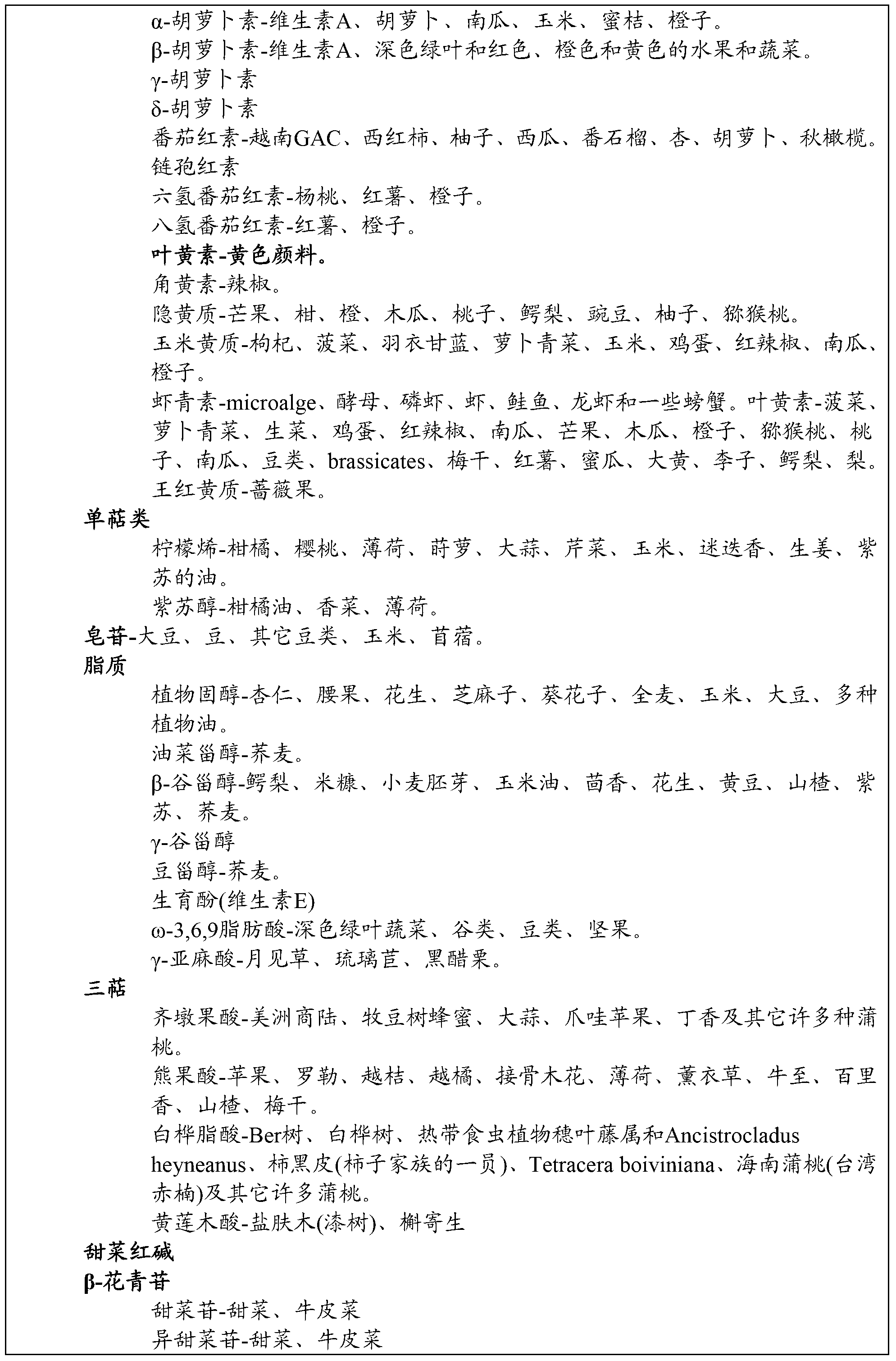

Optimized nutritional formulations, methods for selection of tailored diets therefrom, and methods of use thereof

PendingUS20130261183A1Safely selectConveniently maintain nutritional balanceOrganic active ingredientsSenses disorderFiberPhytochemical

Nutritional compositions and formulations that optimize nutritional contents are provided. Dietary compositions and methods for tailoring such compositions to optimize levels of nutrients that have beneficial effects within specific ranges are provided. Dietary plans, and formulations comprising dietary products that comprise optimized levels of nutrients derived from phytochemicals, antioxidants, vitamins, minerals, lipids, proteins, carbohydrates, probiotics, prebiotics, microorganisms and fiber. Diet plans and modular nutritional packages comprising food and drink items tailored according to consumer patterns typed by diet, age, size, gender, medical conditions, family history, climate and the like are provided.

Owner:ASHA NUTRITION SCI INC

Pattern searching methods and apparatuses

InactiveUS20080243841A1Avoid less flexibilityMore freedomDigital data information retrievalDigital data processing detailsStructure recognitionData mining

A computer-based method for identifying patterns in computer text using structures defining types of patterns which are to be identified, wherein a structure comprises one or more definition items, the method comprising assigning a weighting to each structure and each definition item; searching the computer text for a pattern to be identified on the basis of a particular structure, a pattern being provisionally identified if it matches the definition given by said particular structure; in a provisionally identified pattern, determining those of the definition items making up said particular structure that have been identified in the provisionally identified pattern; combining the weightings of the determined definition items and optionally, the weighting of the particular structure, to a single quantity; assessing whether the single quantity fulfils a given condition; depending on the result of said assessment, rejecting or confirming the provisionally identified pattern.

Owner:APPLE INC

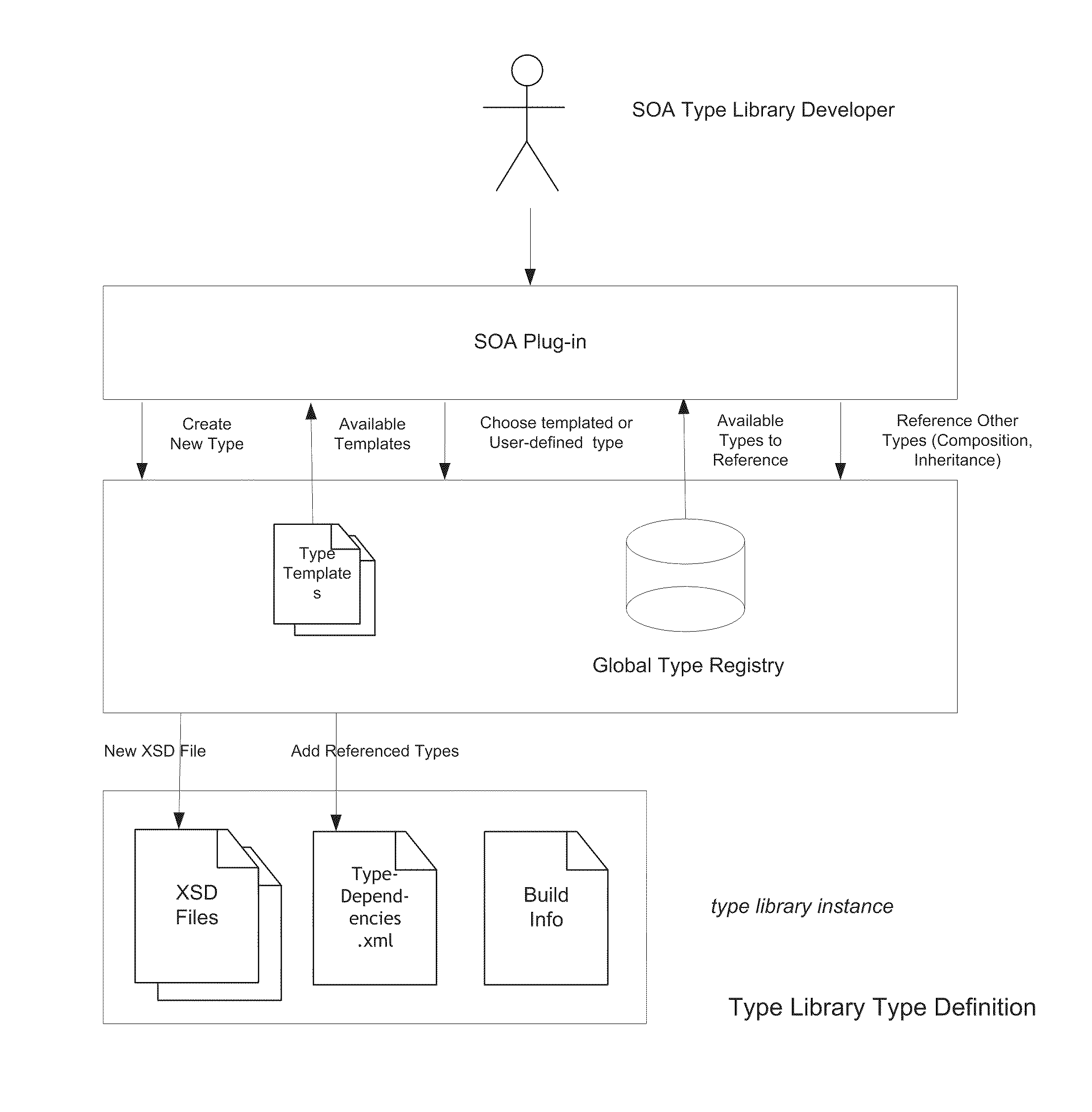

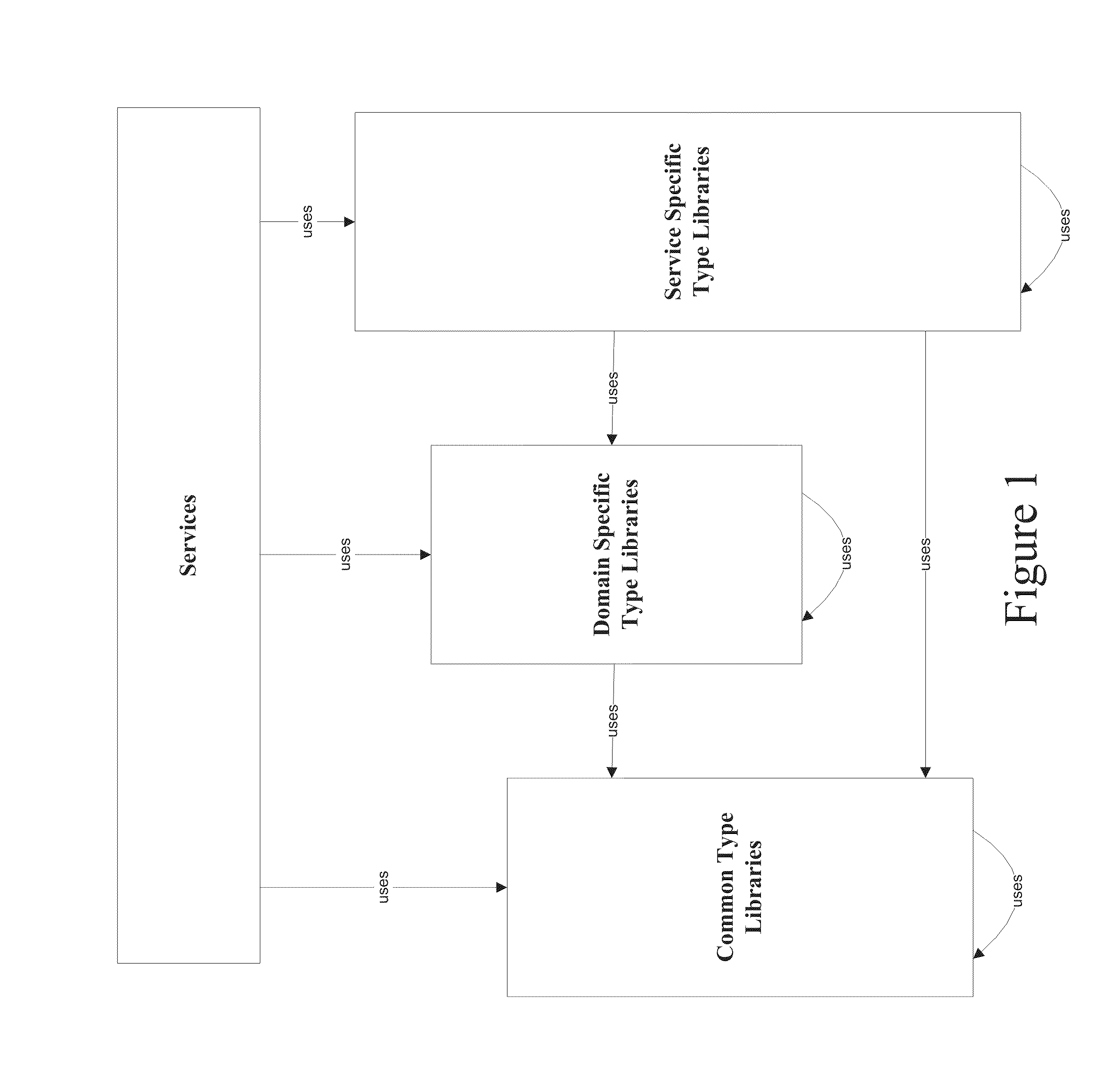

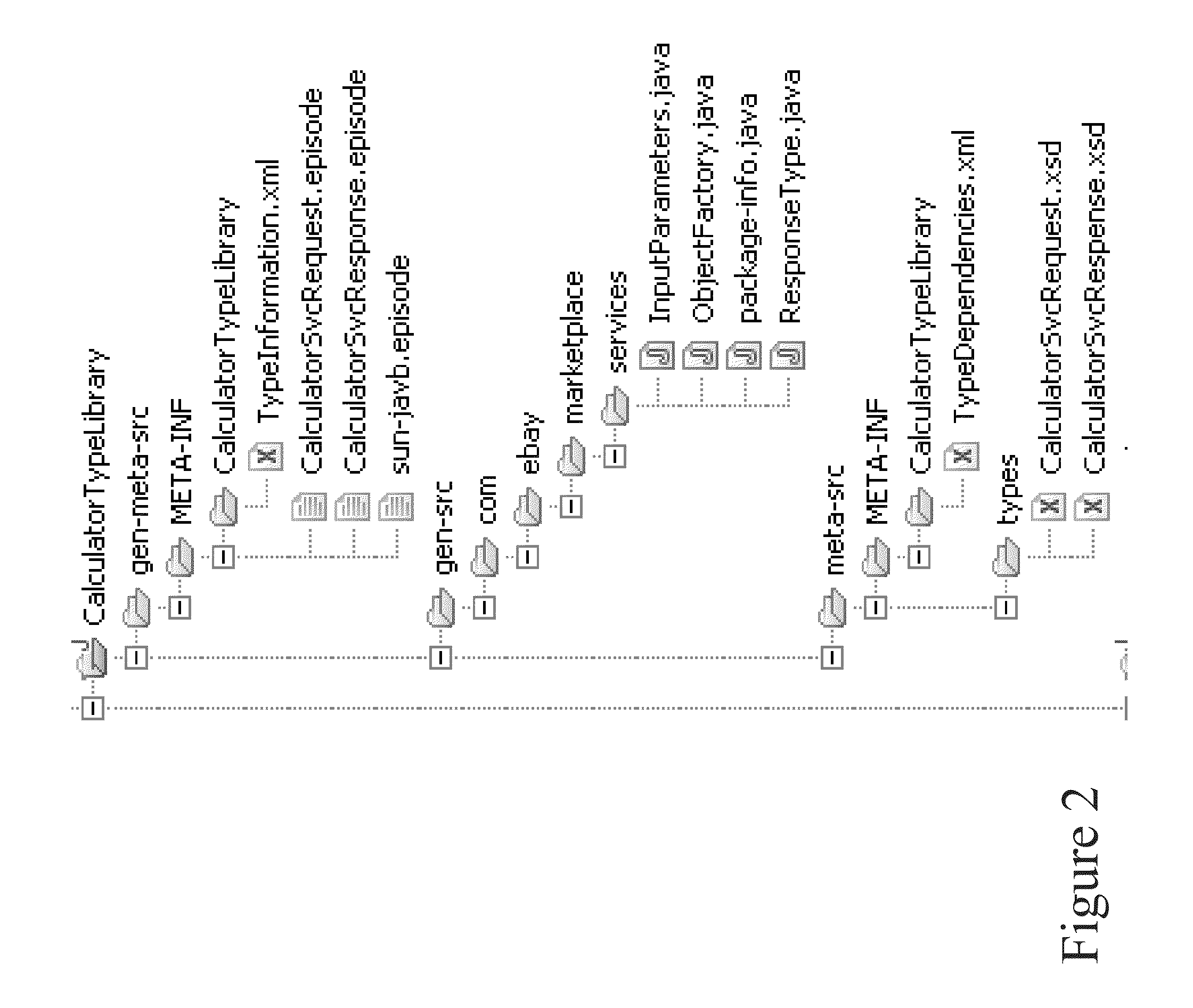

System and method for creating, managing, and reusing schema type definitions in services oriented architecture services, grouped in the form of libraries

ActiveUS20110184990A1Digital data processing detailsSoftware maintainance/managementProgramming languageDerivation Type

A computer-implemented system and method for creating, managing, and reusing schema type definitions in SOA services, grouped in the form of libraries are disclosed. The method in an example embodiment includes: grouping a plurality of Extensible Mark-up Language (XML) schema (XSD) types, each XSD type defined in an individual XSD file; using a processor to bundle the plurality of individual XSD types into a type library, the type library including a type information file to register the individual XSD types in the type library, the type library further including a type dependencies file to register dependencies between the individual XSD types in the same or different type library; importing types from a different type library, when defining derived types or aggregated types; generating Java artifacts from the XSD types; and associating the Java artifacts with corresponding XSD types in the type information file of the type library.

Owner:PAYPAL INC

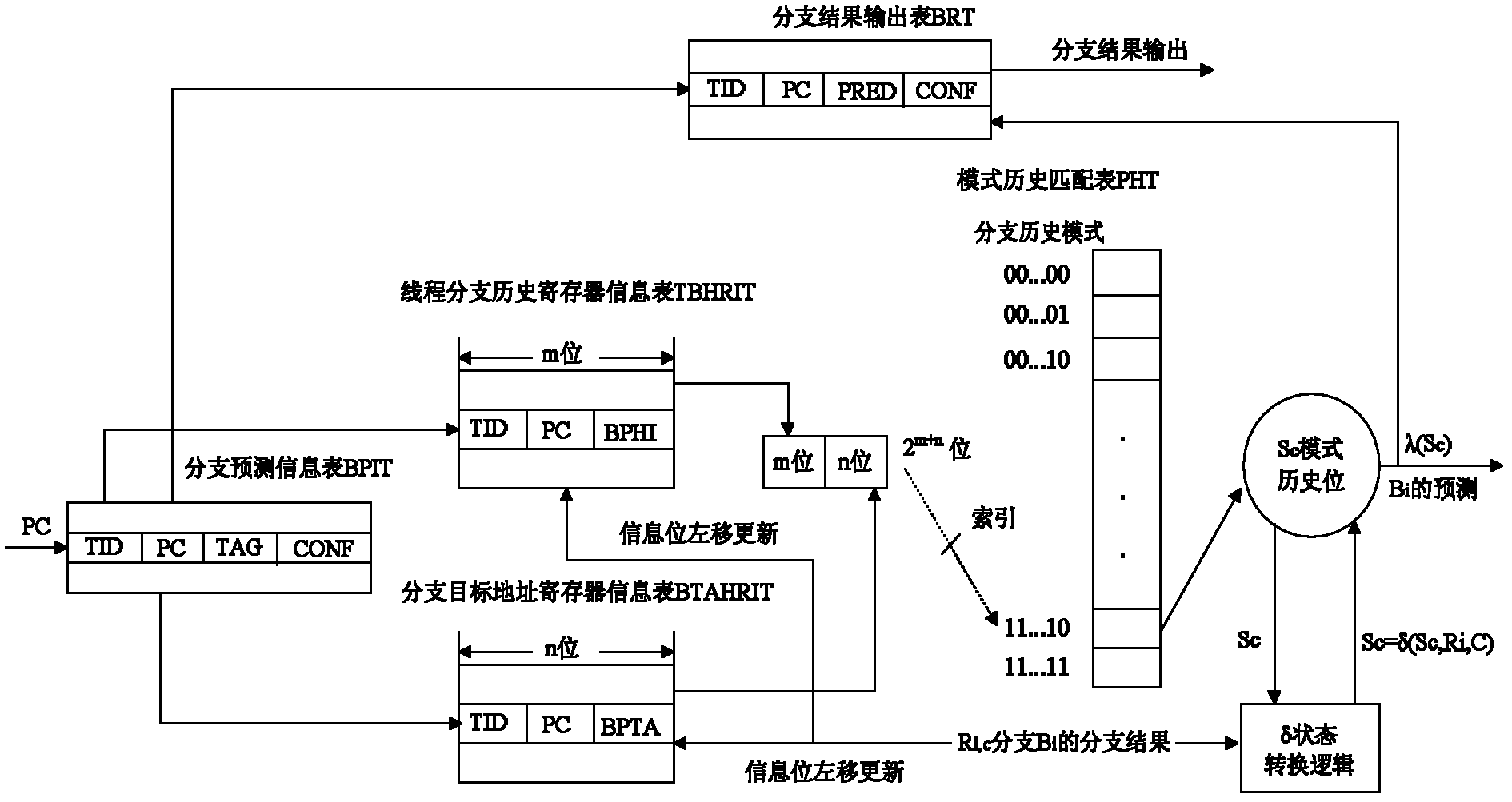

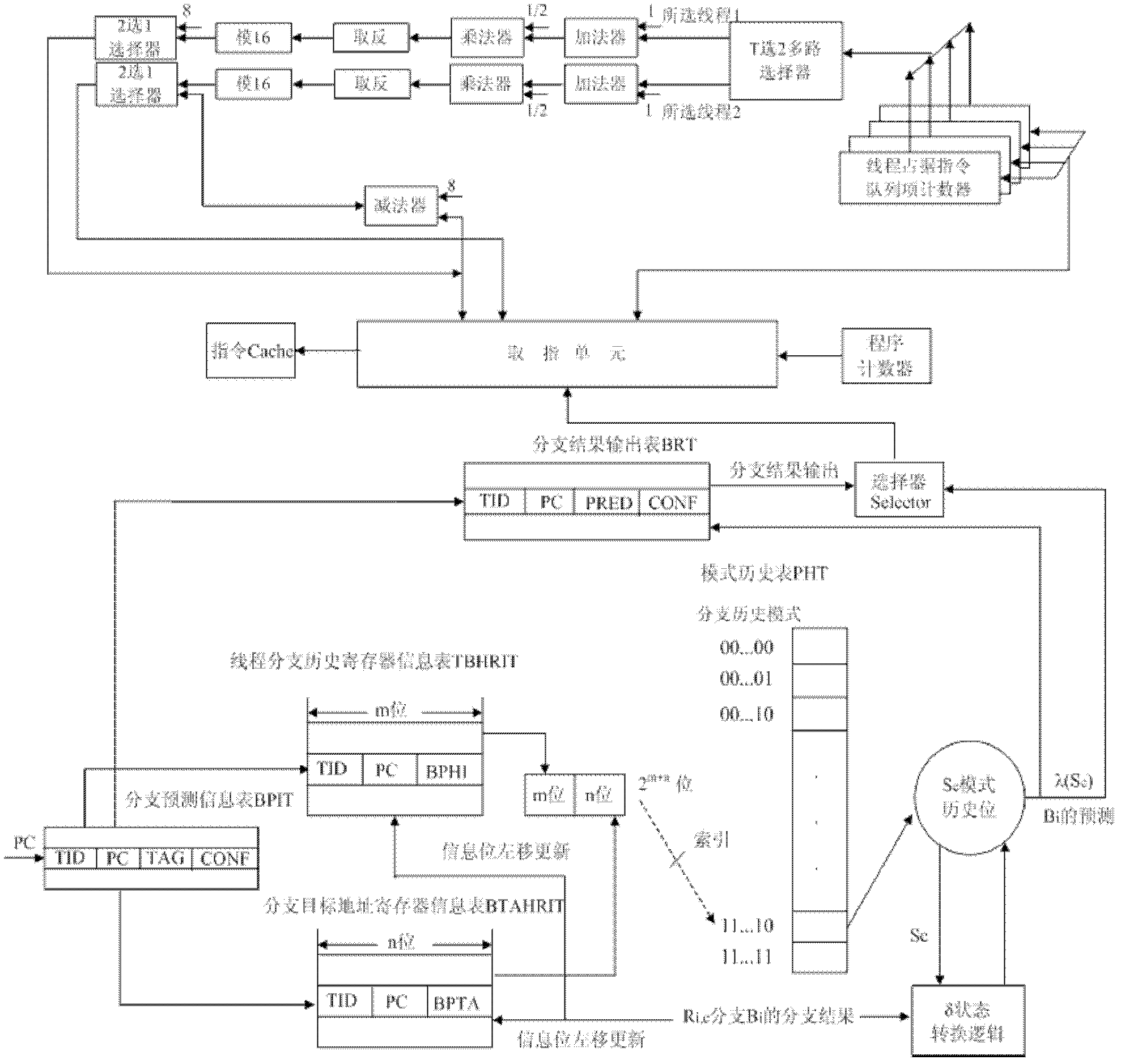

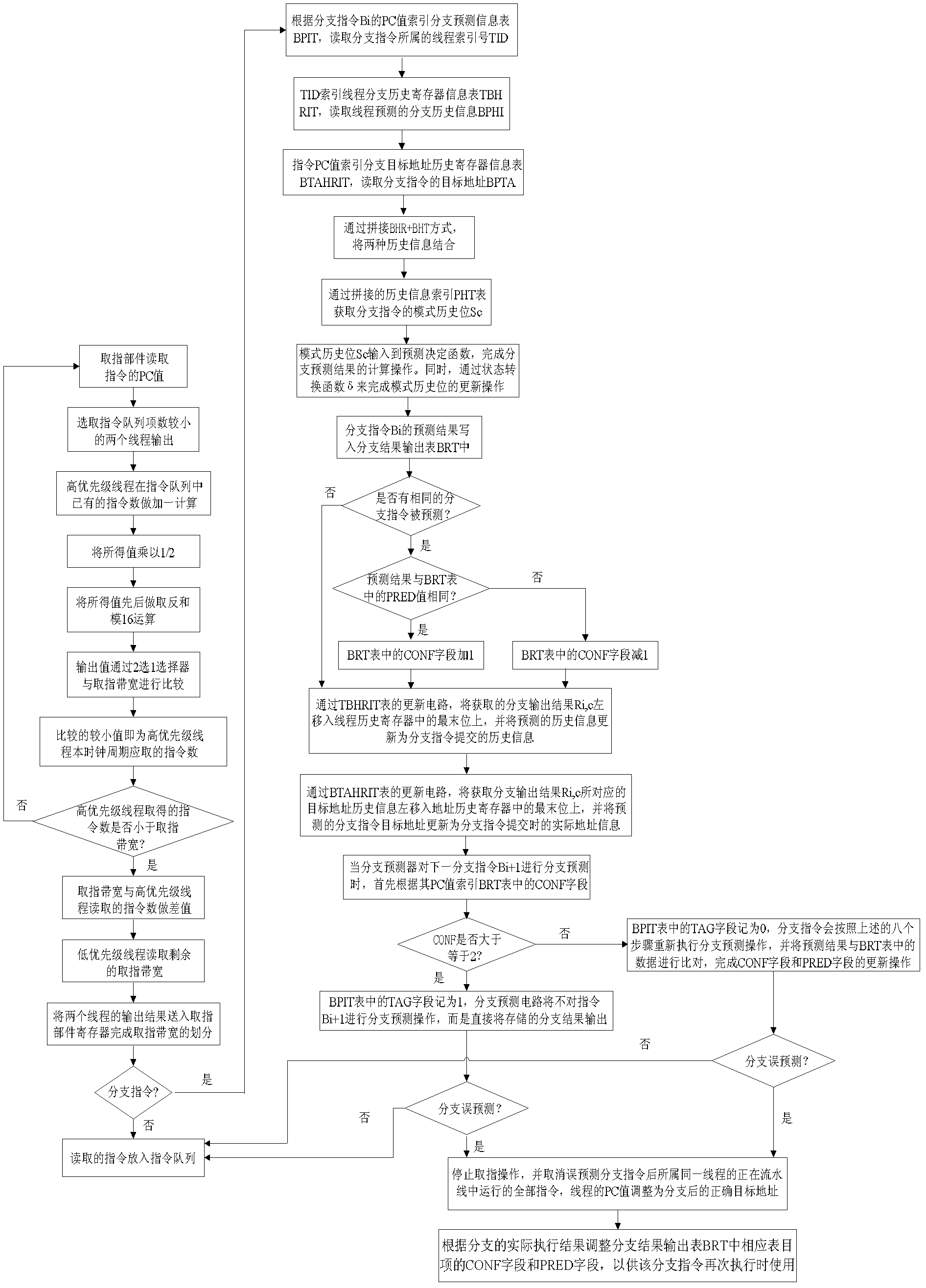

Instruction acquisition control method based on simultaneous multithreading

InactiveCN102566974AImprove superiorityAdvancing Predictive Execution SpeedConcurrent instruction executionMemory systemsFailure ratePattern matching

The invention provides an instruction acquisition control method based on simultaneous multithreading, which includes the steps: in each clock cycle of a processor, reading a PC (personable computer) value of instructions by an instruction acquisition component according to a program counter, selecting two threads with high priority as instruction acquisition threads firstly, and then computing the actual instruction number required by each instruction acquisition thread so as to read the instructions; according to an IPC (inter-process communication) value and the Cache failure rate, enabling a dual-priority resource allocation mechanism to compute system resources required by the threads in an instruction acquisition stage and complete dynamic allocation of the resources; matching a TBHBP (thread branch history branch predictor) with the instruction acquisition operations of the instruction acquisition component, acquiring a pattern type match position Sc by connecting global historical information with local historical information read by a branch instruction Bi to utilize as an index of a secondary PHT (pattern history table), and inputting computed results to a BRT (branch result table); and when the branch instruction Bi is executed again, judging whether CONF fields are larger than or equal to 2 or not by the aid of a selector, directly outputting the recorded branch results if the CONF fields are larger than or equal to 2, and finally placing the acquired instruction into an instruction Cache, so that all operations of instruction acquisition control are completed.

Owner:HARBIN ENG UNIV

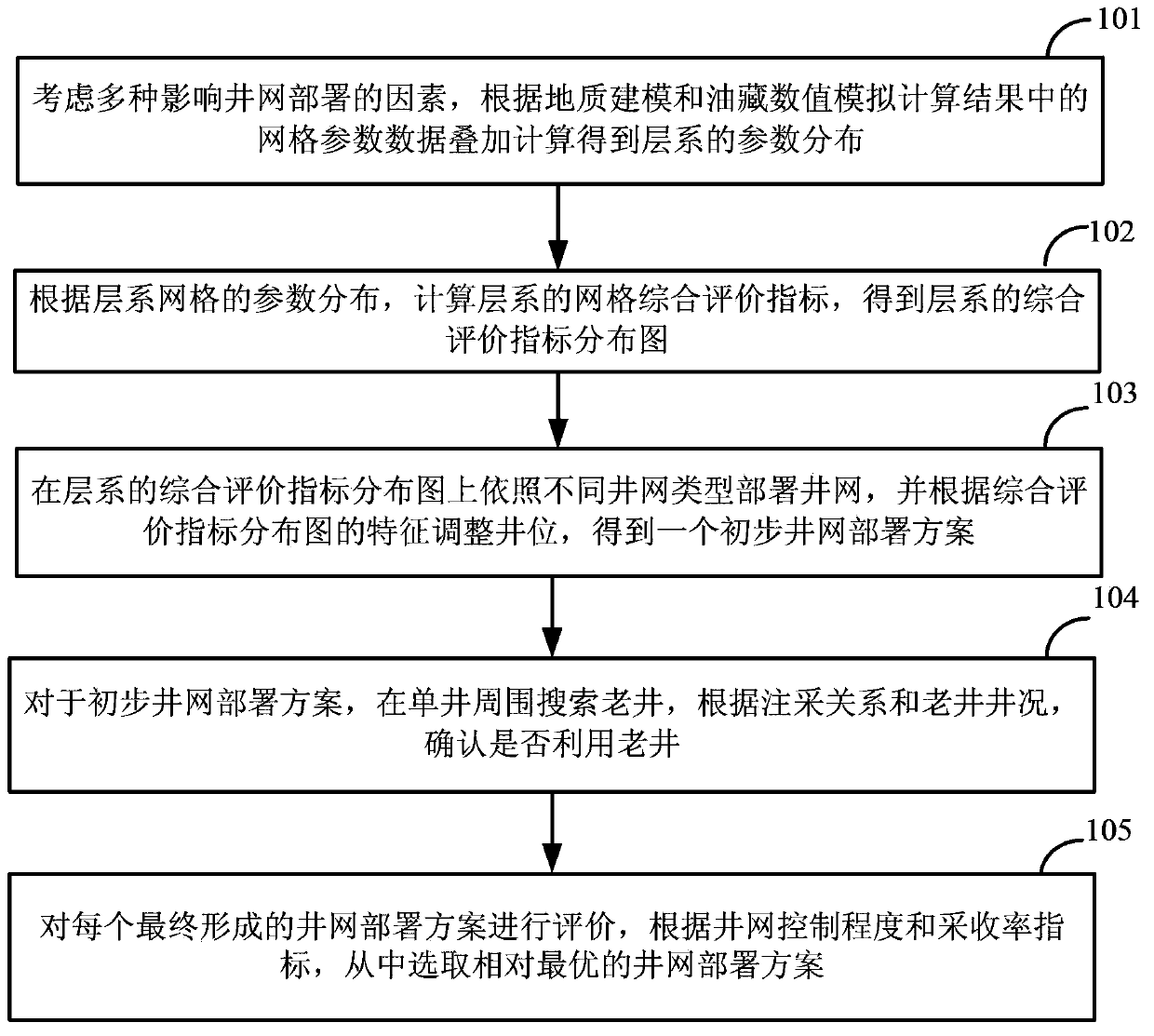

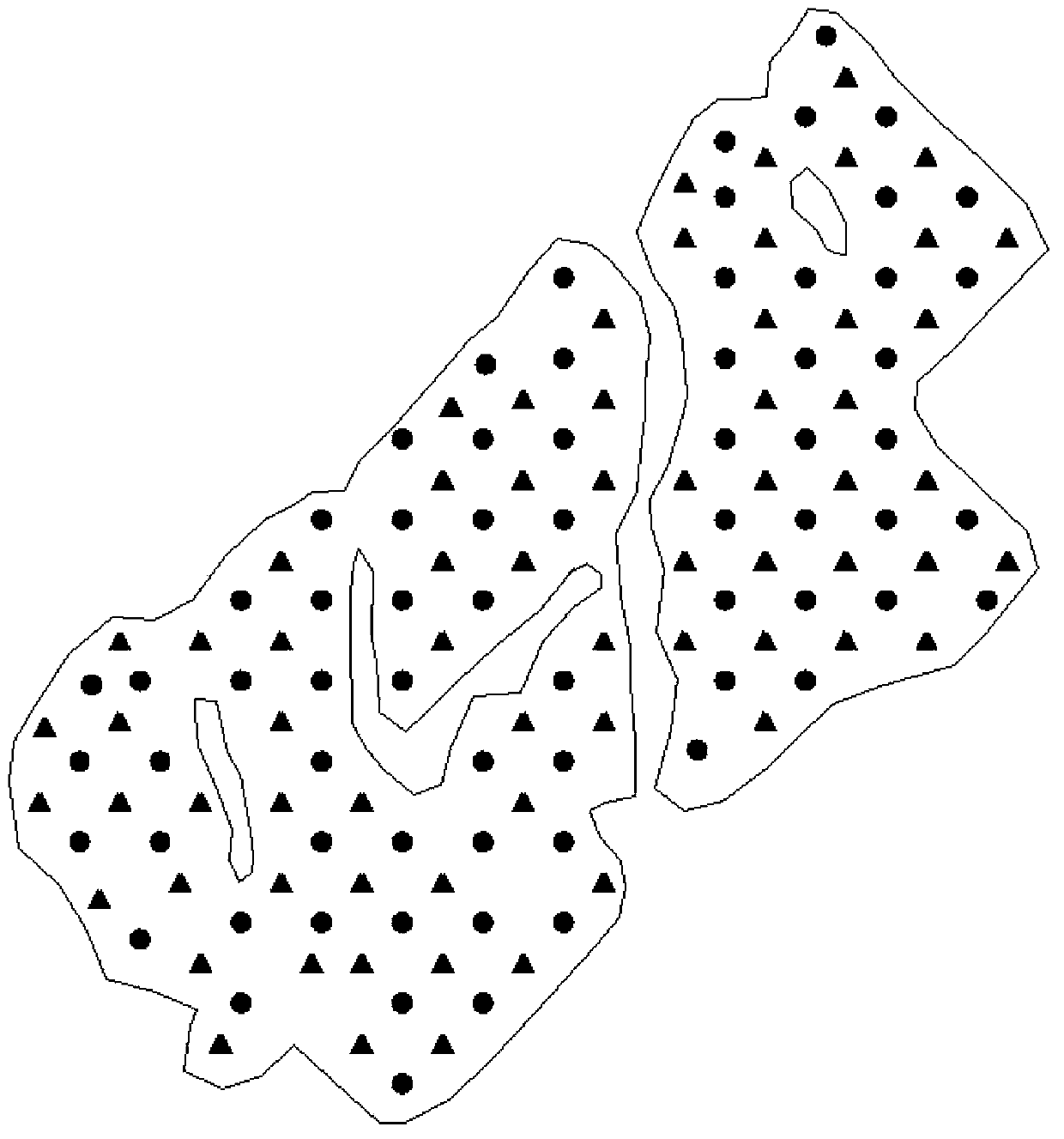

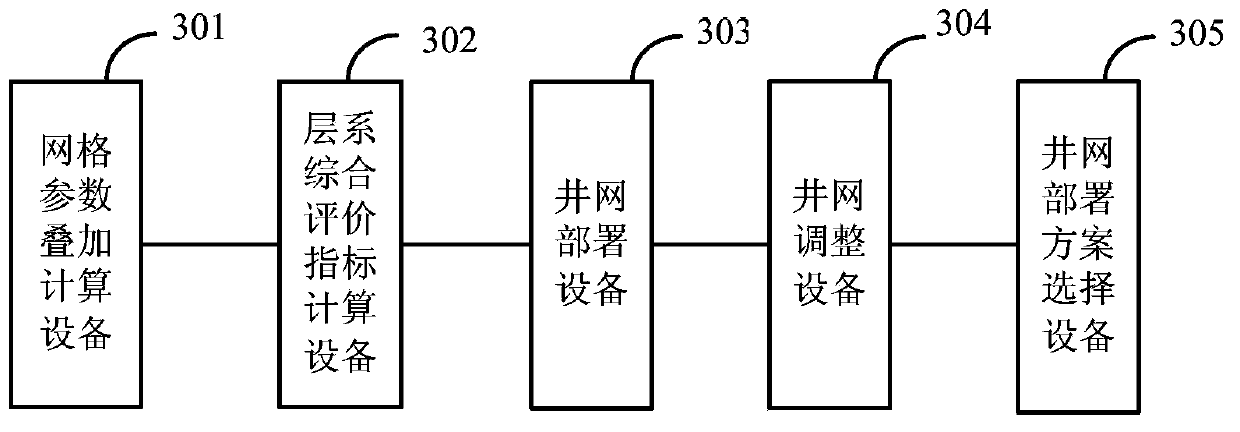

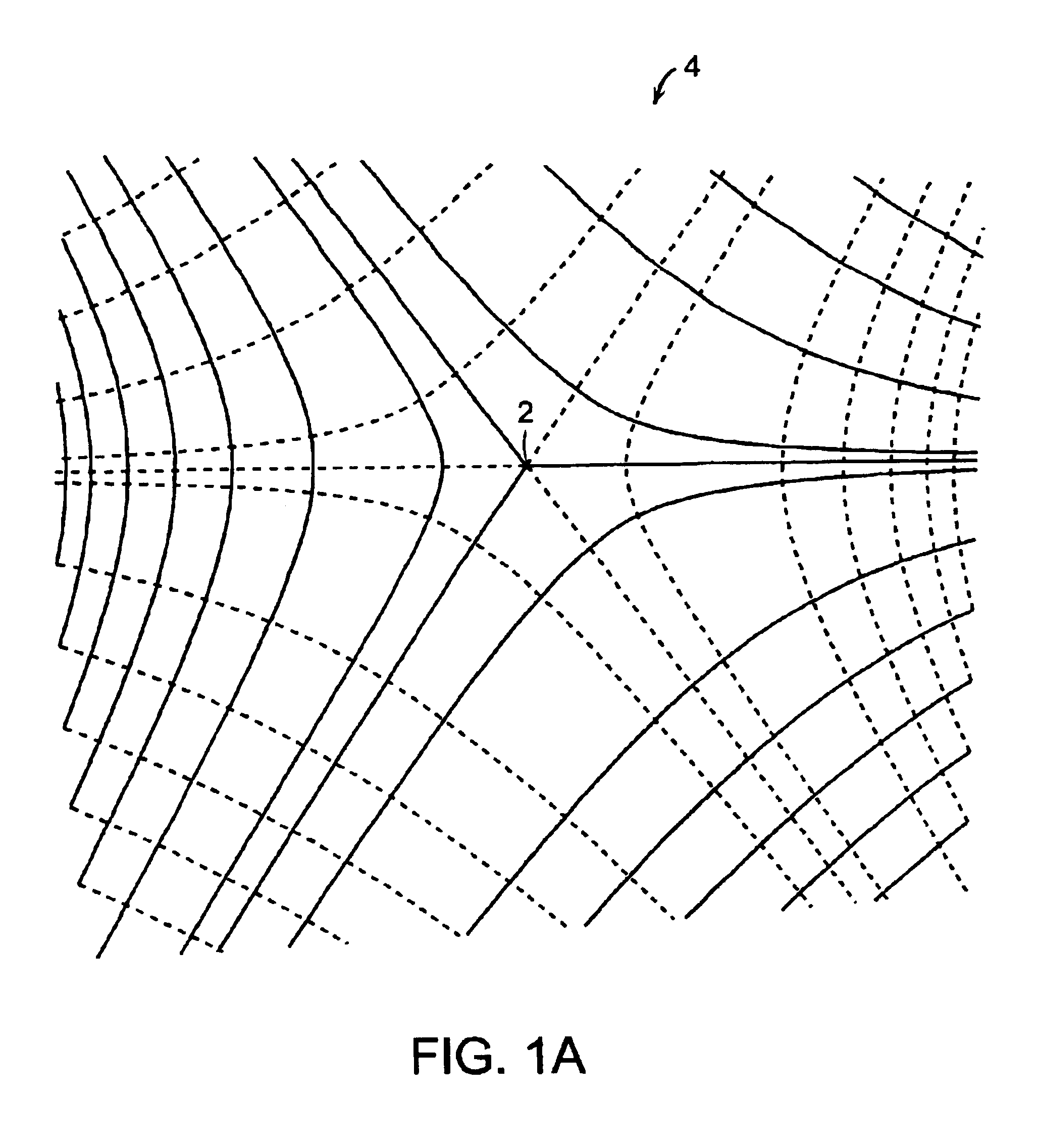

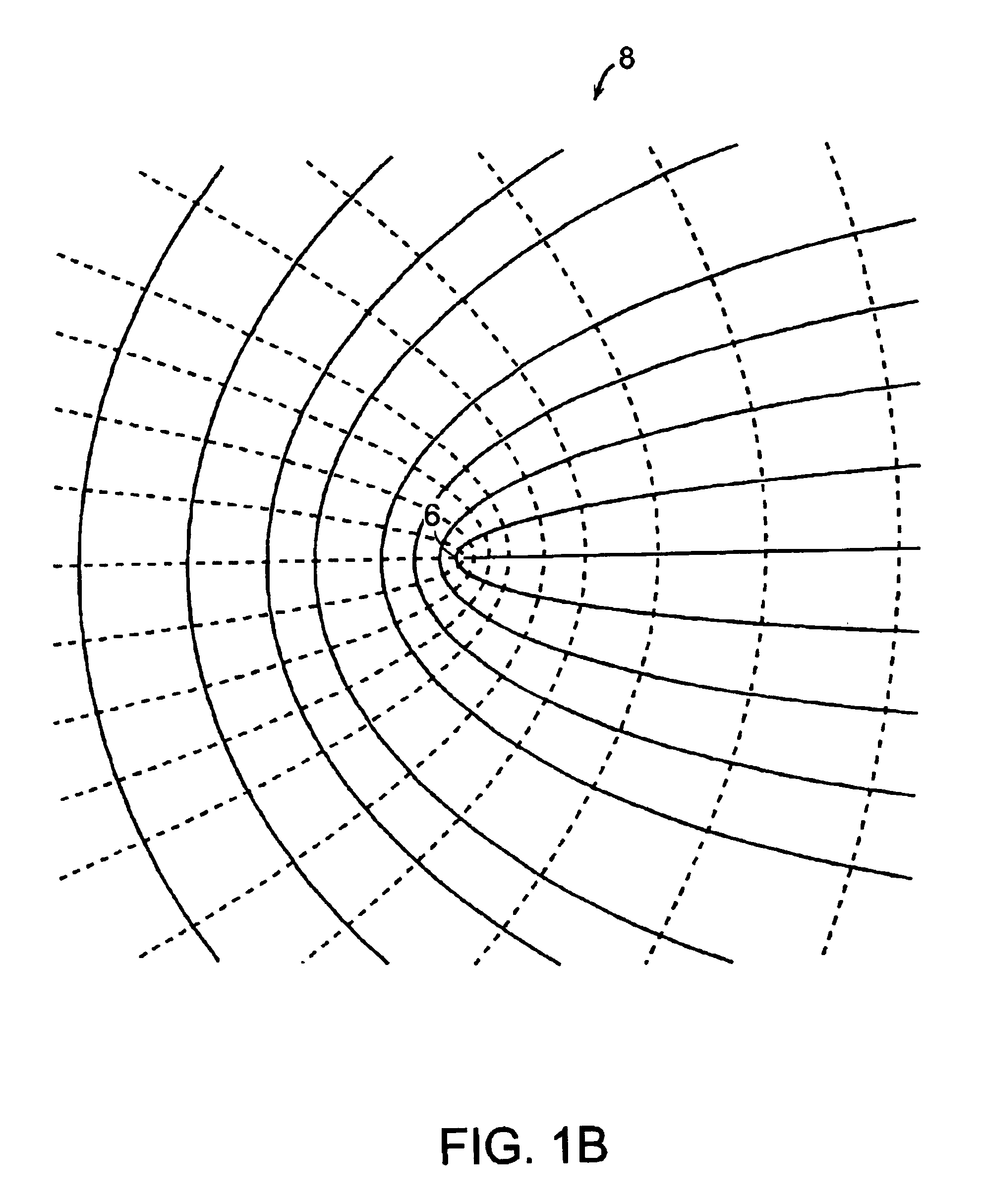

Well pattern rebuilding method and device for water-injection development of old oil field

The invention discloses a well pattern rebuilding method and device for the water-injection development of an old oil field. The method comprises the steps that various factors for influencing well pattern arrangement are taken into account, and mesh parameter data in geologic modeling and numerical reservoir simulation computed results are stacked and computed to obtain parameter distribution of series of strata; the mesh comprehensive evaluation index of the series of strata is computed, and a comprehensive evaluation index distribution diagram of the series of strata is obtained; well patterns are arranged on the comprehensive evaluation index distribution diagram of the series of strata according to different well pattern types, well positions are adjusted according to the characteristics of the comprehensive evaluation index distribution diagram, and initial well pattern arrangement schemes are obtained; for each initial well pattern arrangement scheme, old wells are searched for around the signal wells, and whether the oil wells are utilized is determined according to well conditions and an injection-production relationship; each well pattern arrangement scheme formed finally is evaluated, and the relatively-optimal well pattern arrangement scheme is selected according to the well pattern control degree and a recovery efficiency index. The well pattern rebuilding method and device for the water-injection development of the old oil field can meet the well pattern arrangement requirements of old oil fields in the secondary development process.

Owner:PETROCHINA CO LTD

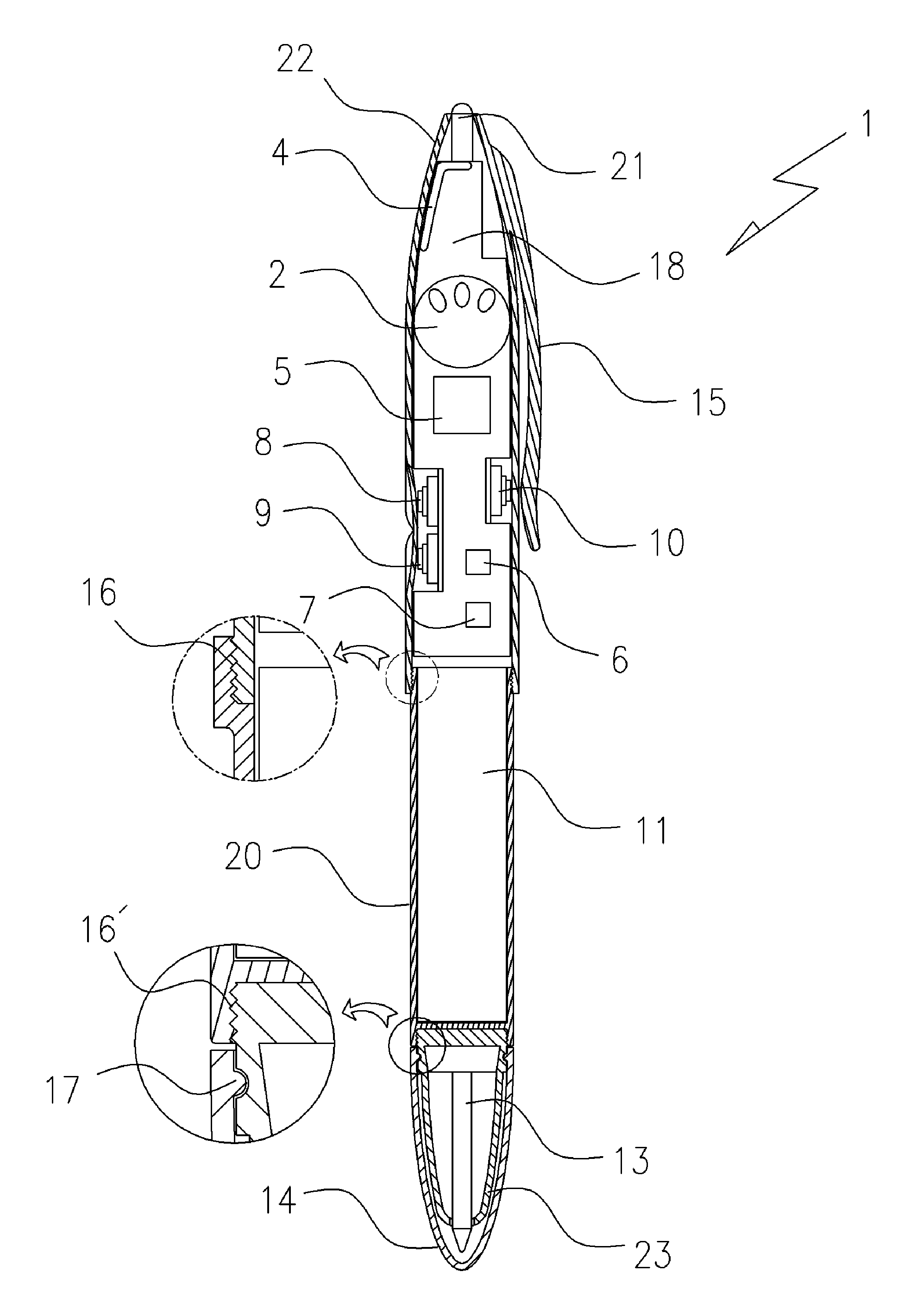

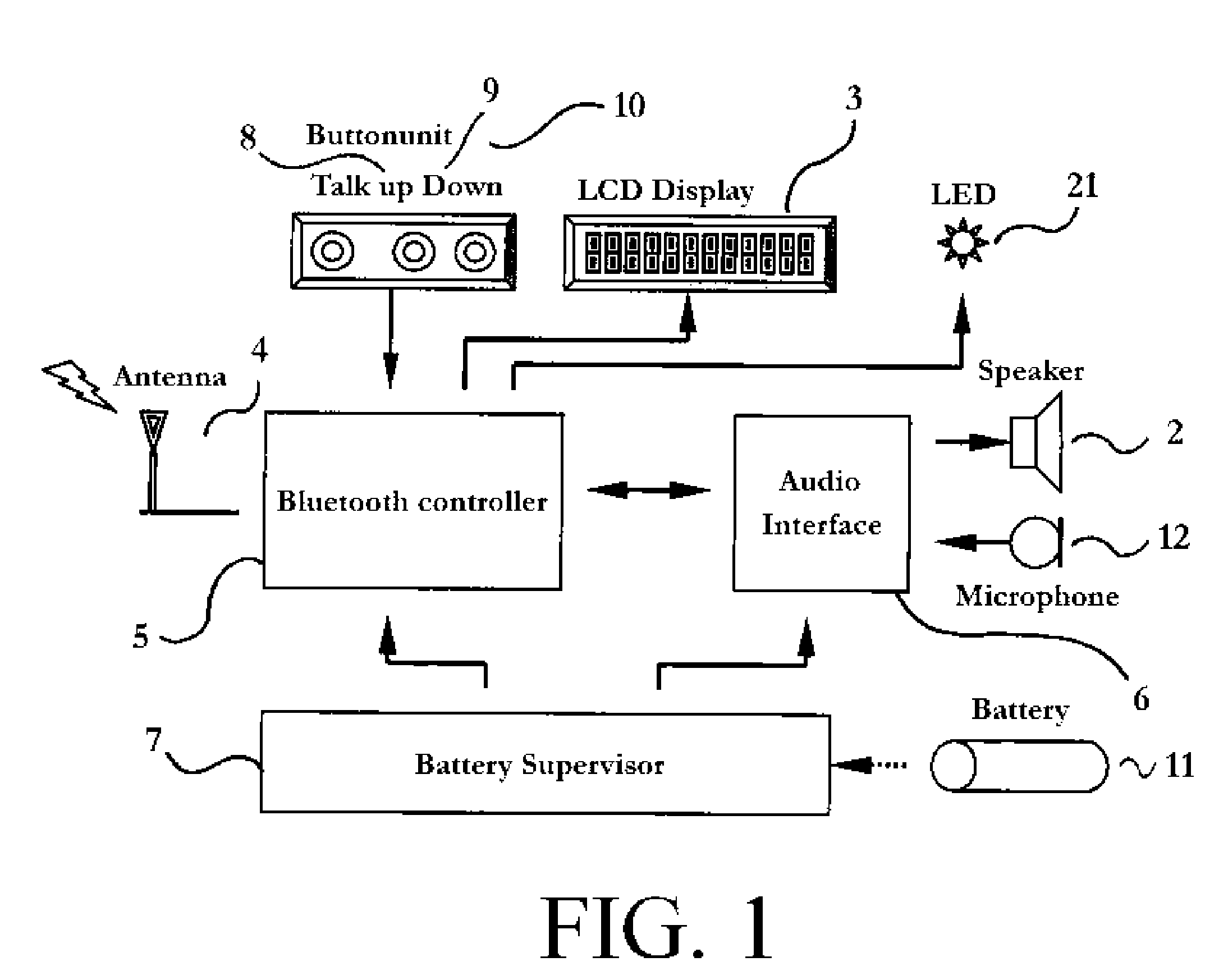

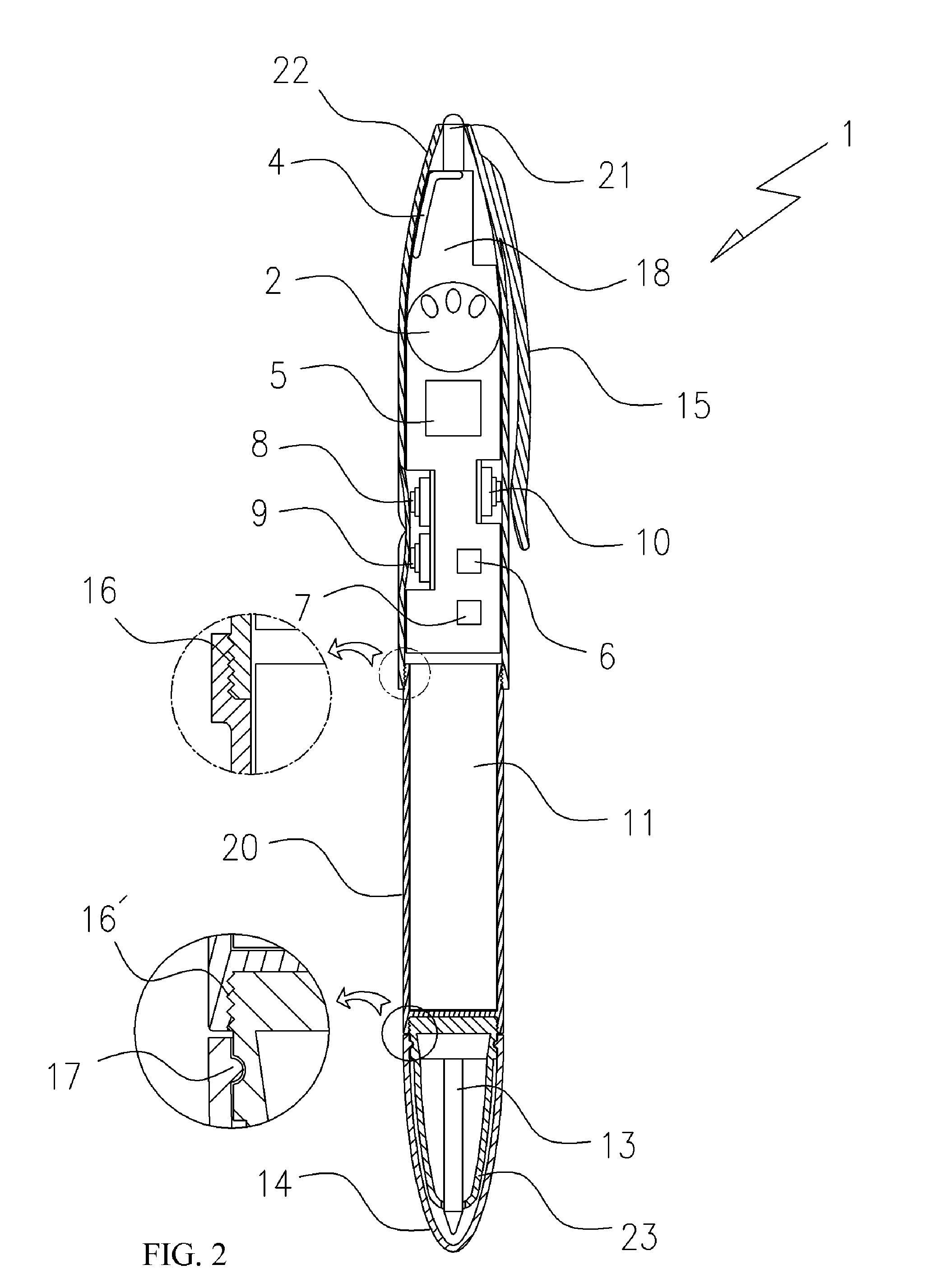

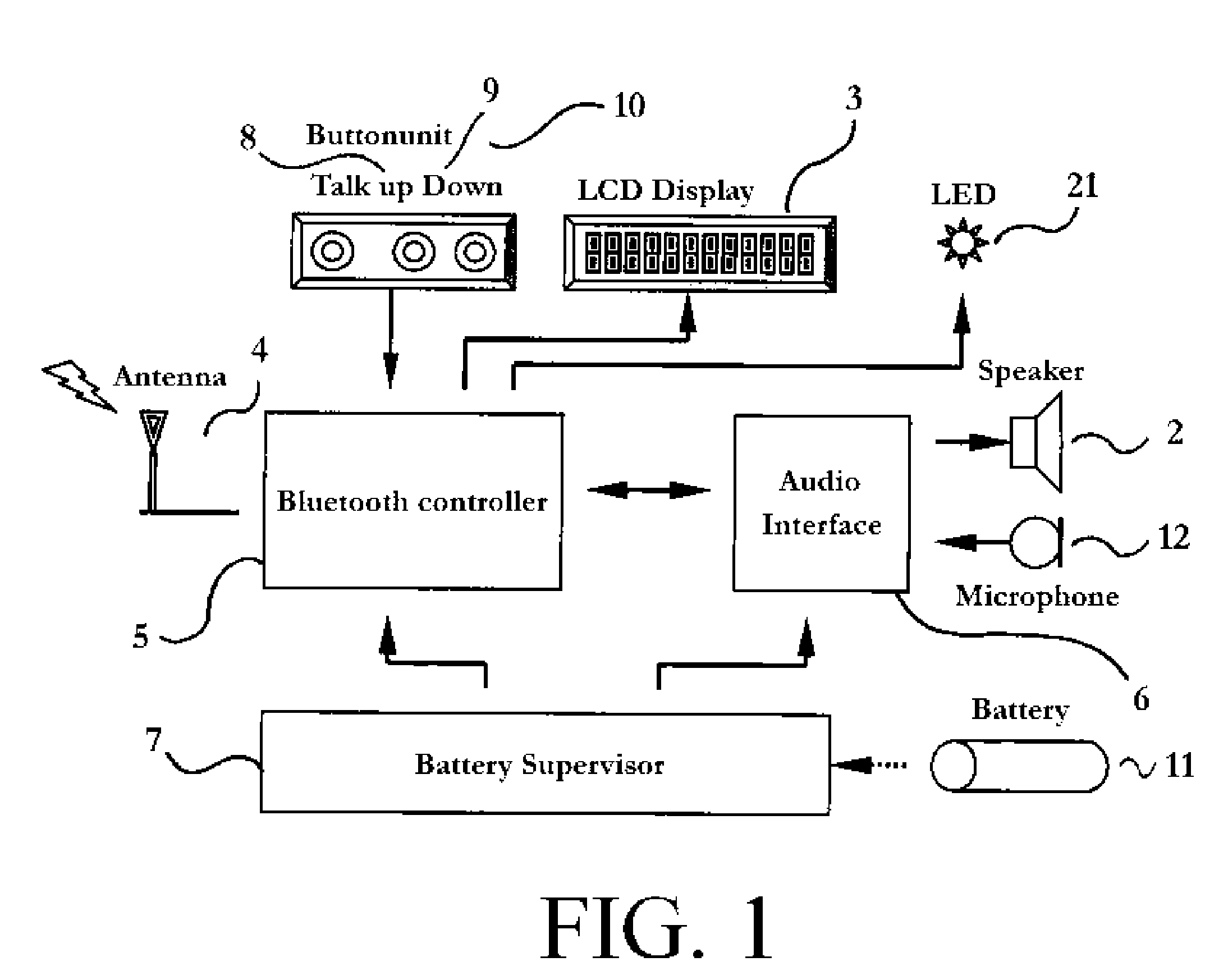

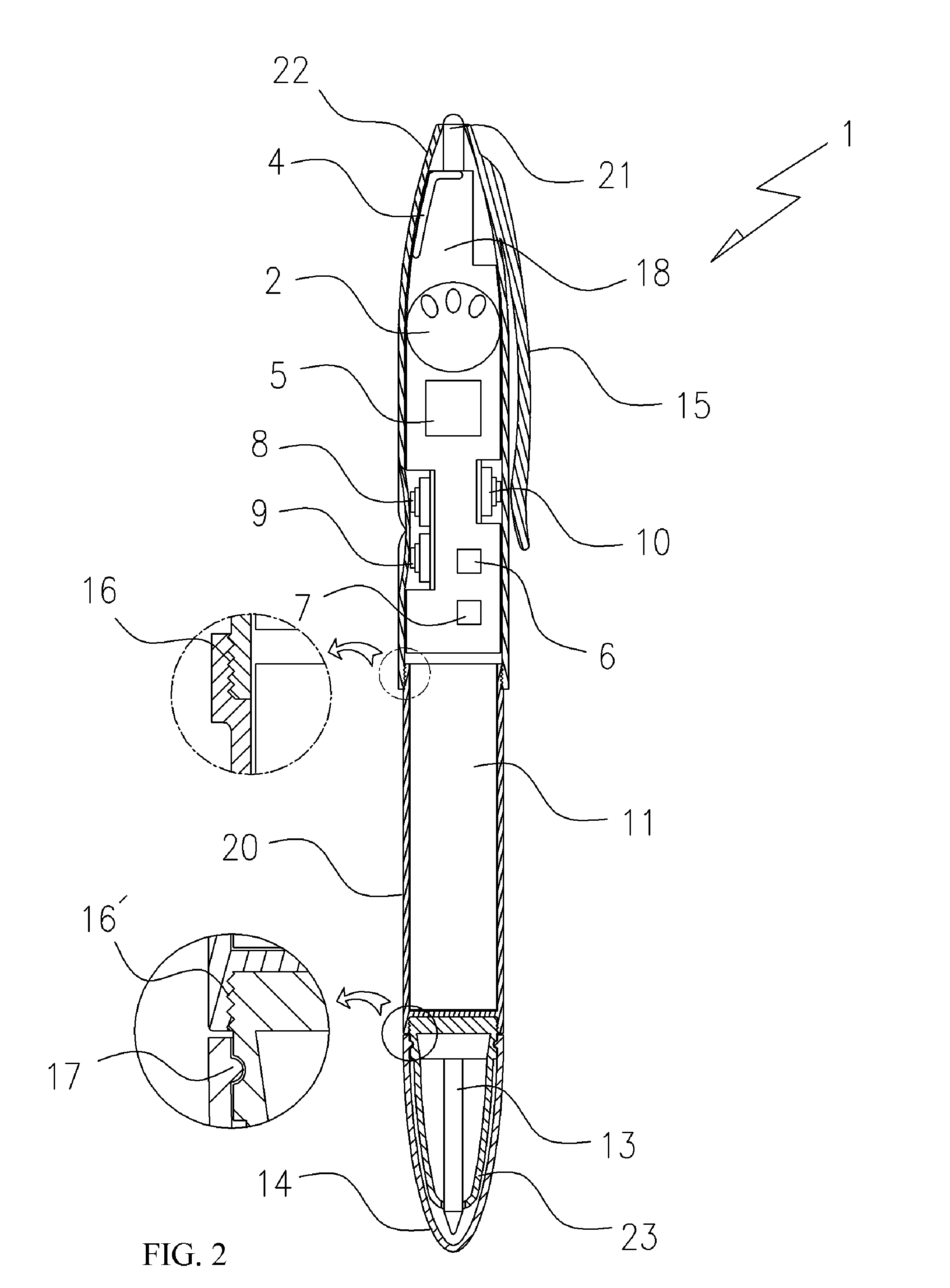

Pen-type wireless transceiver for mobile communication terminal using bluetooth

InactiveUS20060046650A1Low powerEasy to carryDevices with bluetooth interfacesRadio transmissionKey pressingWireless transceiver

Disclosed herein is a pen-type wireless transceiver for a mobile communication terminal using Bluetooth. The pen-type wireless transceiver includes a pen type body, an LED, a pattern type antenna, a speaker, an LCD display, a button unit, a battery, a microphone, a Bluetooth controller, an audio interface, a main board, a battery supervisor, a replaceable ballpoint ink container, a locking projection, threaded parts, a pen clip and a guard pad.

Owner:KOHLI PARAMJIT +1

Pen-type wireless transceiver for mobile communication terminal using bluetooth

InactiveUS7231181B2Low powerEasy to carryDevices with bluetooth interfacesRadio transmissionWireless transceiverEngineering

Disclosed herein is a pen-type wireless transceiver for a mobile communication terminal using Bluetooth. The pen-type wireless transceiver includes a pen type body, an LED, a pattern type antenna, a speaker, an LCD display, a button unit, a battery, a microphone, a Bluetooth controller, an audio interface, a main board, a battery supervisor, a replaceable ballpoint ink container, a locking projection, threaded parts, a pen clip and a guard pad.

Owner:KOHLI PARAMJIT +1

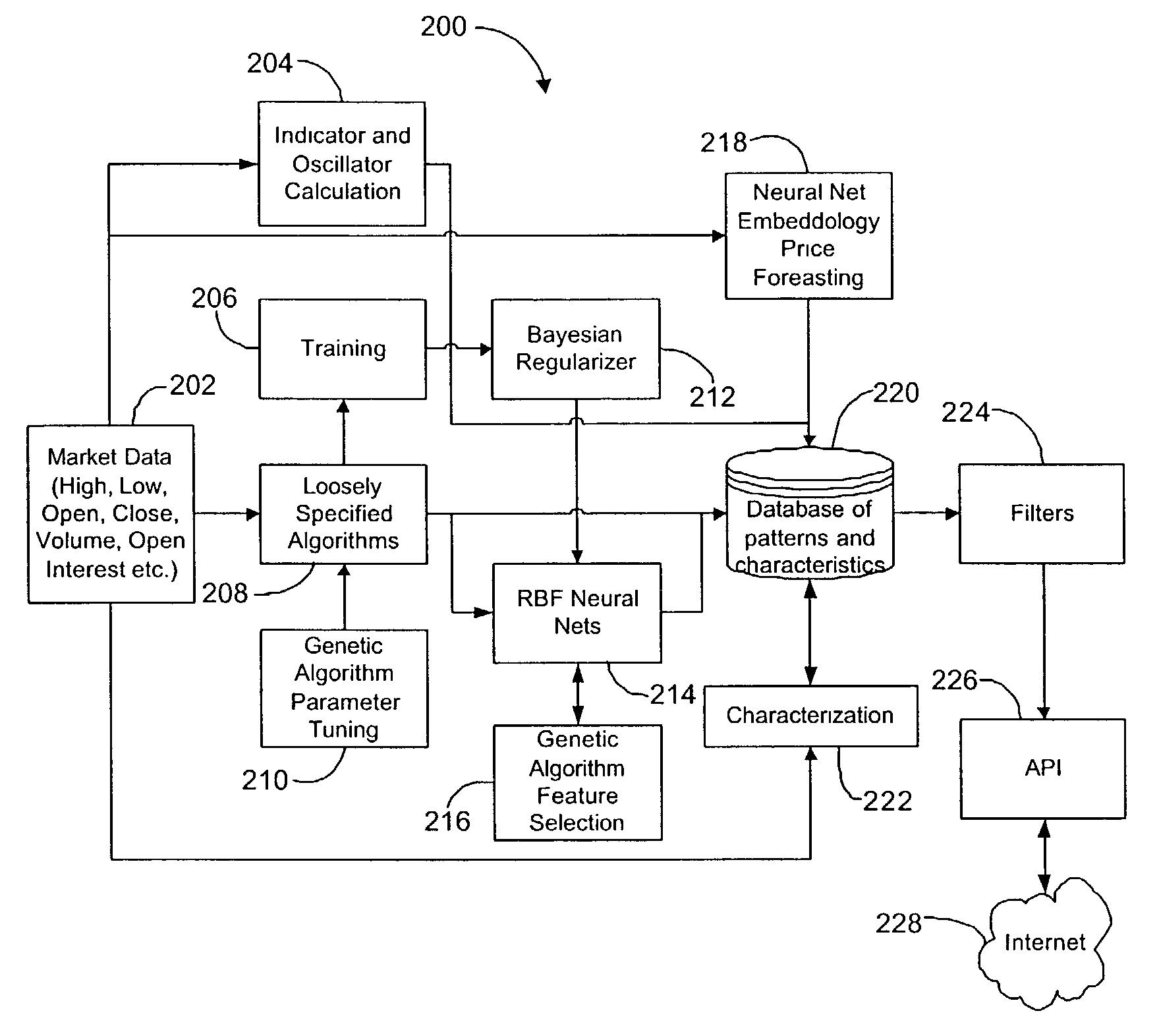

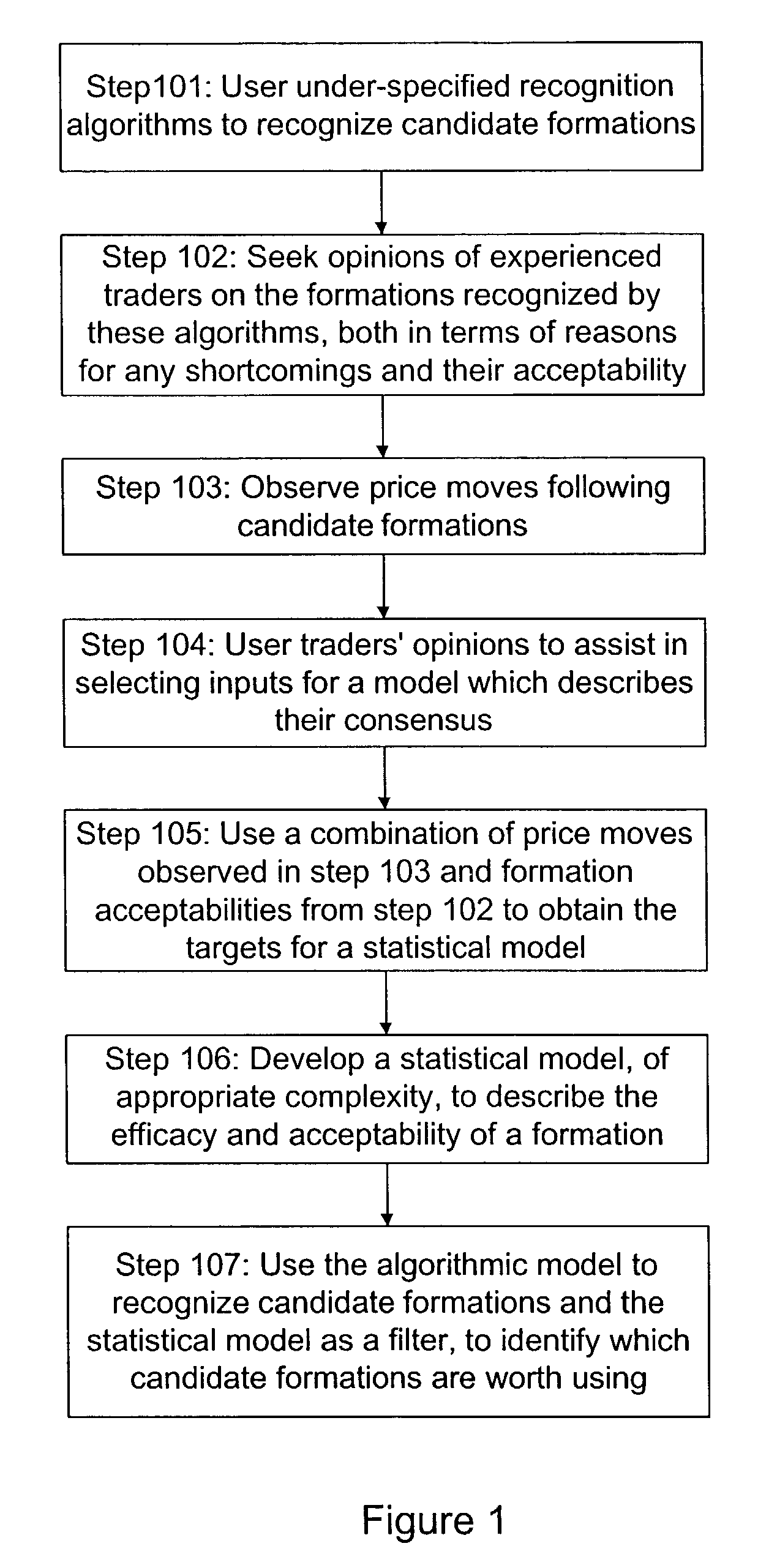

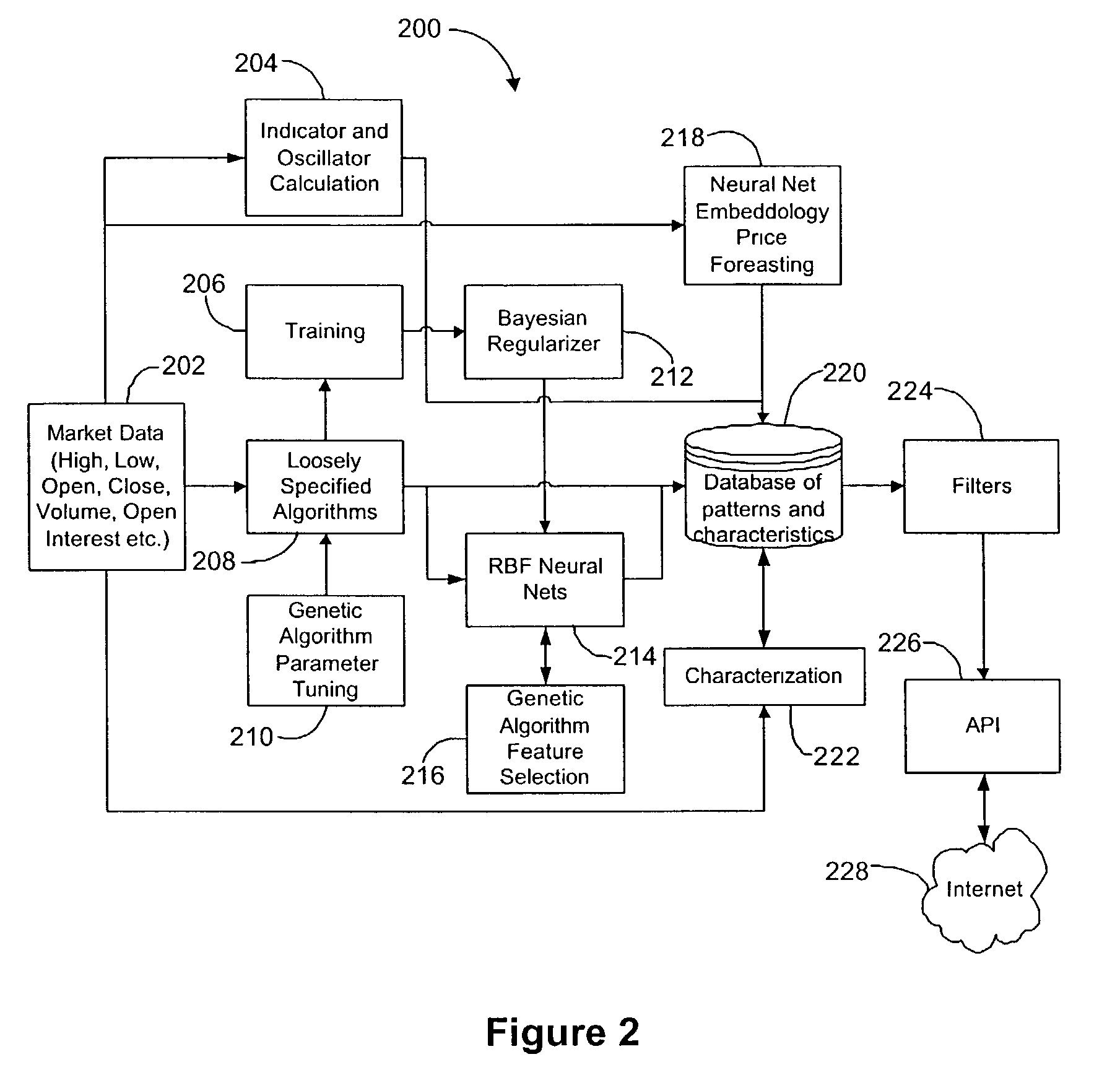

Method of rule constrained statistical price formation recognition

A method of developing a rule-constrained statistical pattern recognizer applicable to price formation recognition includes assembling input data containing examples of patterns to be recognized and establishing mandatory recognition rules. The recognition rules are programmed to construct an underspecified or underconstrained recognition model which is applied to the assembled data to produce candidate patterns. The candidate patterns are reviewed and identified as valid or invalid and for each pattern type a residual statistical model is produced based on the candidate patterns identified as valid. A filter is used to ensure that custom conditions such as duration relationships, height relationships and volume requirements are met.

Owner:TRADING CENT CANADA INC

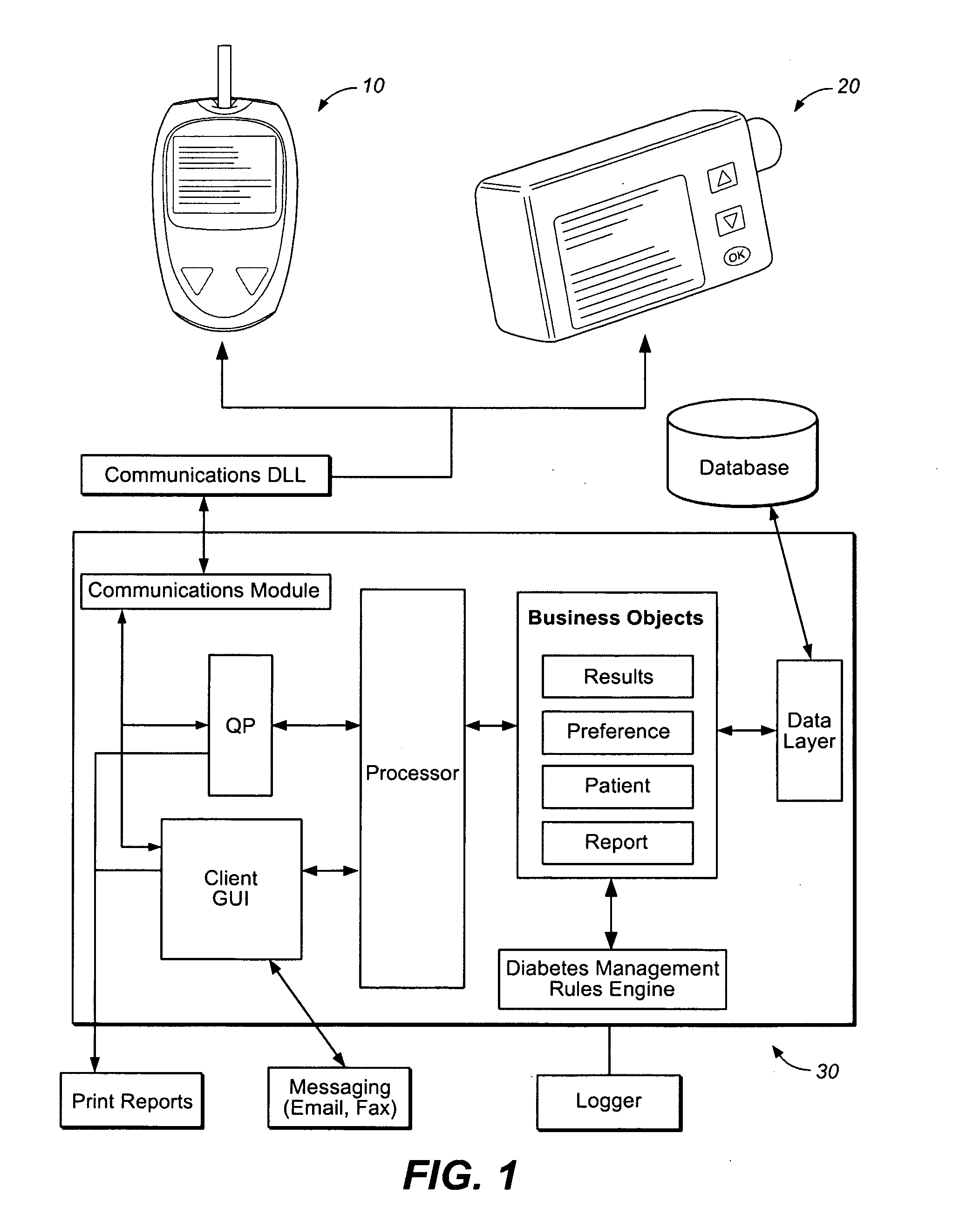

Computer system for diabetes management

A diabetes management system or process is provided herein that may be used to analyze and recognize patterns for a large amount of blood glucose concentration measurements and other physiological parameters related to the glycemia of a patient. In particular, a method of monitoring glycemia in a patient may include storing a patient's data on a suitable device, such as, for example, a glucose meter. The patient's data may include blood glucose concentration measurements. The diabetes management system or process may be installed on, but is not limited to, a personal computer, an insulin pen, an insulin pump, or a glucose meter. The diabetes management system or process may identify a plurality of pattern types from the data including a testing / dosing pattern, a hypoglycemic pattern, a hyperglycemic pattern, a variability pattern, and a comparative pattern. After identifying a particular pattern with the data management system or process, a warning message may be displayed on a screen of a personal computer or a glucose meter. Other messages can also be provided to ensure compliance of any prescribed diabetes regiments or to guide the patient in managing the patient's diabetes.

Owner:LIFESCAN INC

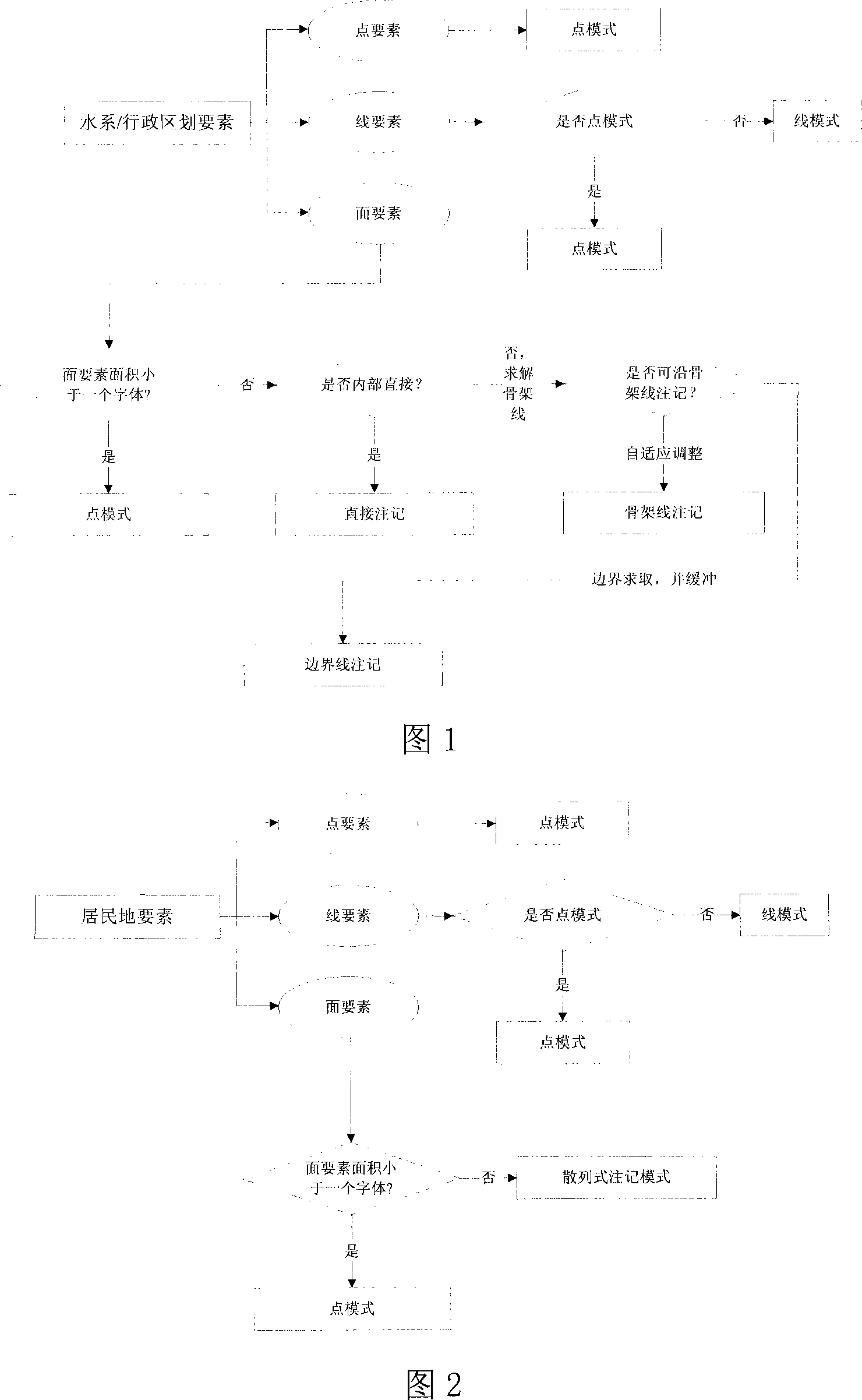

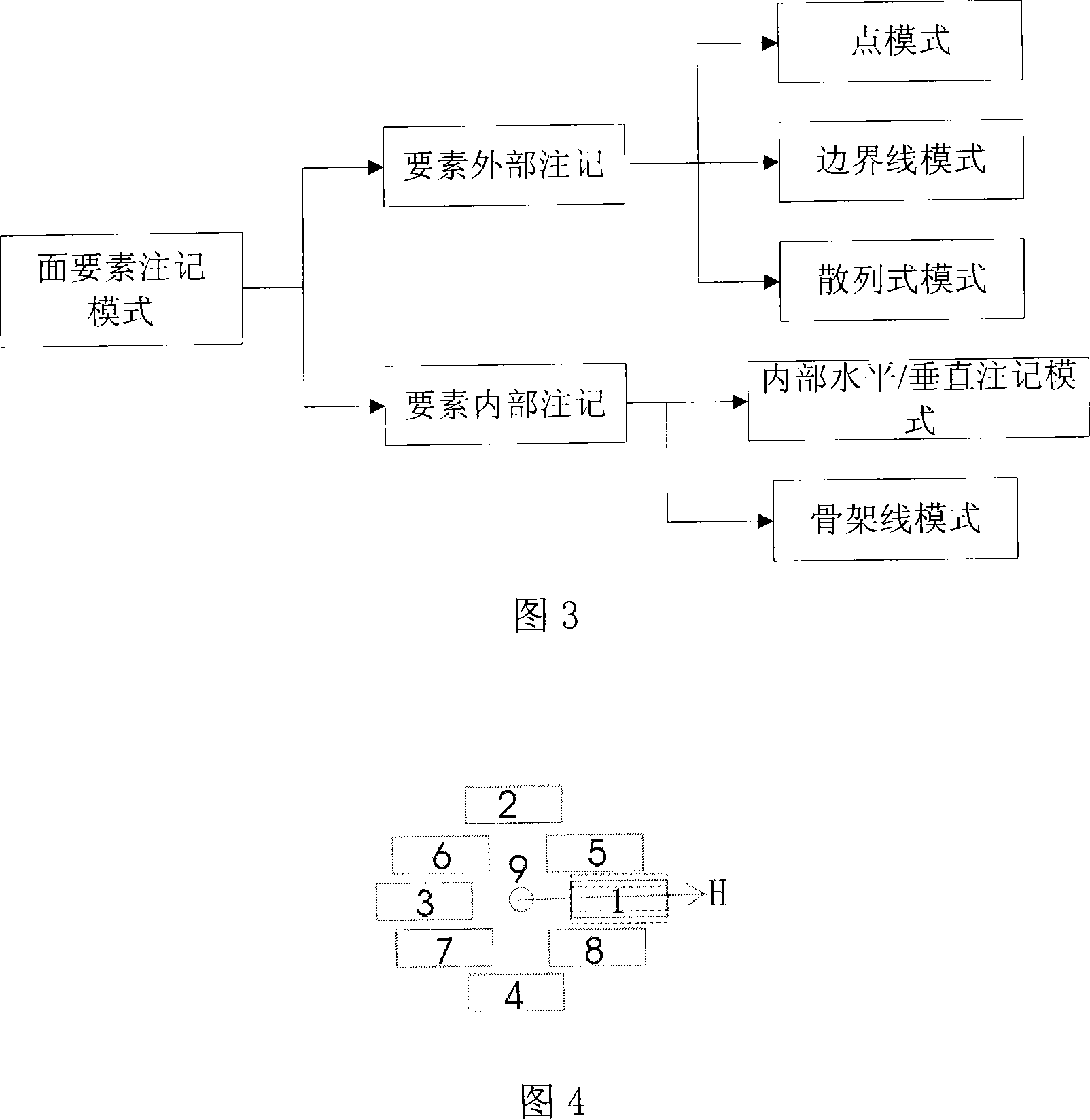

Face-shaped element configuring method in computer graphics

InactiveCN101183461AImprove the efficiency of automatic annotationSolve the problem of intelligent configurationMaps/plans/chartsSpecial data processing applicationsComputerized systemTopographic map

The invention relates to a configuration method for area pattern in computer drawing, belonging to the technical field of computer drawing, which comprises the following steps: step one, importing the geography data into the computer and then judging the pattern type waiting for noting in the geography data; step two, deciding the noting mode type of the noting pattern according to the pattern type; step three, configuring the pattern waiting for noting according to the configuration rule of the noting mode type. The invention divides the noting configuration of the area pattern into five basic modes according to the substantive characteristics and the configuration rules of the patterns of the water system and settlement place, provides the automatic configuration arithmetic of noting of different modes according to the geometrical characteristics of the modes, and resolves the problems of collision or shelter of the different noting modes in topographic maps with full elements. The invention has the advantages of improved efficiency of automatically noting the area pattern and enhanced noting quality of the map.

Owner:常熟紫金知识产权服务有限公司

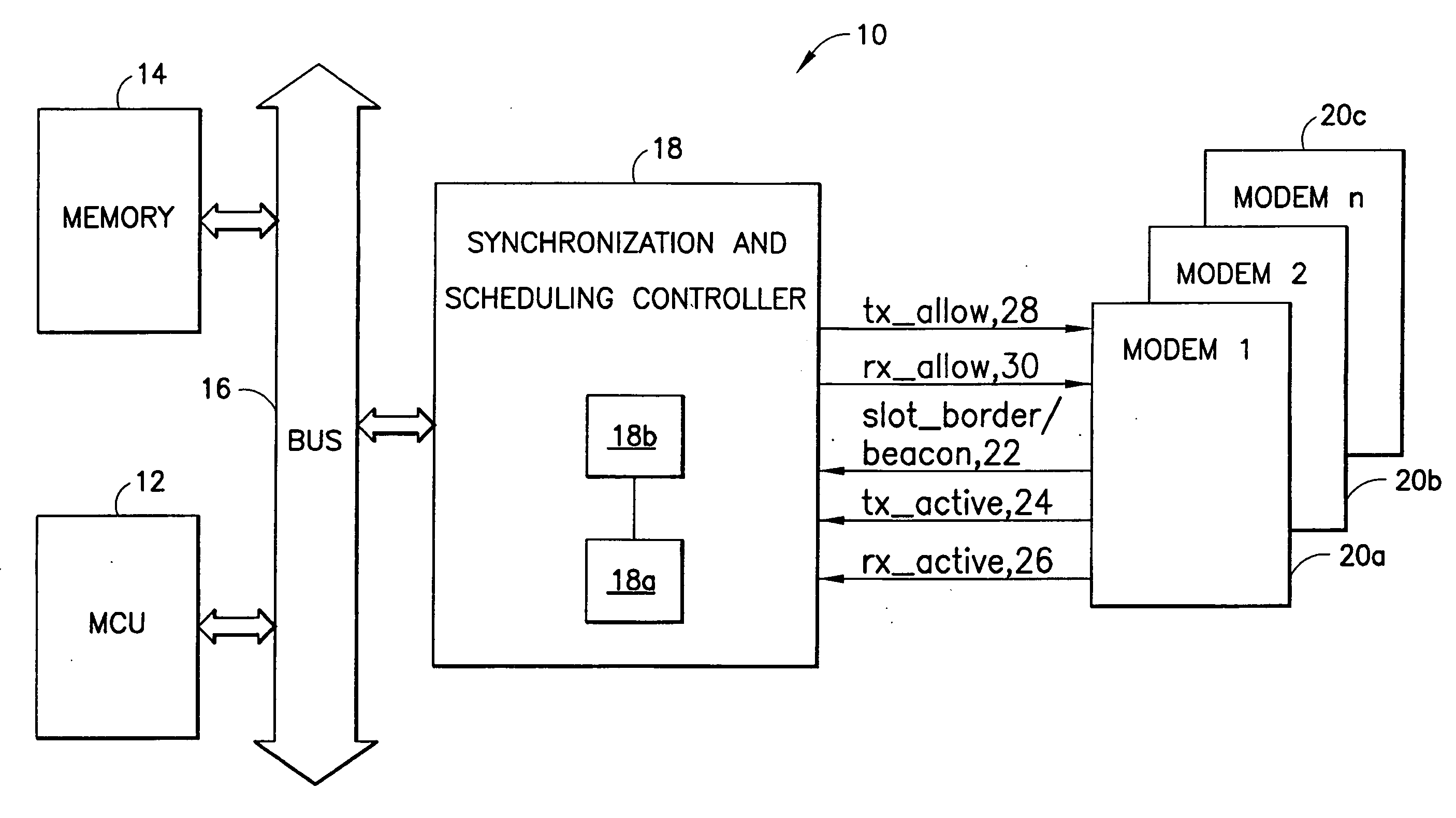

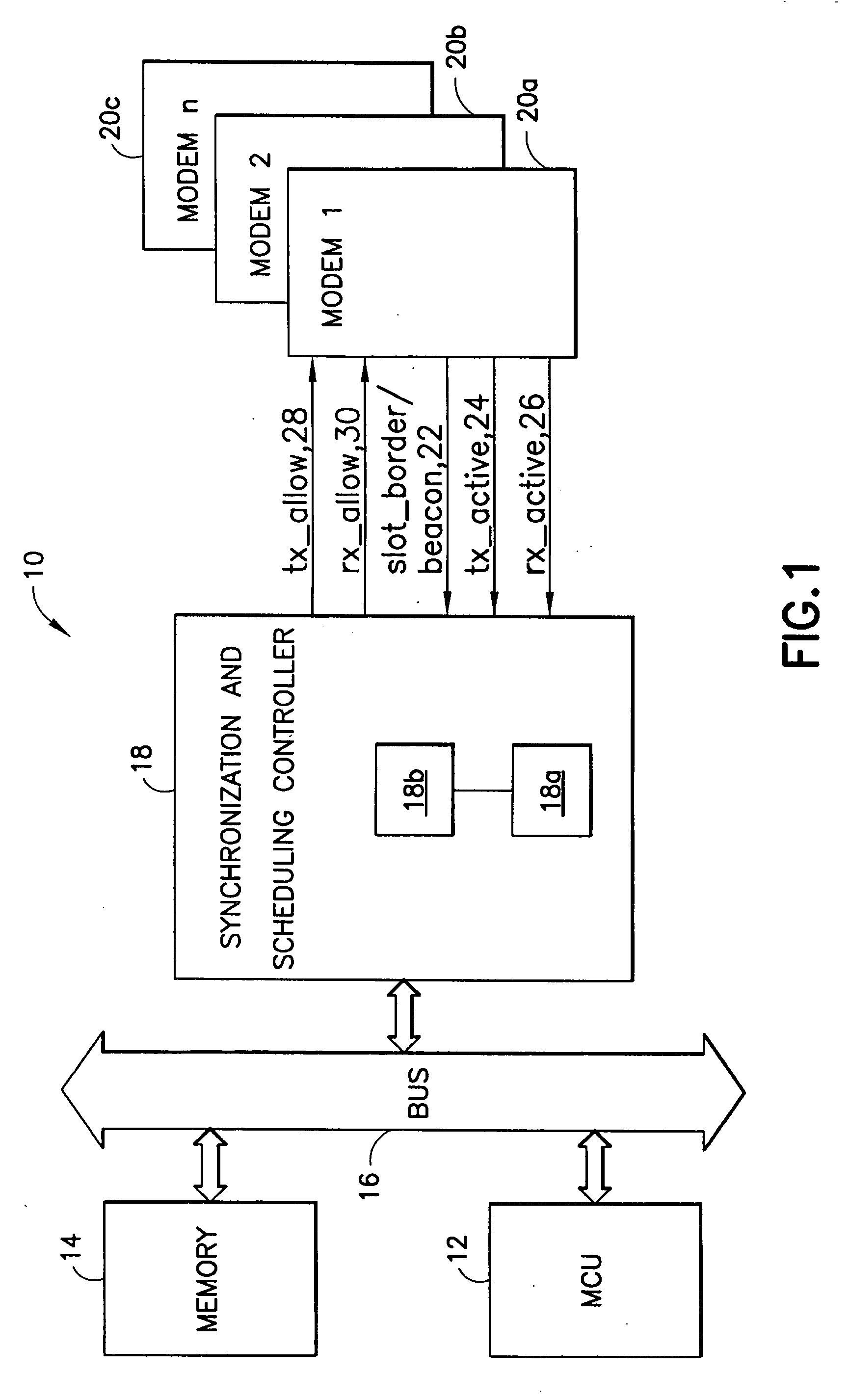

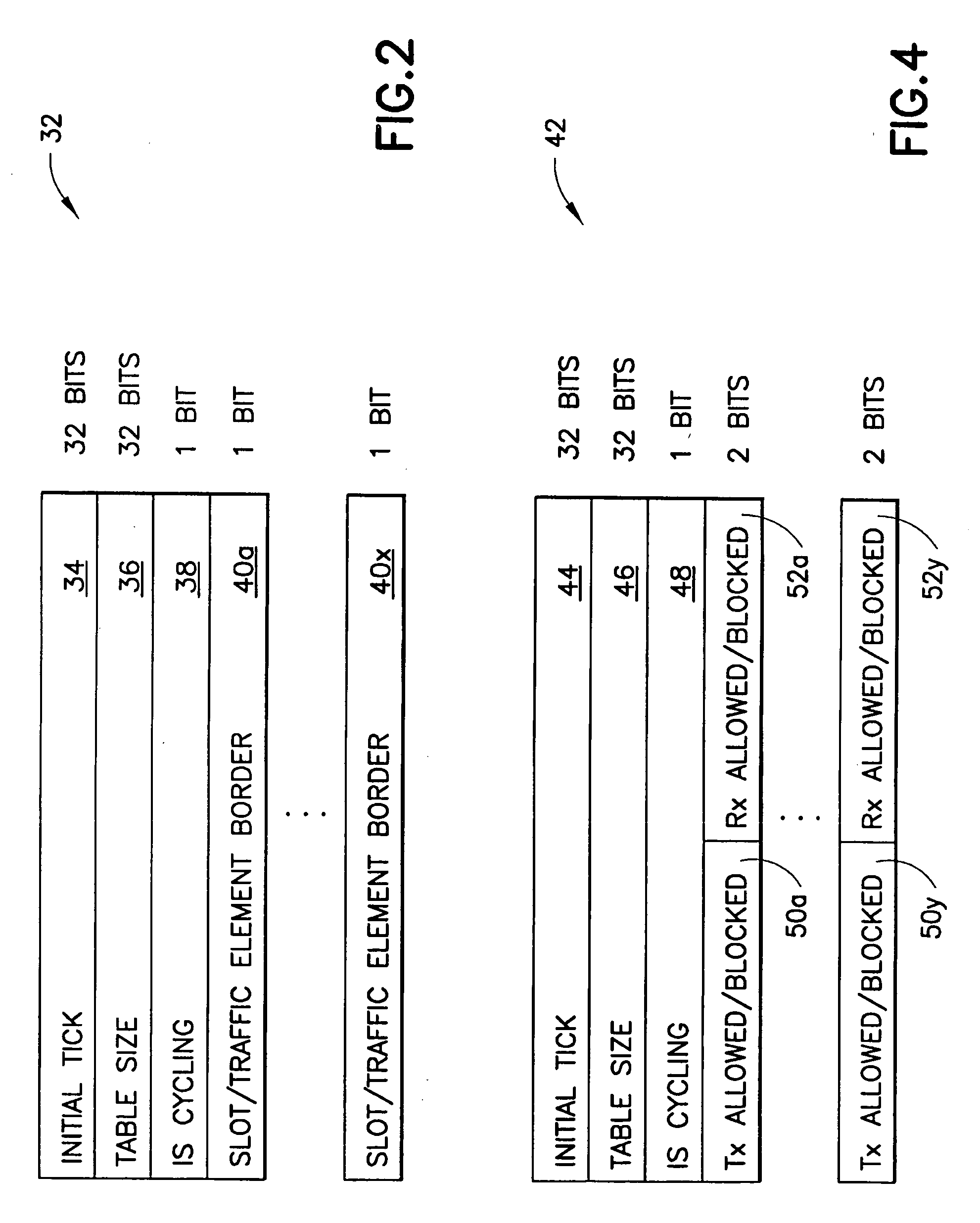

Apparatus, methods and computer program products providing pattern masking and traffic rule matrix scheduling for multiradio control

ActiveUS20080161030A1Radio/inductive link selection arrangementsRadio transmissionTraffic capacityModem device

Disclosed herein are apparatus, methods and computer program products for implementing pattern masking scheduling in a multiradio terminal having multiradio control. When a message to be carried by a modem is configured by a multiradio controller, it is given a priority and connection properties (such as, for example, frequency band, transmit power, connection pattern type, etc.) When a set of messages have been configured, the multiradio controller sets them in a priority order and using the properties, generates a traffic rule matrix. The priorities and traffic rule matrix are then used to govern access by the modems to the communications channel. The rule matrix can reflect various constraints. For example, if connections occupy the same frequency, the connections are not allowed to operate concurrently. If connections occupy the same physical resources, they are not allowed to operate simultaneously.

Owner:NOKIA TECHNOLOGLES OY

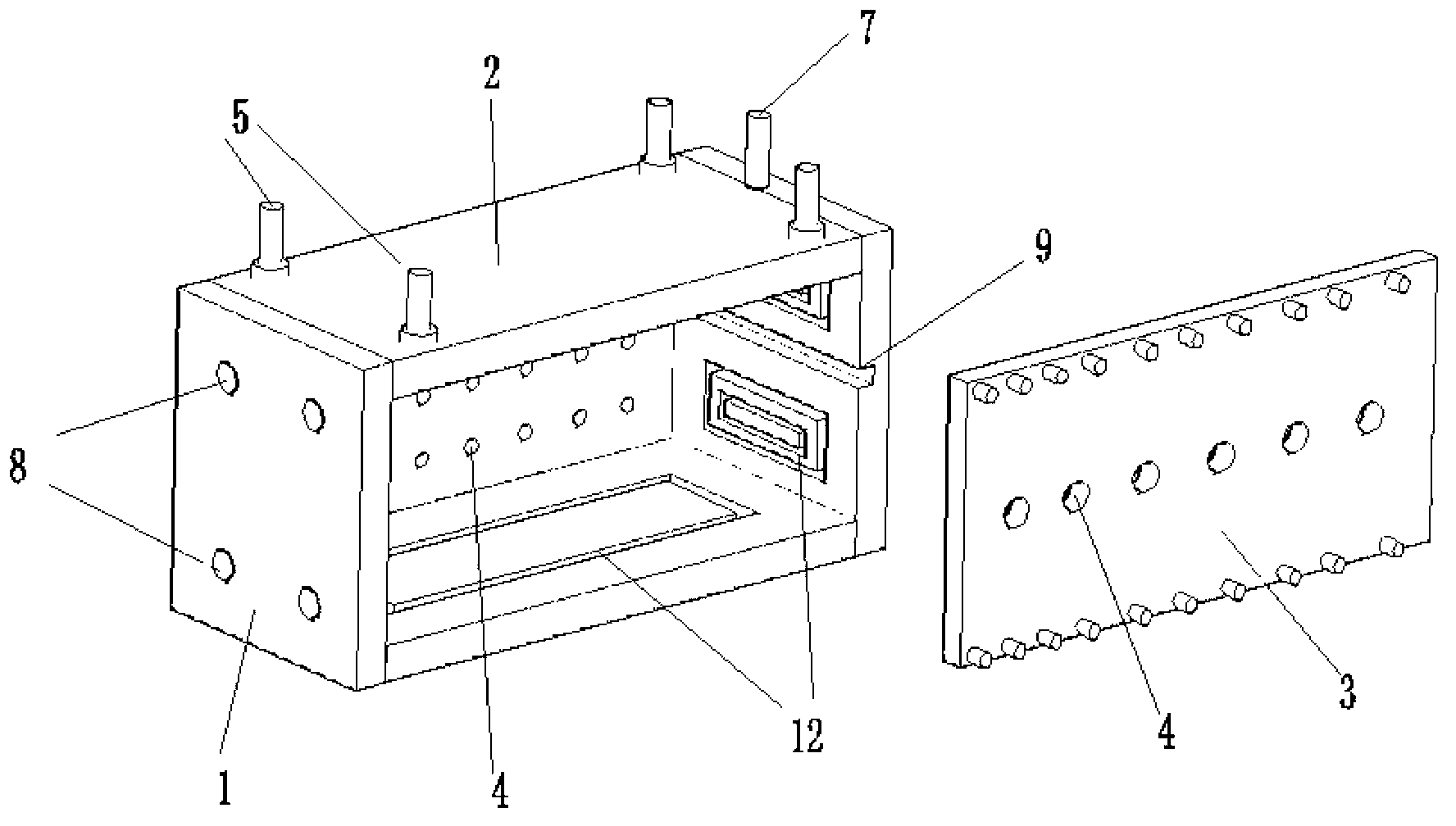

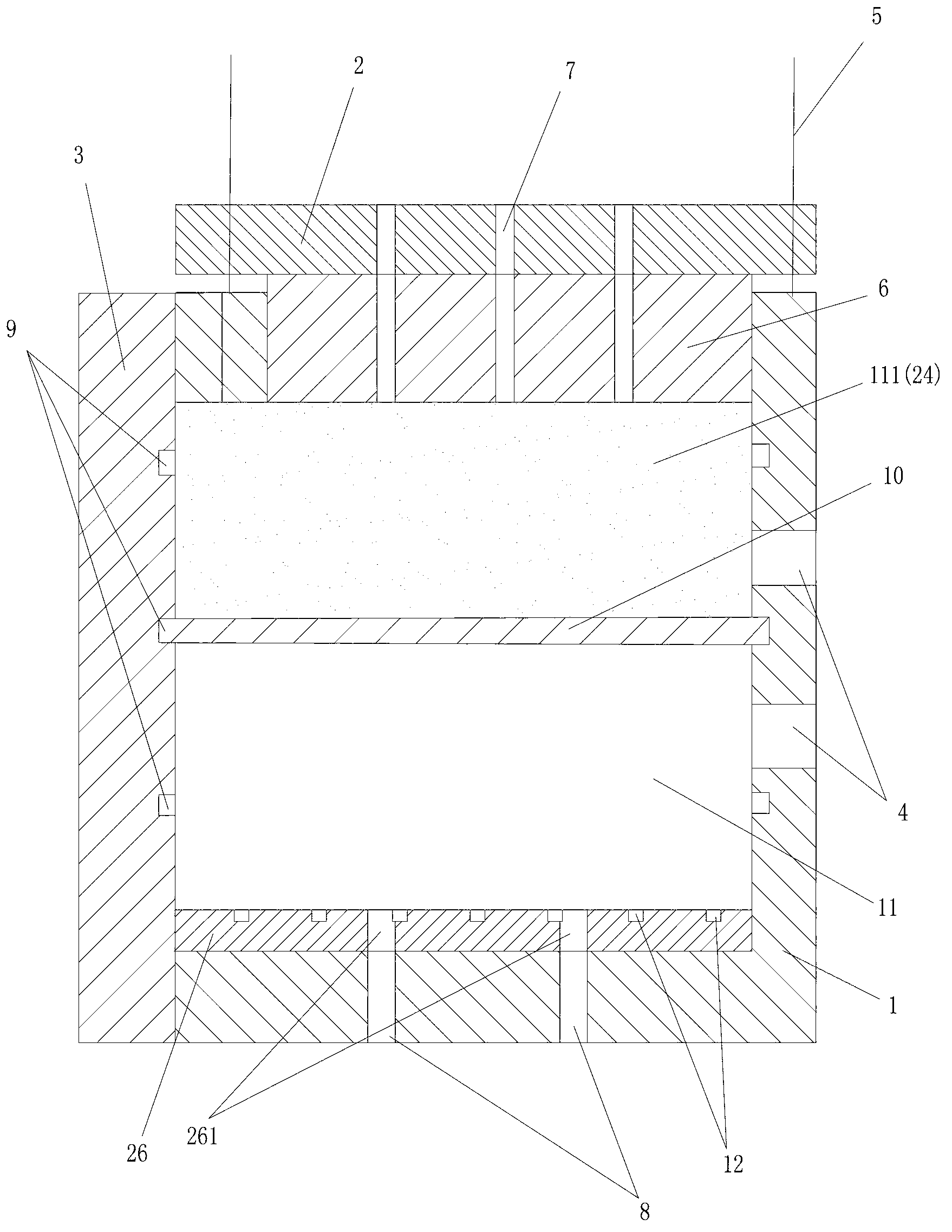

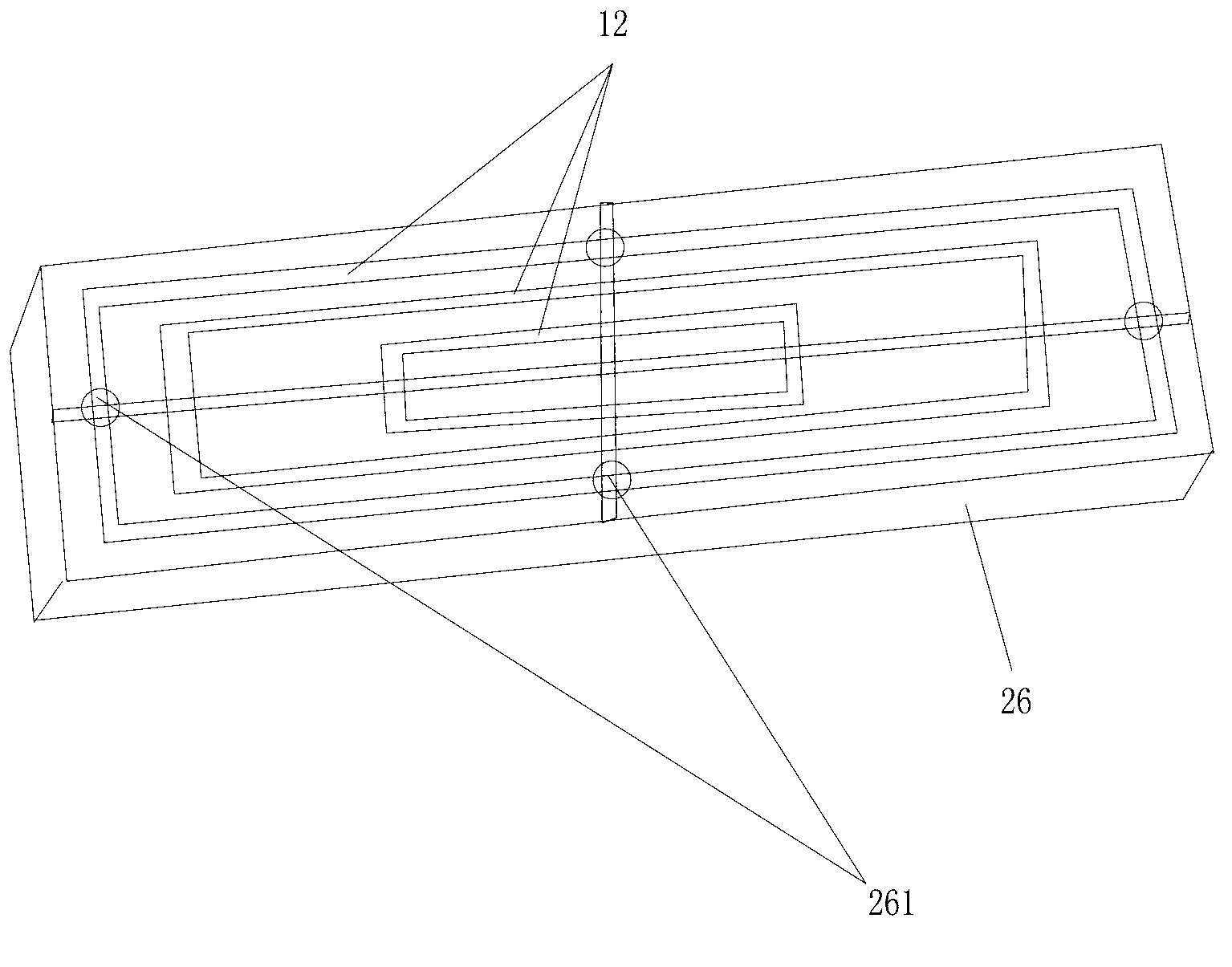

Method for manufacturing ultrasonic wave embossed release paper artificial leather

InactiveCN101570938AOvercome the problem of single leather textureNo cavitationLamination ancillary operationsPattern makingFoaming agentPotassium

The invention discloses a method for manufacturing ultrasonic wave embossed release paper artificial leather, which comprises the following steps: firstly, preparing raw materials of a bottom blank of the artificial leather, wherein a facing material comprises 100 portions of polyvinyl chloride paste resin, 60 to 70 portions of DOP, 20 to 30 portions of CaCO3 and 5 to 8 portions of potassium and zinc thermal stabilizer, a medium foaming layer comprises 100 portions of polyvinyl chloride paste resin, 65 to 80 portions of DOP, 150 to 250 portions of CaCO3, 4 to 8 portions of potassium and zinc thermal stabilizer and 8 to 16 portions of high-temperature foaming agent, and a bottom material bonding layer comprises 100 portions of polyvinyl chloride paste resin, 50 to 60 portions of DOP, 5 to 20 portions of CaCO3 and 2 to 5 portions of potassium and zinc thermal stabilizer; uniformly stirring the raw materials prepared according to the formula; making the bottom blank of the artificial leather; and obtaining a finished product by ultrasonic wave embossing. The method has the advantages of fully autonomic pattern types and cost conservation. The products of the method have high physical and chemical properties.

Owner:无锡市瑞莺合成革有限公司

Three-dimensional simulation device for edge/bottom water reservoir

The invention relates to a three-dimensional simulation device for an edge / bottom water reservoir. The device comprises a body and a detachable moving side wall which is arranged on the side surface of the body, wherein an accommodating cavity is formed in the body; a gland is arranged on the top of the body; a piston is arranged on the lower part of the gland; a plurality of vent holes communicated with the accommodating cavity are formed in the gland; an annular groove in which a clapboard can be arranged in a sealing mode is formed in the peripheral side wall of the accommodating cavity; a plurality of poroid functional measuring points are formed on all the wall surfaces of the body and the gland and are communicated with the accommodating cavity in a controlled mode; a plurality of granular porous media are fully filled in the accommodating cavity; and a plurality of pipe columns for simulating a mineshaft are arranged in the granular porous media in the accommodating cavity. By the device, edge / bottom water reservoirs which have different thicknesses and are developed at different dip angles in different displacement modes and different well pattern types can be subjected to physical simulation experiment, so that an oil-water percolation mechanism of an oil and gas reservoir can be researched, and the effects of the edge / bottom water reservoirs in different development modes can be evaluated.

Owner:CHINA UNIV OF PETROLEUM (BEIJING) +1

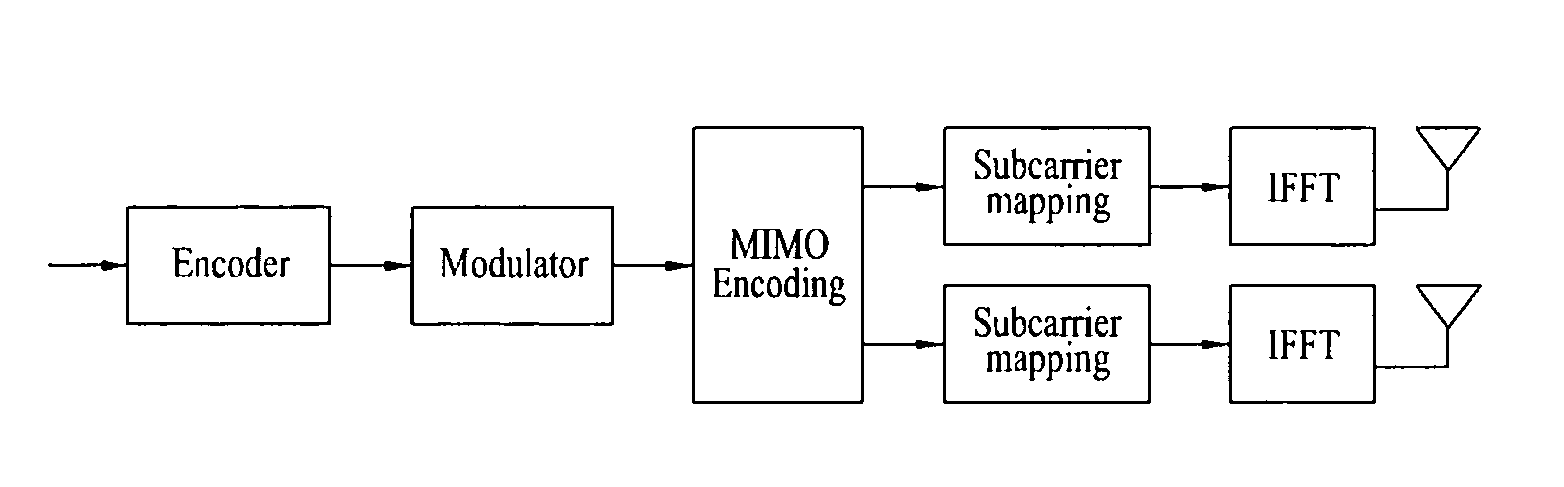

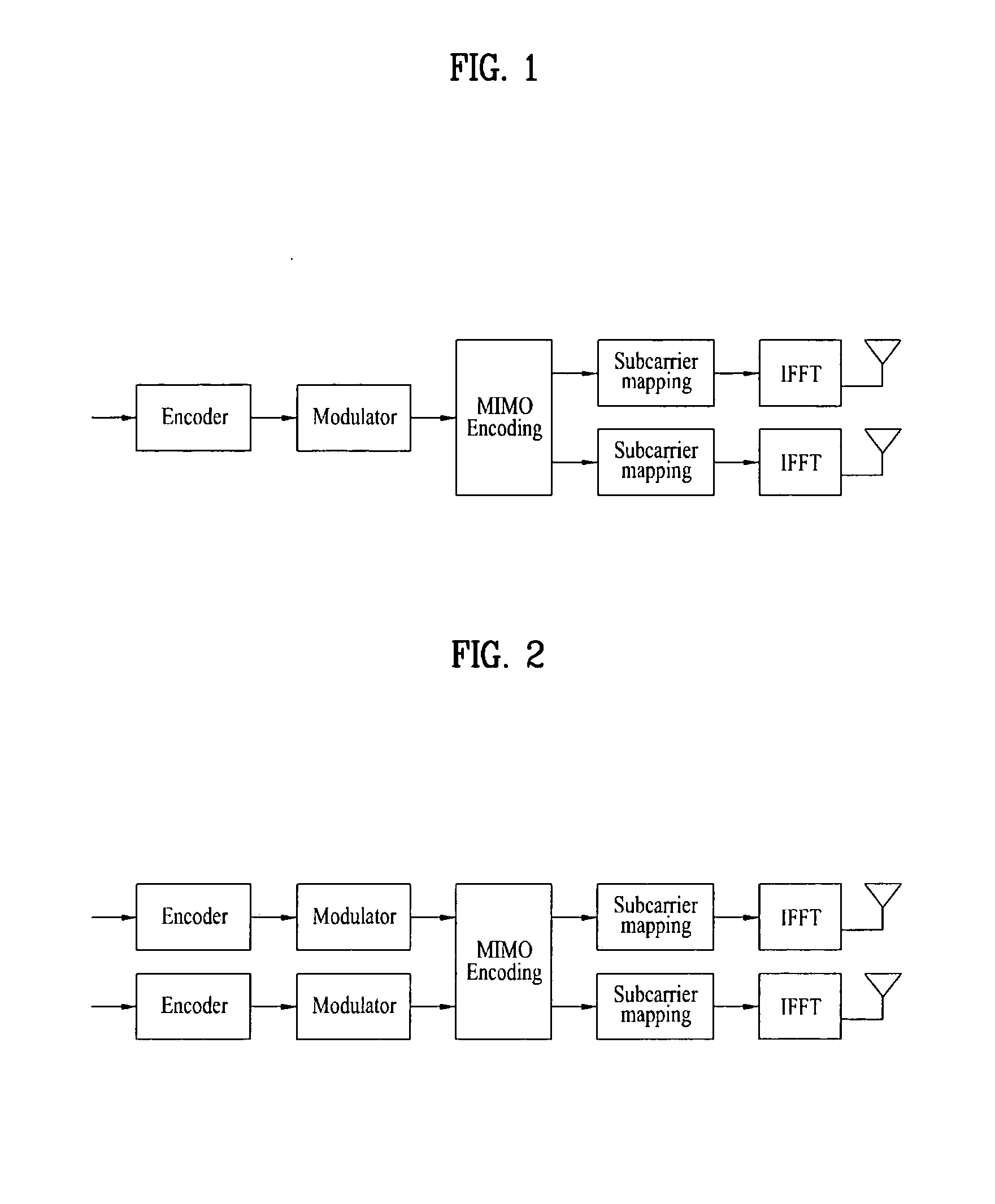

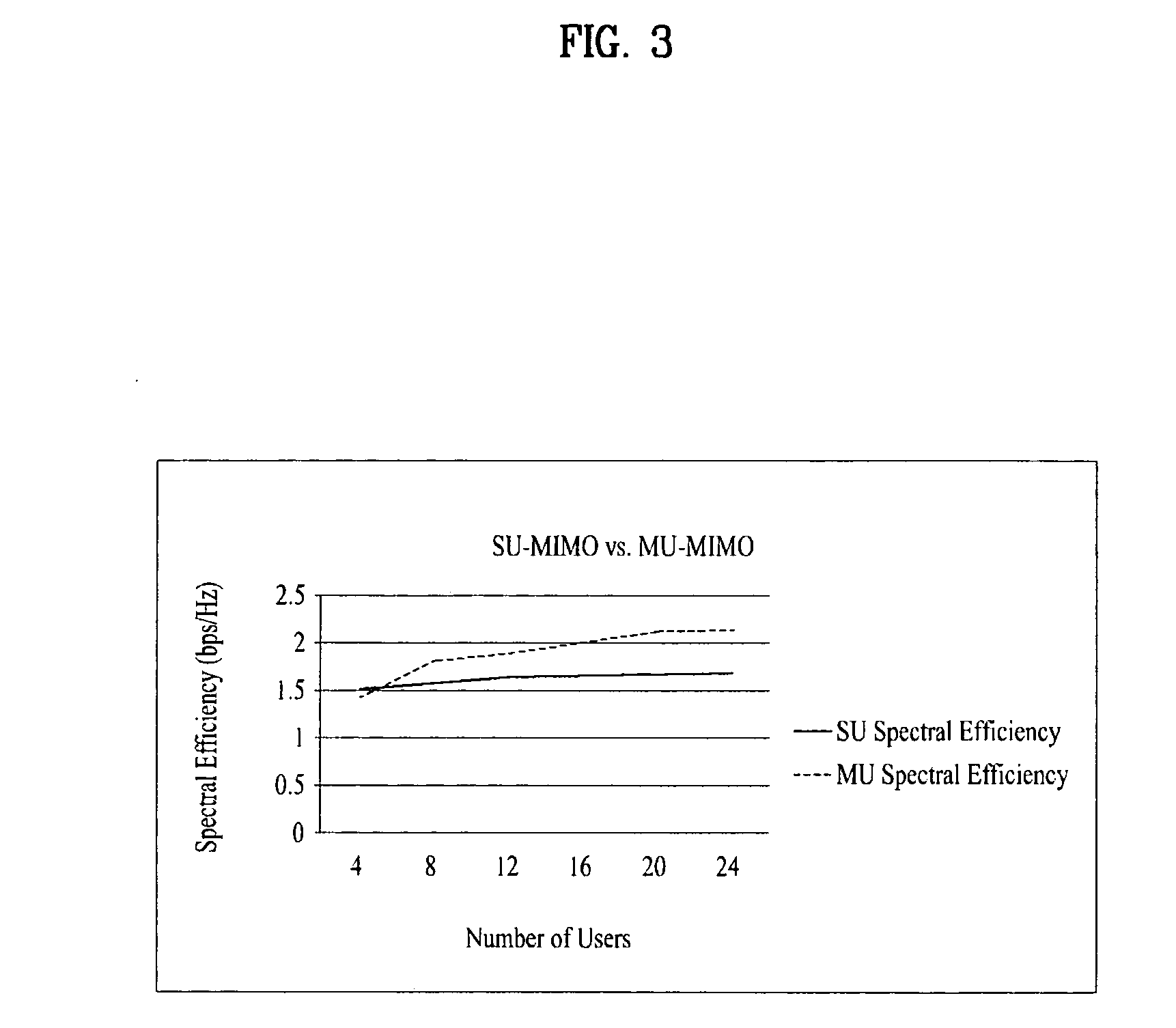

Feedback method for performing a feedback by using a codebook in MIMO system

InactiveUS20090257383A1System throughput is maximizedReduce the amount of feedbackDiversity/multi-antenna systemsWireless commuication servicesMobile stationComputer science

A feedback method for performing a feedback by using a codebook in Multiple Input Multiple Output (MIMO) system includes receiving, by the mobile station, a MIMO mode type information, generating feedback information by using the codebook selected according to the MIMO mode type information, and transmitting the feedback information to the base station. The codebook includes a SU-MIMO codebook and a MU-MIMO codebook, and the MU-MIMO codebook is formed by extracting codebook elements from the SU-MIMO codebook. As a result, the method maximizes a system throughput simultaneously while effectively reducing an amount of feedback information.

Owner:LG ELECTRONICS INC

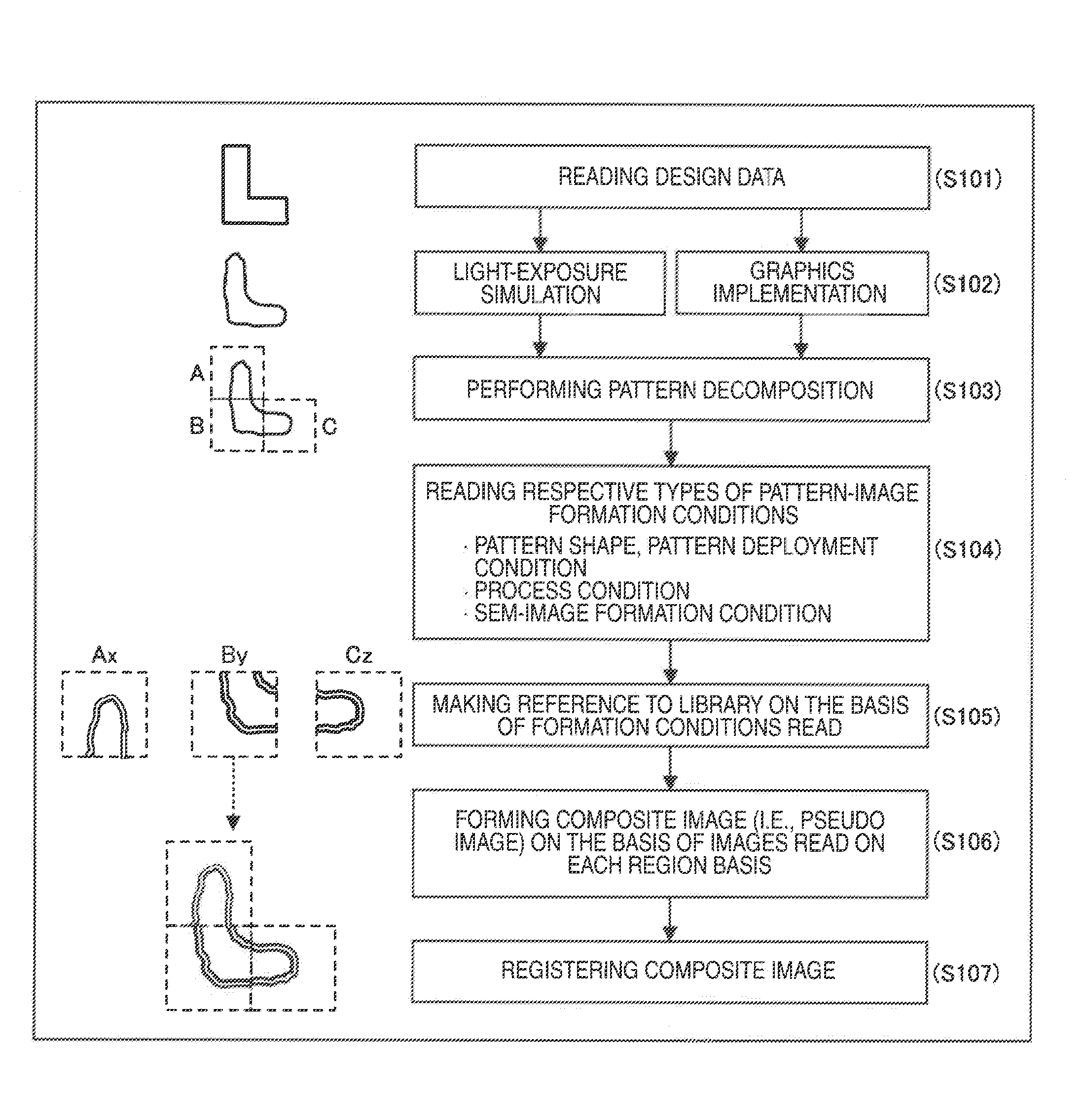

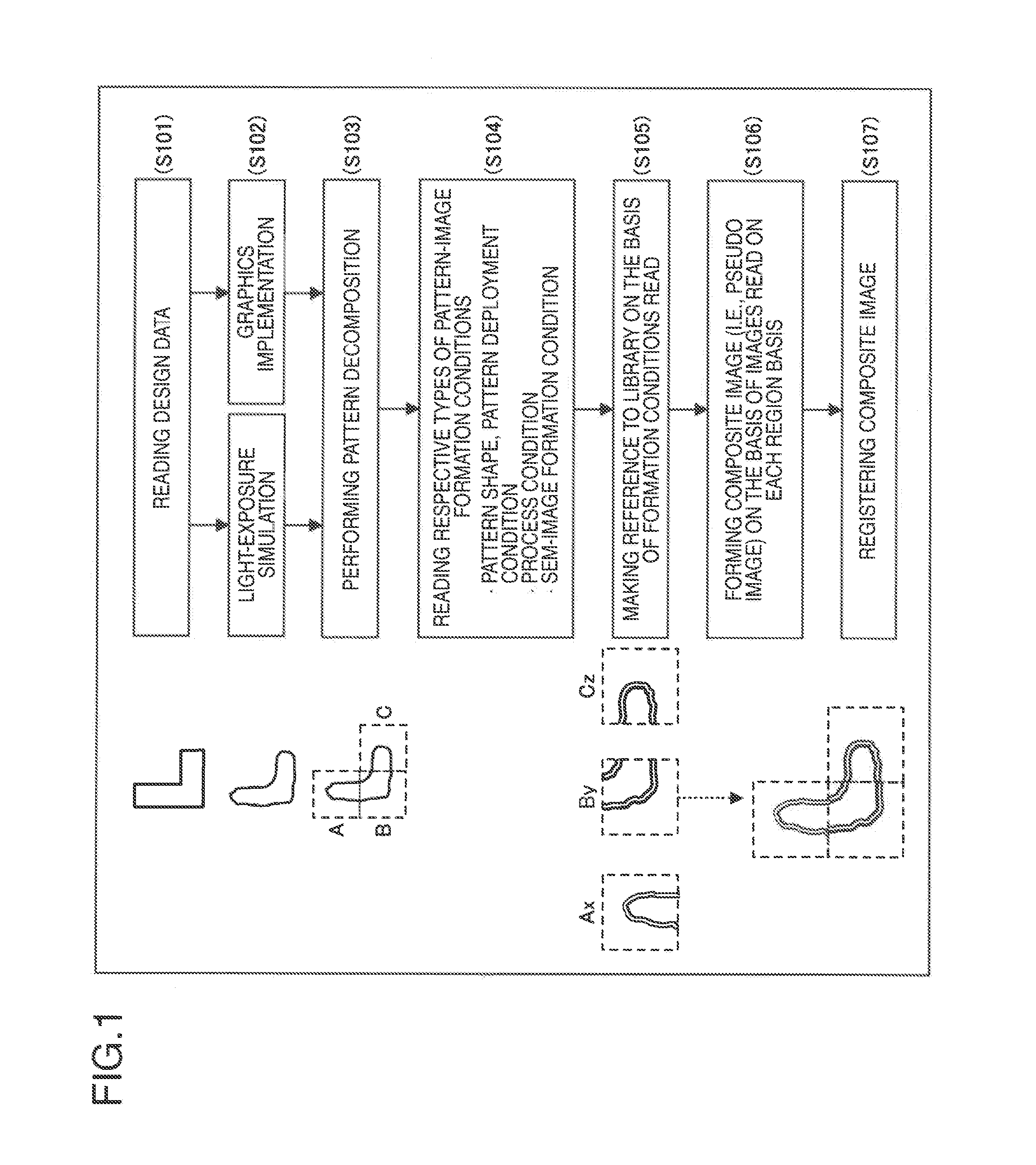

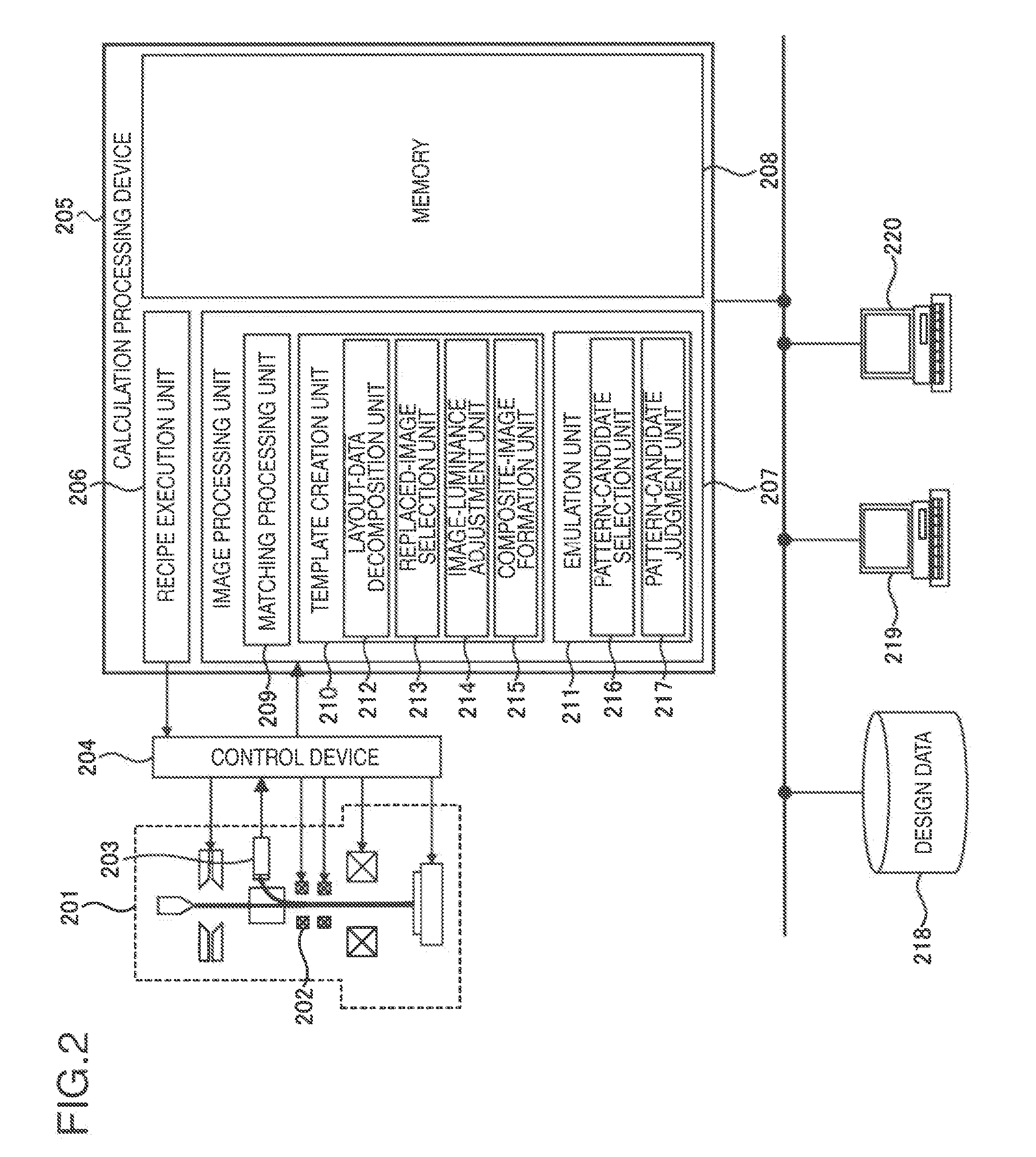

Image processing device and computer program for performing image processing

InactiveUS20130326439A1Easy to implementSemiconductor/solid-state device testing/measurementSolid-state devicesImaging processingDevice form

It is an object of the present invention to provide an image processing device for allowing an actual-image-closer pattern to be formed based on the design data, or its simulation image. In order to accomplish the above-described object, the proposal is made concerning an image processing device which includes an image processing unit which sets the operation condition of a charged-particle beam device on the basis of the design data on a semiconductor element. Here, the image processing device accesses a library for storing device-condition information on the charged-particle beam device, pattern types, and a plurality of combinations of pattern information on each pattern-region basis. Moreover, the image processing device forms a composite image of each pattern region, using the pattern information on each pattern-region basis, and based on the device-condition information and the selection of a pattern type from the pattern types.

Owner:HITACHI HIGH-TECH CORP

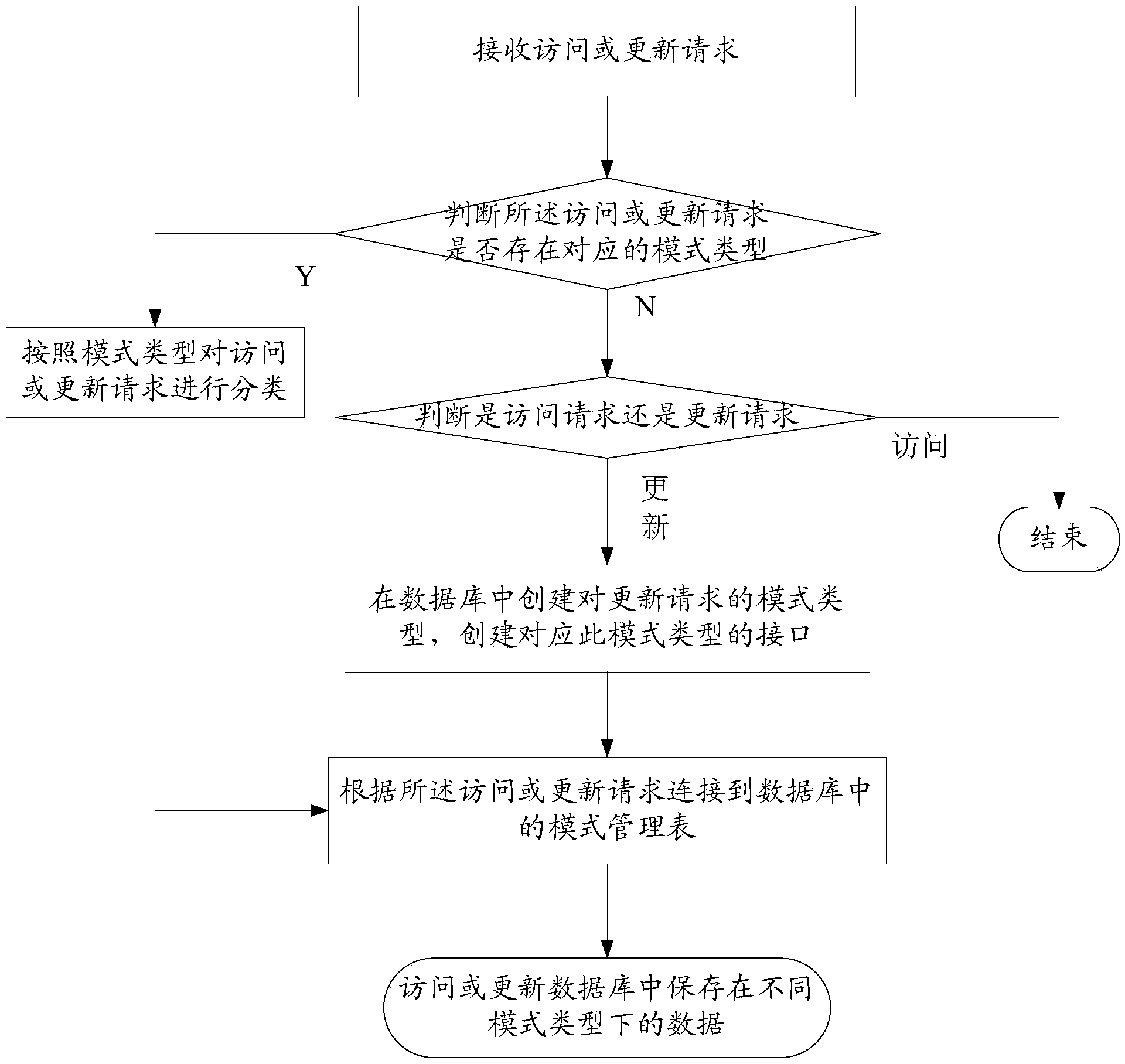

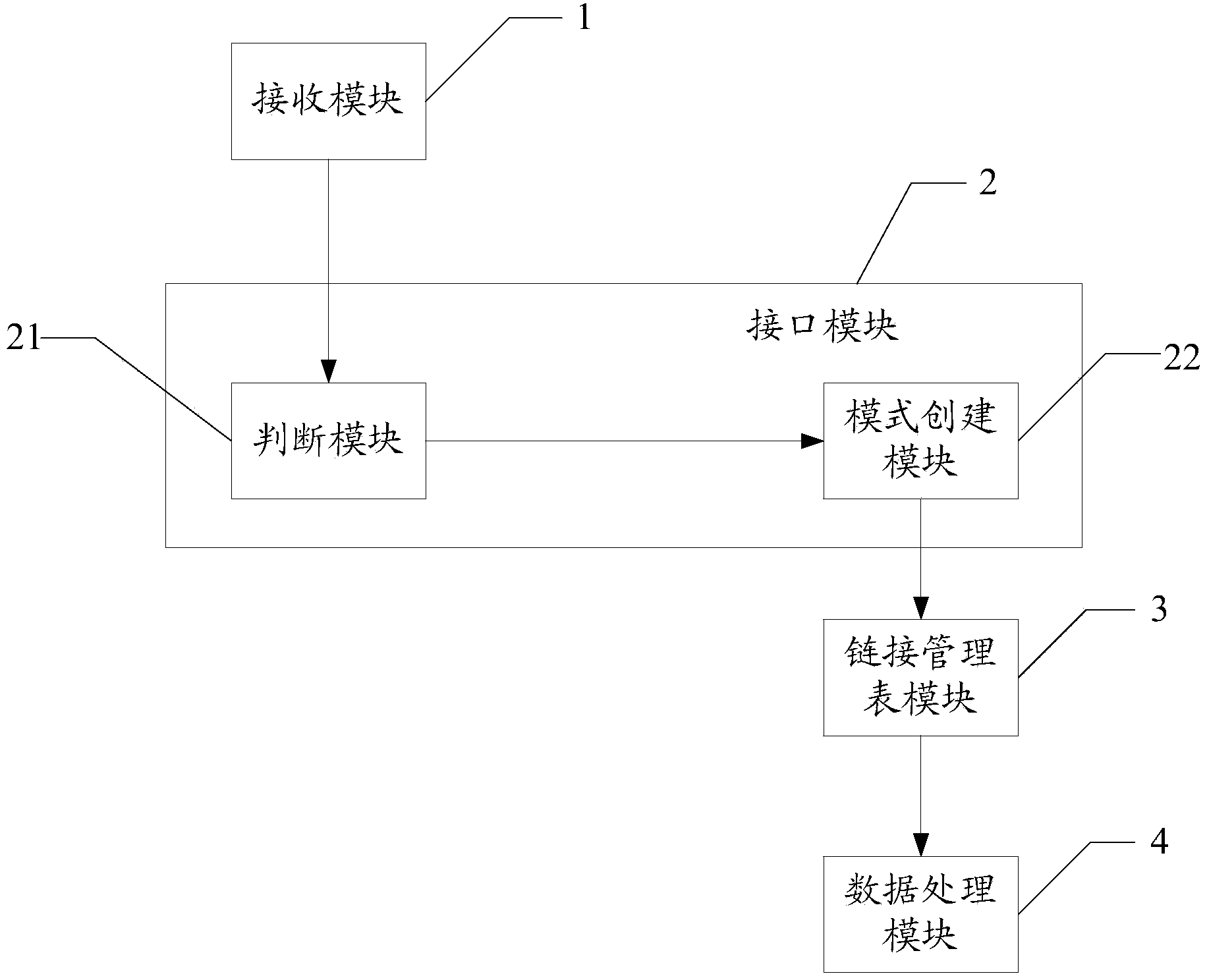

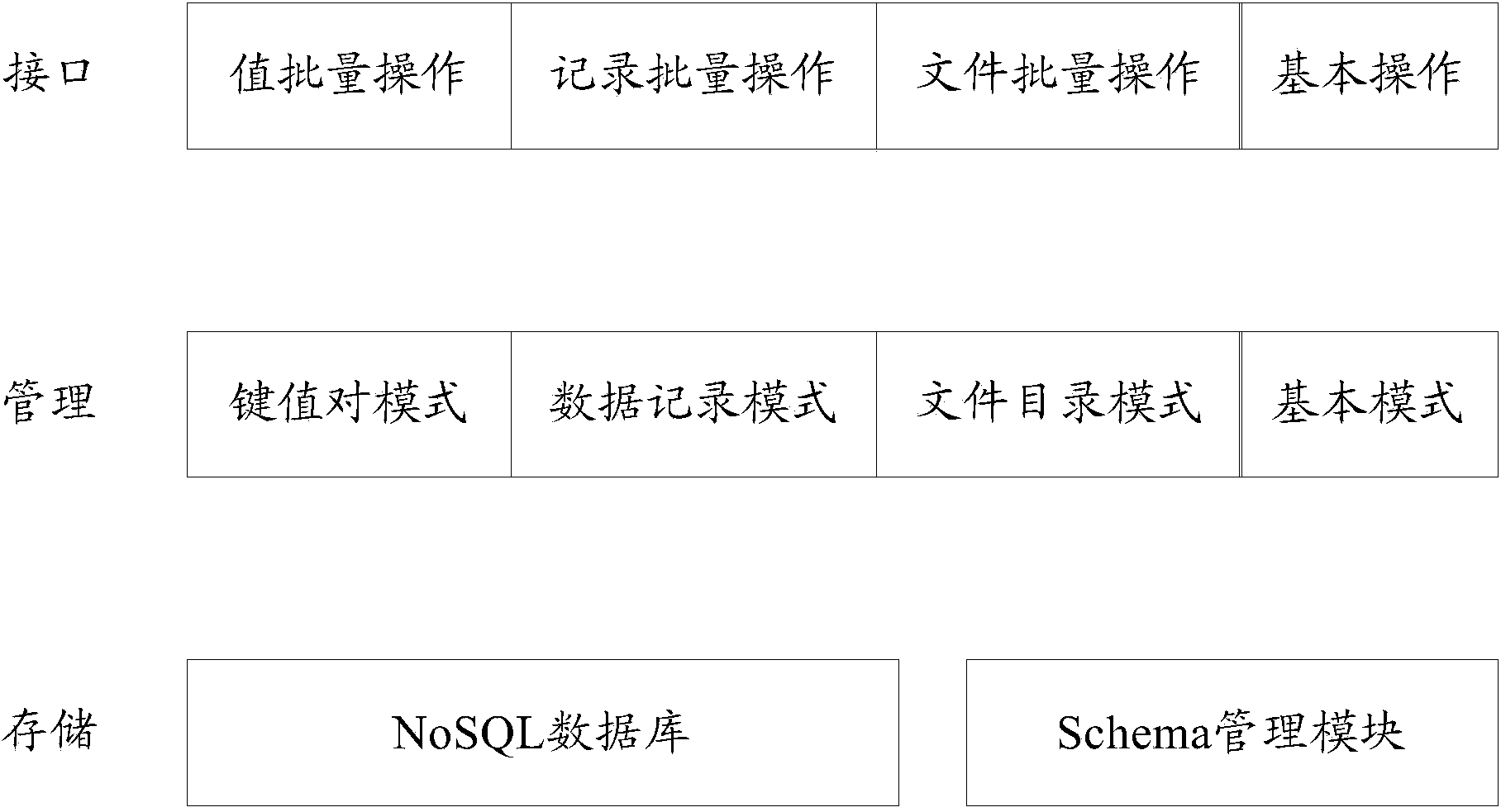

Pattern management method and system of NoSQL database

ActiveCN103714163APerfectly compatibleRealize unified managementSpecial data processing applicationsInterface designHigh Readings

The invention relates to a pattern management method of a NoSQL database. The pattern management method specifically includes the following steps that firstly, accessing or updating requests are received; secondly, classification is performed on the accessing or updating requests according to pattern types, or new pattern types and interfaces corresponding to the new pattern types are constructed according to the accessing or updating requests; thirdly, according to a pattern management table connected into the database by the accessing or updating requests through the interfaces corresponding to the pattern types, pattern information in the pattern management table is obtained; fourthly, according to a route provided by the pattern management table, data stored under different pattern types in the database are accessed or updated according to the accessing or updating requests. According to the pattern management method of the NoSQL database, unified management of various heterogeneous data in the NoSQL database is performed; according to different types and features of the data, differential pattern and interface design is achieved, and the high reading and writing performance is ensured. Meanwhile, the universal schema management strategy and a universal read-write interface are provided, and convenience is provided for expansion of data patterns.

Owner:INST OF INFORMATION ENG CAS

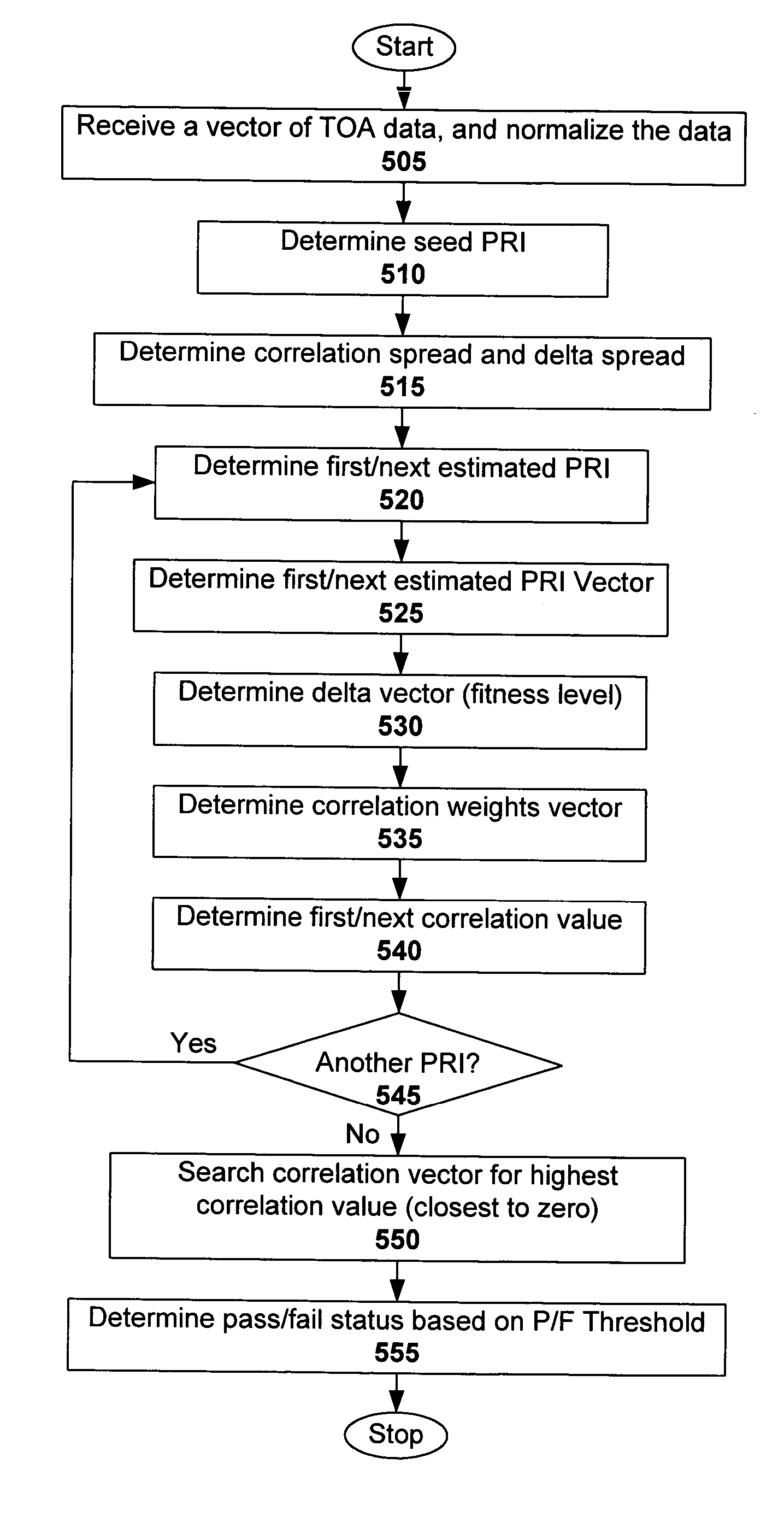

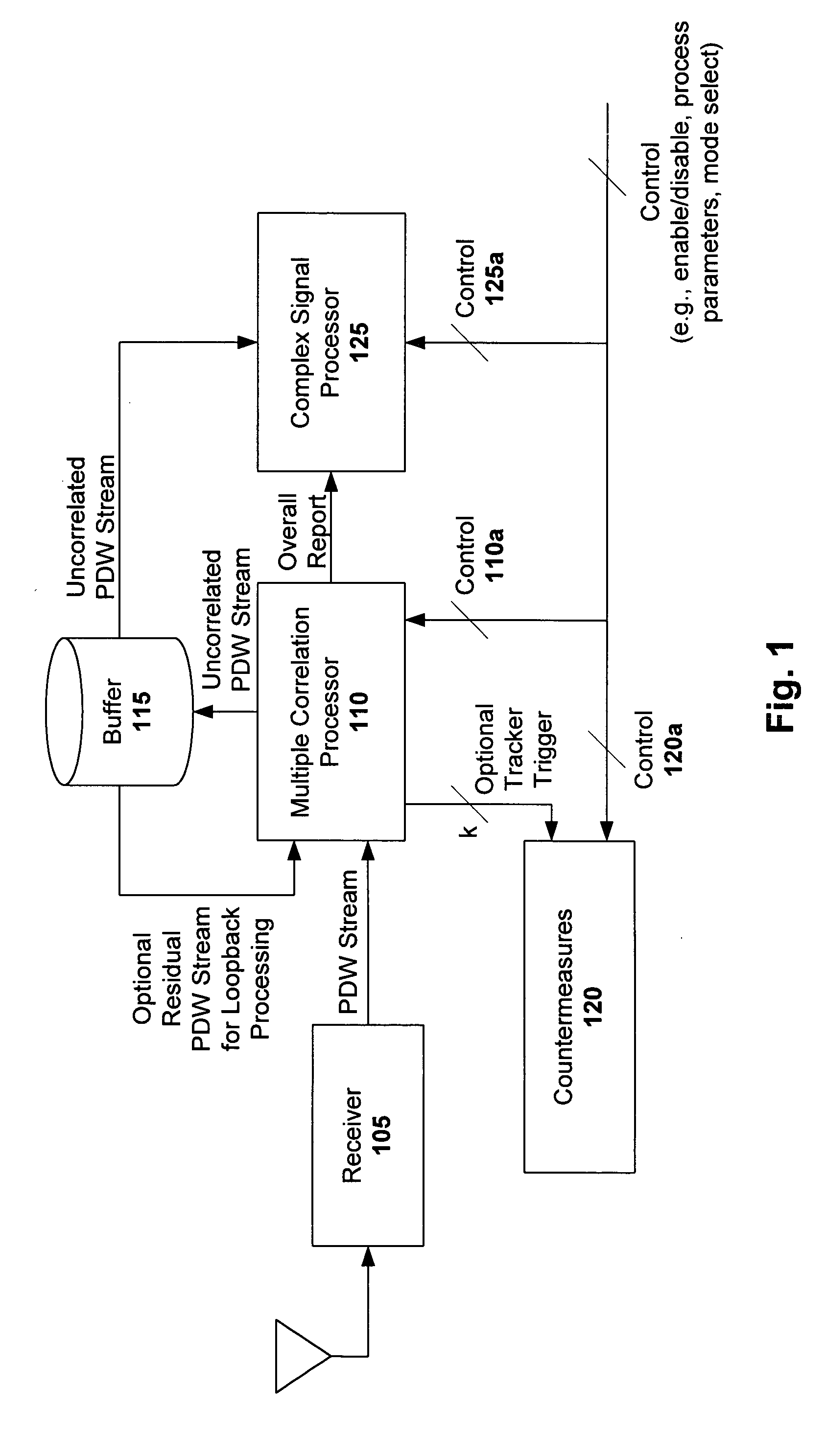

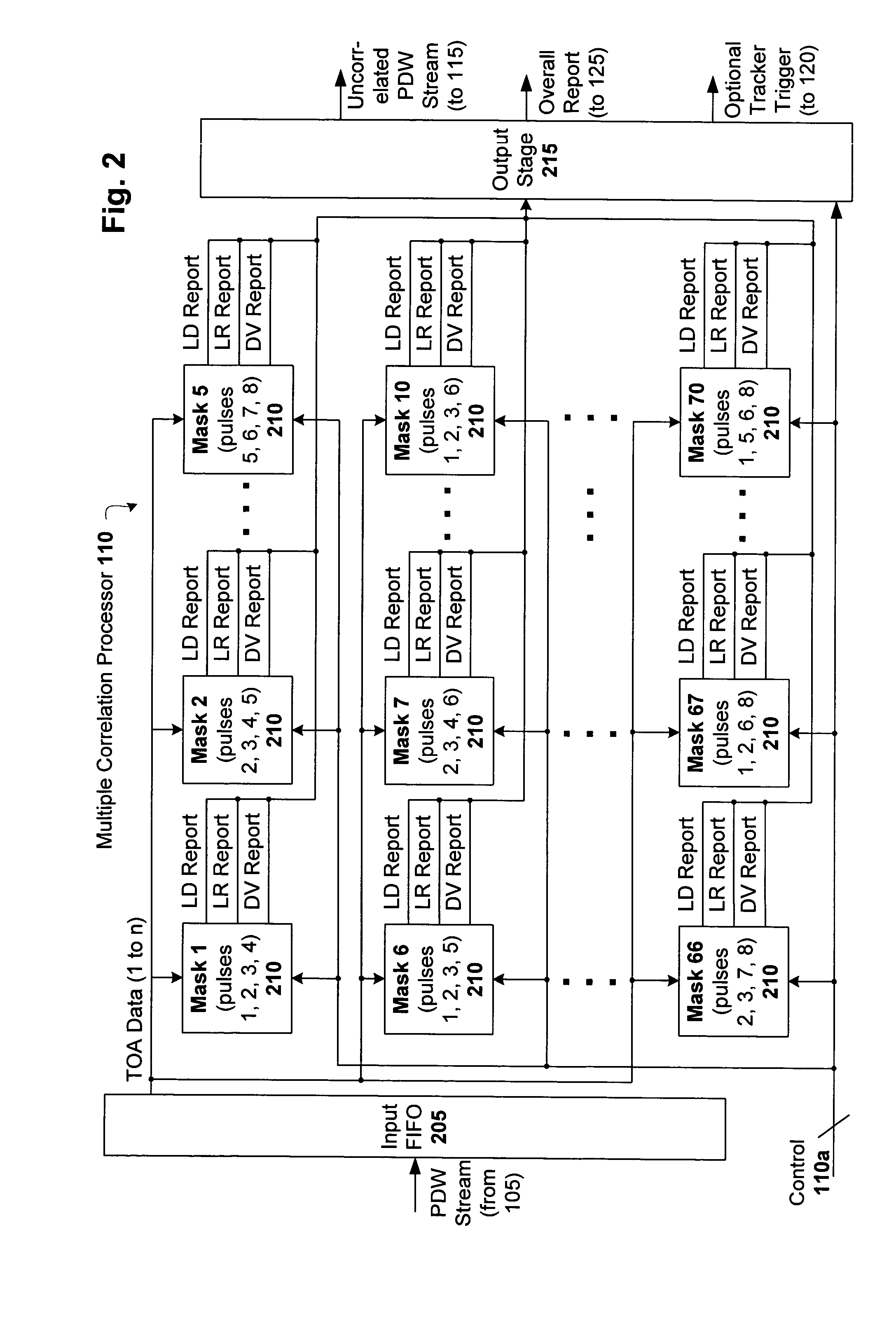

Detection and identification of stable PRI patterns using multiple parallel hypothesis correlation algorithms

ActiveUS20050033789A1Reduce computational processingReduce data volumeWave based measurement systemsComplex mathematical operationsLimited resourcesHypothesis

An algorithmic approaches that can be implemented in software / firmware / hardware that filters out stable PRI patterns detected within a system that is prosecuting against radar based transmissions are disclosed. The algorithms allow downstream computing assets to concentrate their limited resources on the more complex emitter PRI pattern types. Thus, a portion (e.g., stable signals) of the pulse deinterleave and PRI identification problem is solved without requiring the more computationally expensive processing. The disclosed algorithms can be employed, for example, in electronic support measures (ESM) systems, electronic intelligence (ELINT) systems, and / or a electronic countermeasures (ECM) systems. The algorithms employ linear detection, linear regression, or a combination of linear detection and linear regression, thereby providing a “dual voting” scheme that decreases the occurrence of false positives. Other algorithmic approaches can be used as well in a multi-voting scheme that considers PRI estimates from distinct analysis types.

Owner:CALLAHAN CELLULAR L L C

Pushbutton solenoid shifter

A solenoid actuated transmission shifting apparatus is provided for temporary or permanent installation in automobiles with conventional, H-pattern-type manual transmissions or automatic transmissions and also for use with motorcycle transmissions. The shifting apparatus allows for both upshifting and downshifting through the transmission gears by pressing pushbuttons mounted on the steering wheel, handlebar or dashboard.

Owner:FUNK SR DAVID G +1

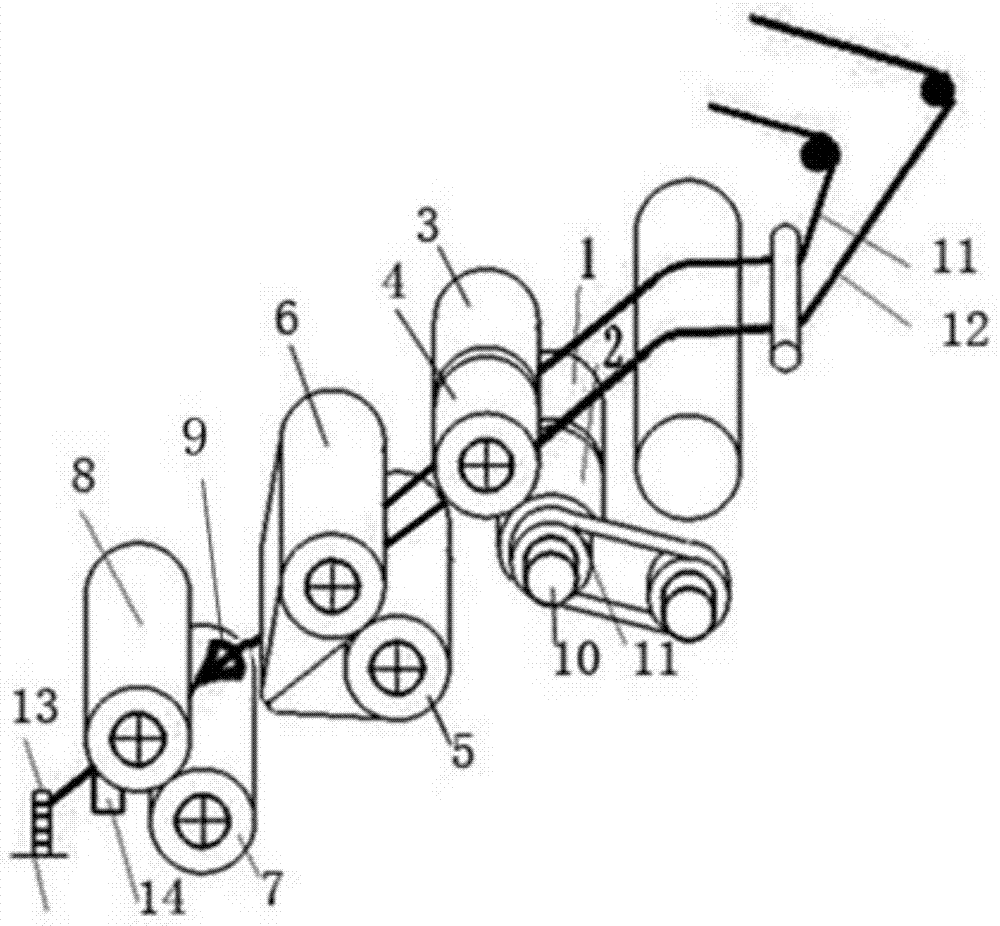

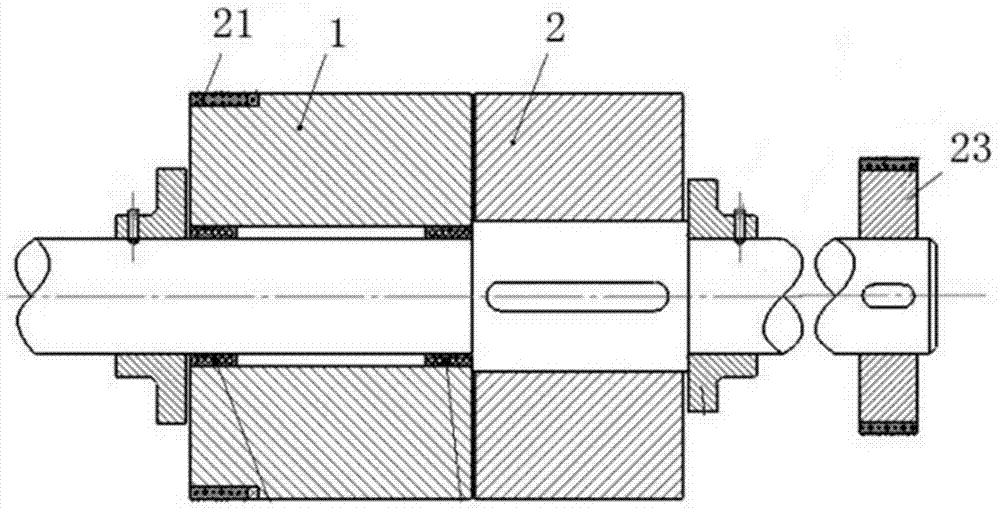

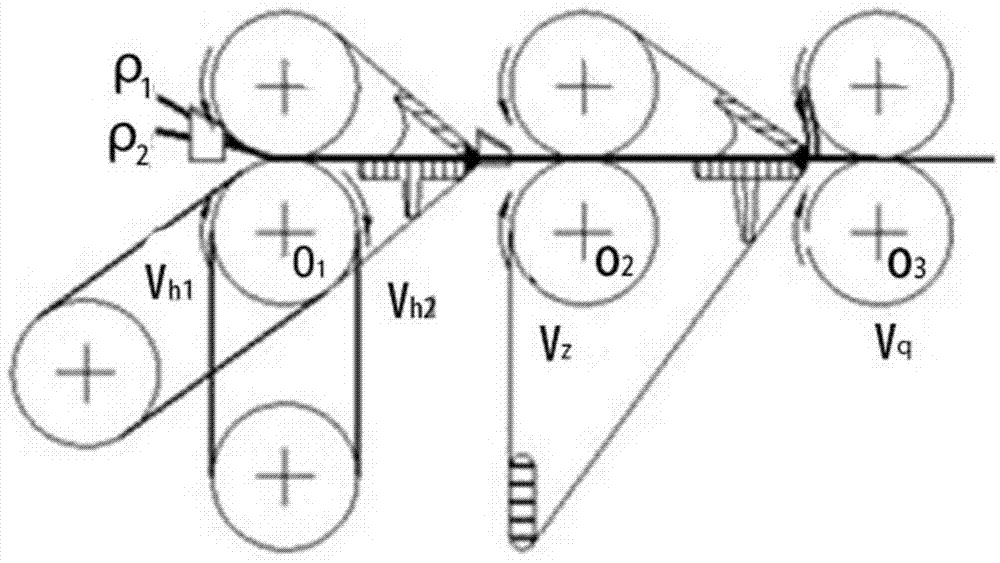

Two-component asynchronous and synchronous two-stage drafting colorful bunchy yarn spinning method and device

The invention discloses a colorful bunchy yarn spinning method based on two-component combined type asynchronous and synchronous two-stage drafting. The method particularly comprises a drafting and twisting system which comprises a primary drafting unit, a secondary drafting unit and a combining twisting unit, and wherein the primary drafting unit, the secondary drafting unit and the combining twisting unit are arranged front and back. The primary drafting unit comprises a combined rear roller and a middle roller. The secondary drafting unit comprises a front roller and the middle roller. The two-component mixing ratio and dynamic changes of linear density are controlled through a primary asynchronous drafting mechanism, and datum linear density is controlled through a secondary synchronous drafting mechanism. The changes of the linear density (the shape of a bamboo joint attached to datum yarn) can be precisely controlled, and the change of the color of the yarn (the color of the bamboo joint and the color of the datum yarn of the bamboo joint) can be precisely controlled. Meanwhile, the middle roller is controlled to rotate with constant set speed, the reproducibility of the pattern type and color of the variable-linear-density yarn is guaranteed, and the spinning effect is more stable.

Owner:JIANGNAN UNIV

Semi-worsted double-face different-color nap-down corrugated fleece and production process thereof

InactiveCN106192132AFluff evenlyOrnamental textile articlesLiquid/gas/vapor removalWorstedEngineering

The invention provides semi-worsted double-face different-color nap-down corrugated fleece and a production process thereof and relates to improvement in double-face corrugated fleece and a production process thereof. The semi-worsted double-face different-color nap-down corrugated fleece is characterized by comprising a fabric body; the fabric body is cloth woven from fine warp and coarse weft, the double faces have different colors, semi-combed section dyed yarn is arranged on the front face, semi-combed color yarn is arranged on the reverse side, and the upper portion and the lower portion are tied to form a double-layer organization structure; the front and reverse face texture of the fabric body is 1 / 3 broken twill. A brand-new process is adopted for the product, and the effects of jacquard weave and printing of former drap-de-berry are exceeded. The semi-worsted double-face different-color nap-down corrugated fleece presents a new appearance for people. The semi-worsted double-face different-color nap-down corrugated fleece is a pioneer of the double-face fleece product style, and the blank in domestic drap-de-berry pattern type products is filled in.

Owner:阜新新溢达毛纺织有限公司

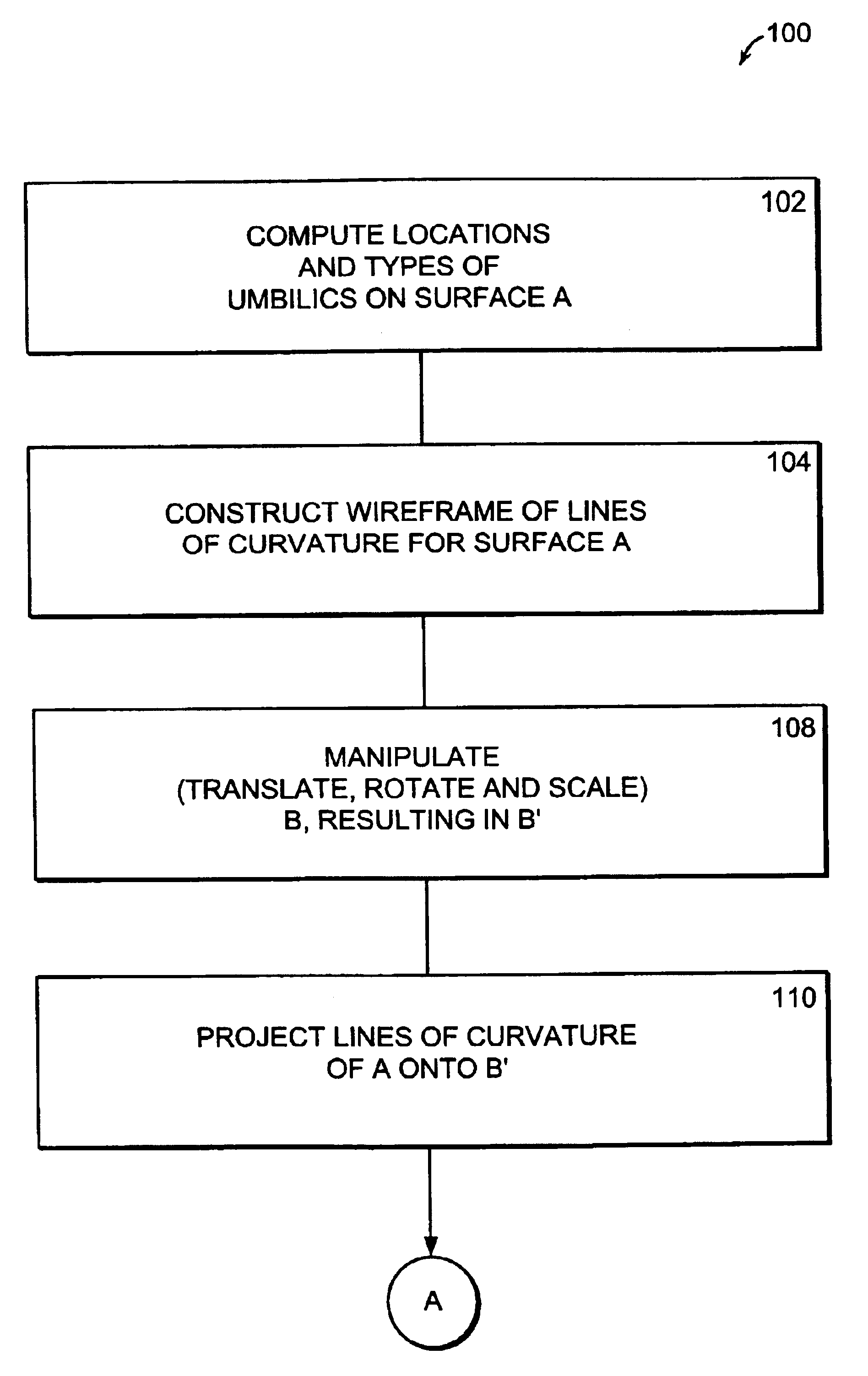

Shape-intrinsic watermarks for 3-D solids

InactiveUS6956568B2Character and pattern recognitionImage data processing detailsIntrinsicsComputer vision

Owner:MASSACHUSETTS INST OF TECH

Optimized nutritional formulations, methods for selection of tailored diets therefrom, and methods of use thereof

Nutritional compositions and formulations that optimize nutritional contents are provided. Dietary compositions and methods for tailoring such compositions to optimize levels of nutrients that have beneficial effects within specific ranges are provided. Dietary plans, and formulations comprising dietary products that comprise optimized levels of nutrients derived from phytochemicals, antioxidants, vitamins, minerals, lipids, proteins, carbohydrates, probiotics, prebiotics, microorganisms and fiber. Diet plans and modular nutritional packages comprising food and drink items tailored according to consumer patterns typed by diet, age, size, gender, medical conditions, family history, climate and the like are provided.

Owner:ASHA NUTRITION SCI INC

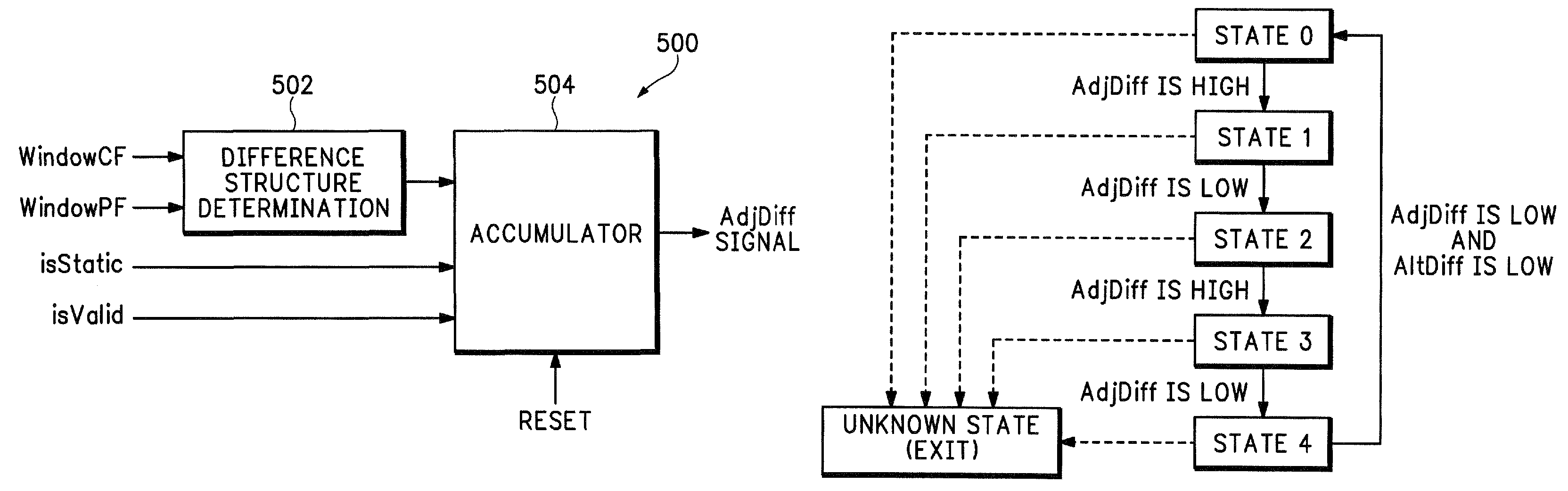

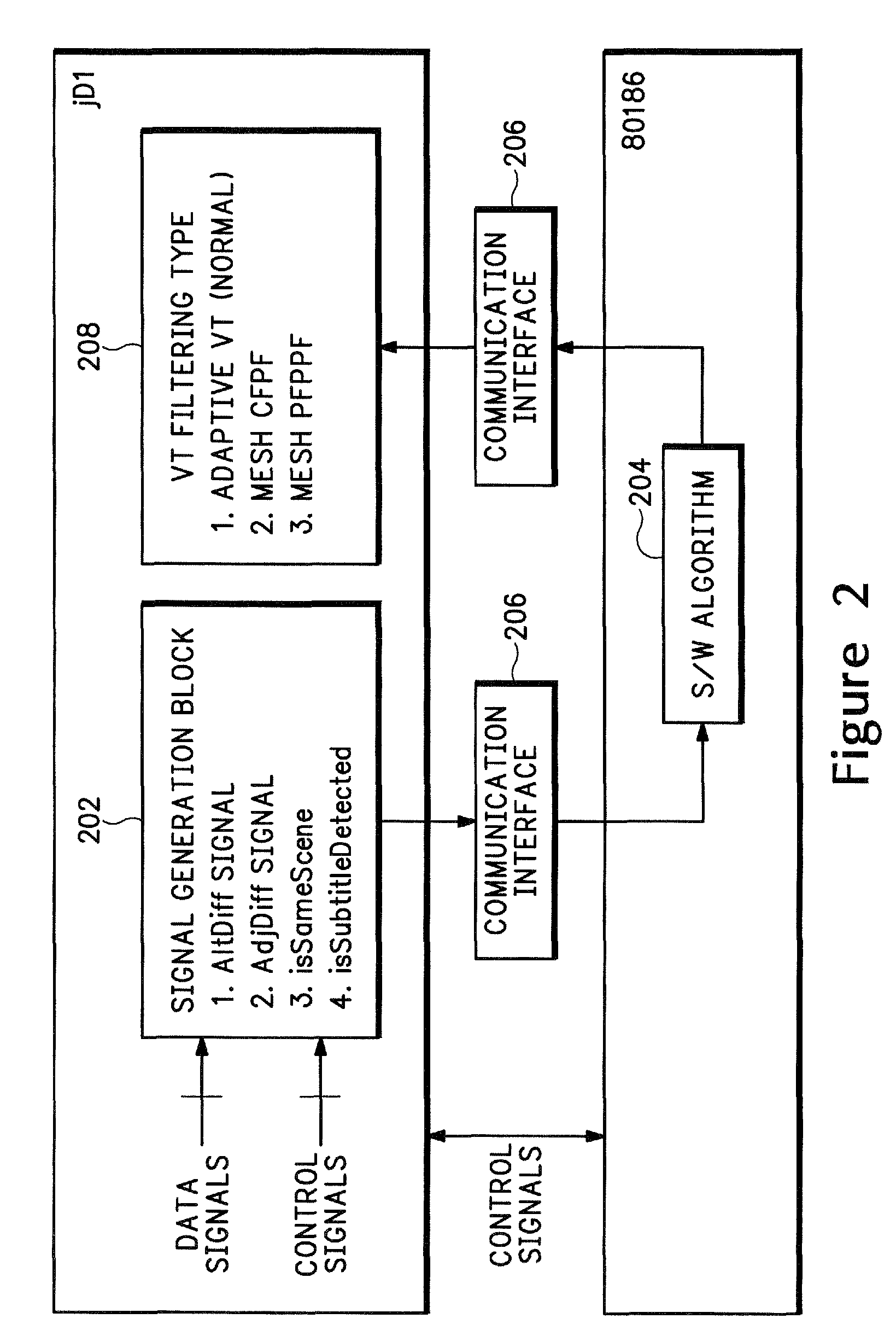

System and method for detecting a non-video source in video signals

InactiveUS7800692B2Television system detailsColor signal processing circuitsPattern recognitionVideo sequence

A video sequence may include a modality corresponding with an embedded pattern. At least one state machine detects the modality in accordance with difference signals. A signal generator generates the difference signals responsive to decision windows that define regions of interest in the video sequence. The modality may correspond with an embedded film source or other pattern types in the video sequence. Where the state machine detects more than one pattern, a single pattern is selected according to a predetermined priority. The video sequence may contain both static patterns and embedded film source patterns. The state machine discerns the presence of the embedded film source patterns notwithstanding the presence of the static patterns.

Owner:PIXELWORKS SEMICON TECH SHANGHAI CO LTD +1

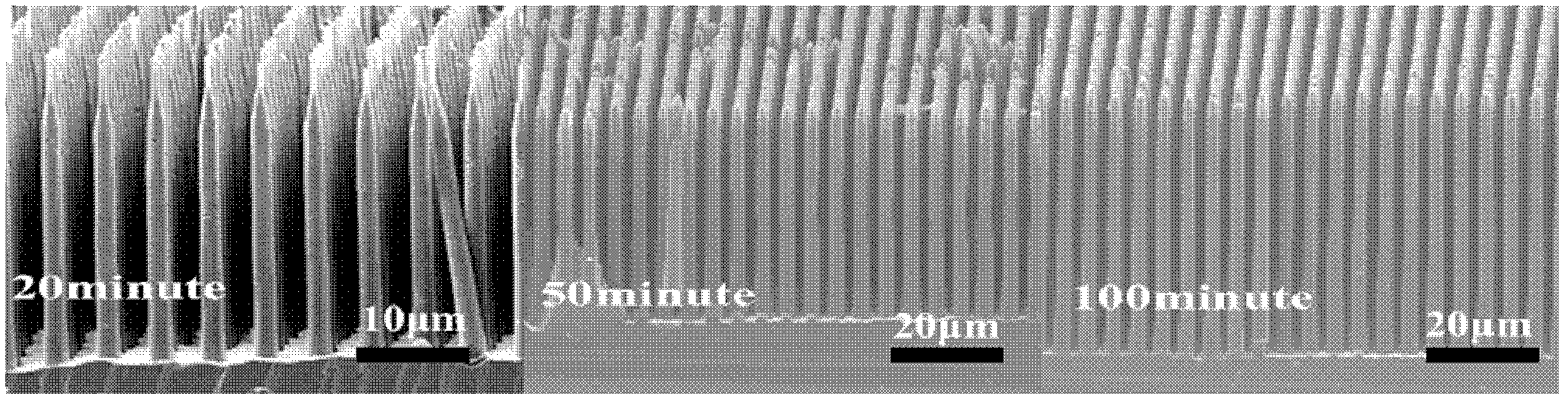

Preparation method of silicon micro/nanometer line array with controllable dimension

InactiveCN102556949ASimple processLow costDecorative surface effectsChemical vapor deposition coatingEtchingCrystal orientation

The invention discloses a preparation method of a silicon micro / nanometer line array with a controllable dimension. The preparation method is characterized in that a silicon chip is used as a substrate, a sample A is obtained through taking out the silicon chip to be dried after the surface of the silicon chip is cleaned, photoresist is coated on the surface of the sample A in a spiral way, and a photoresist layer is baked; a contact type mask is prepared according to the pattern types of the silicon micro / nanometer line array, the mask is utilized for realizing the exposure on the photoresist layer to obtain a sample B, the sample B is developed in developing liquid for 4 to 6 minutes, and exposed photoresist is washed away to obtain a sample C; a gold film with the thickness being 20 to 50 nanometers is coated on the surface of the sample C to obtain a sample D; the sample D is placed into acetone to remove the photoresist and the gold on the sample, and the silicon chip in contact with the gold, i.e. a sample E is obtained; and the sample E is soaked into etching liquid to carry out gold catalysis chemical etching, and the silicon micro / nanometer line array is obtained after the etching completion. The preparation method provided by the invention can be used for obtaining the silicon micro / nanometer line array with the controllable diameter and length and the uniform crystal orientation so that the silicon micro / nanometer line array can realize the practical application to devices.

Owner:HEFEI UNIV OF TECH

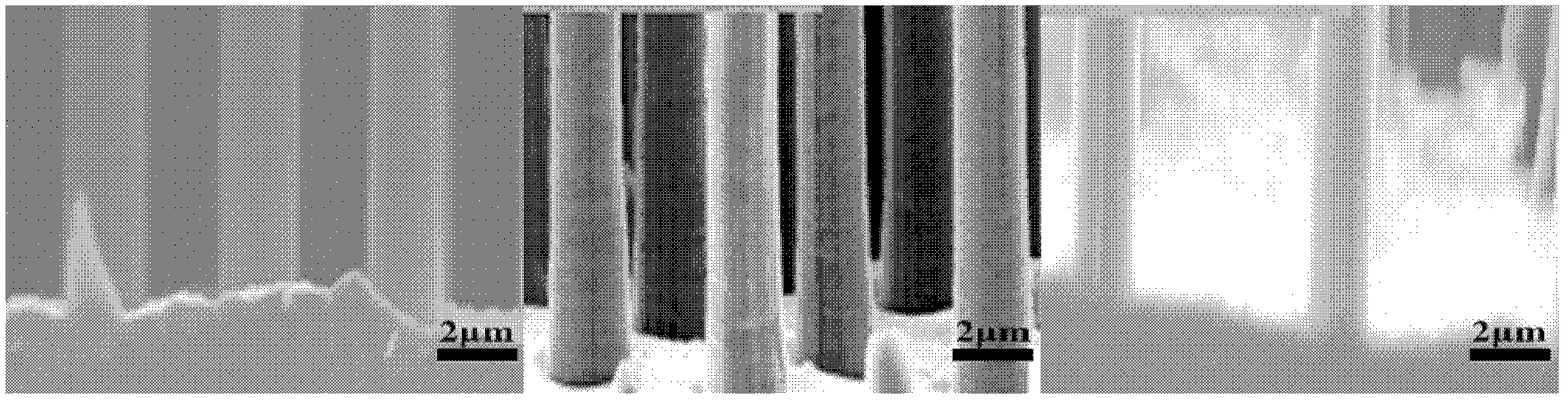

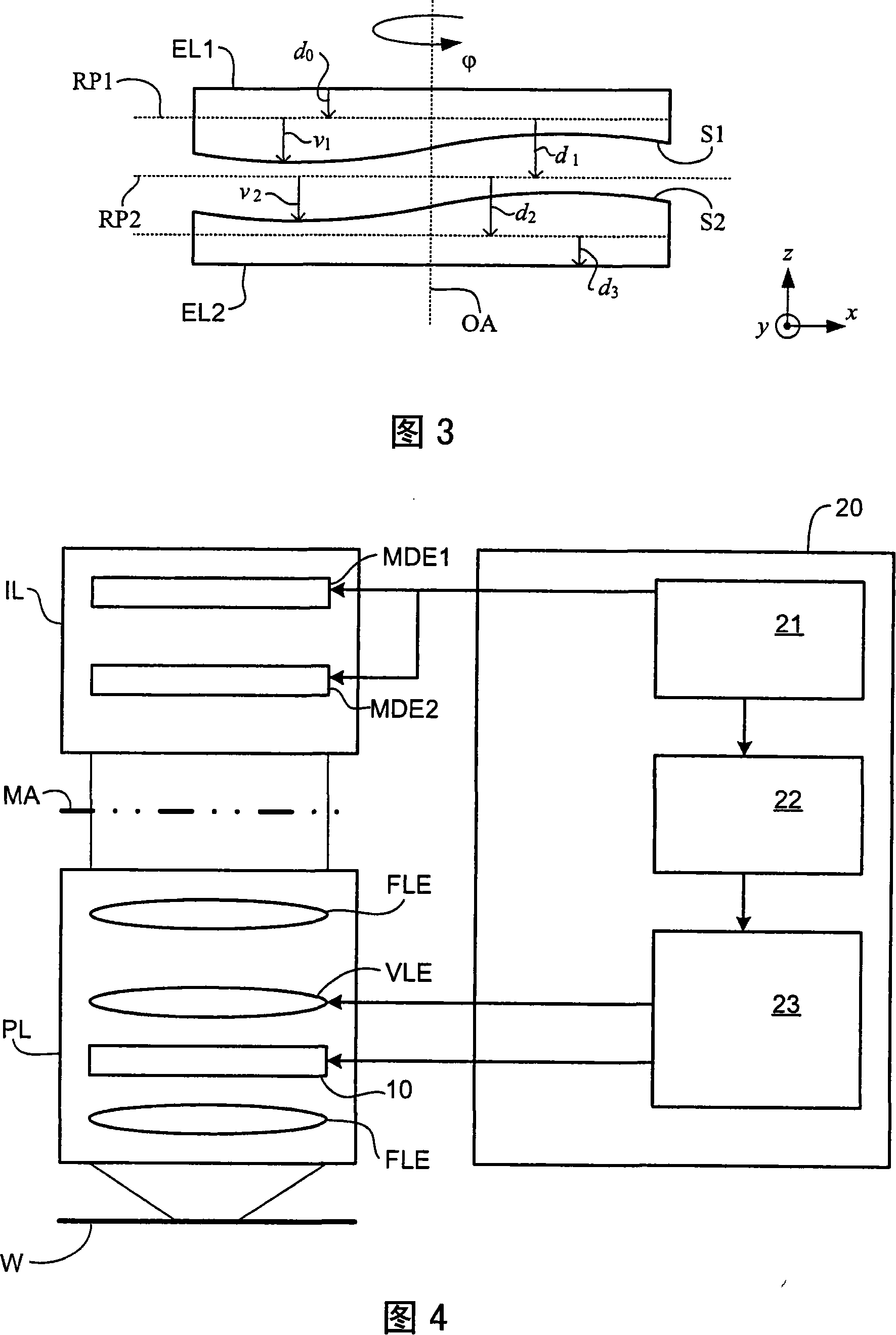

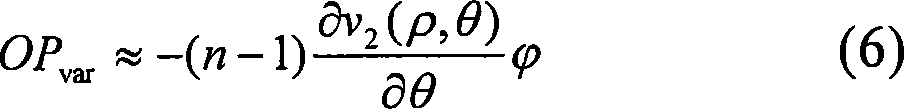

Lithographic apparatus, aberration correction device and device manufacturing method

ActiveCN101109909APhotomechanical exposure apparatusMicrolithography exposure apparatusLithographic artistPhase shifted

The invention provides a photolithographic equipment, an aberration correction device and a device manufacturing method. An aberration correcting device usable in photolithography includes two elements that are relatively rotatable about an optical axis. One surface of each element has a spherical form that can be described by higher order Zernike polynomials. When these two surfaces are rotationally aligned, the device has the optical effect of a flat plate. If there is a small relative rotation between these two elements, the effect of the device is a phase shift that can be described by the derivative in spherical form. Correction means can be used to correct aberrations caused by lens heating, especially for illumination modes and pattern types that lead to strongly off-axis localized pupil filling in projection systems.

Owner:ASML NETHERLANDS BV

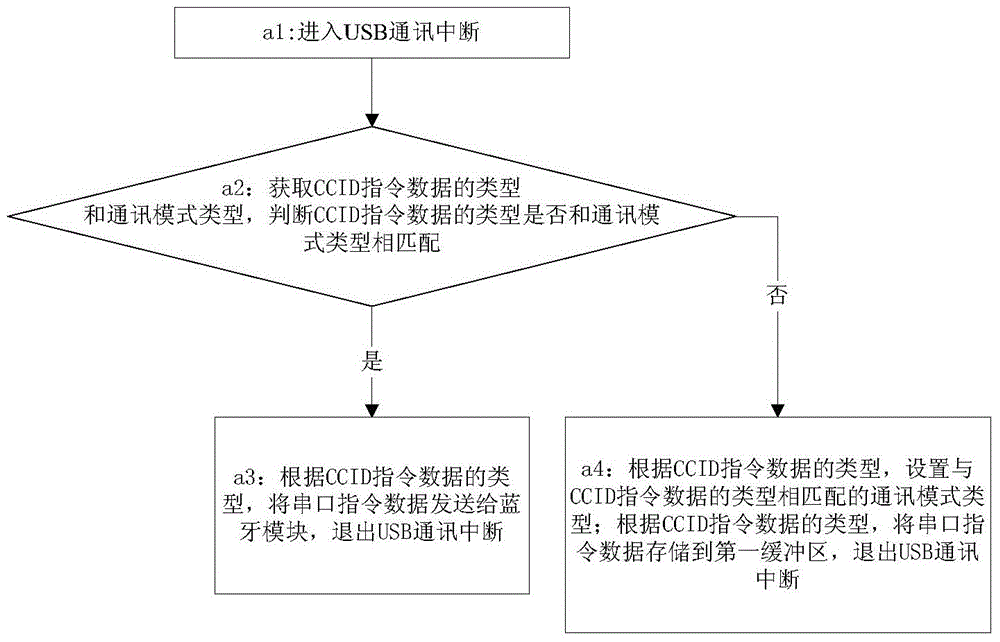

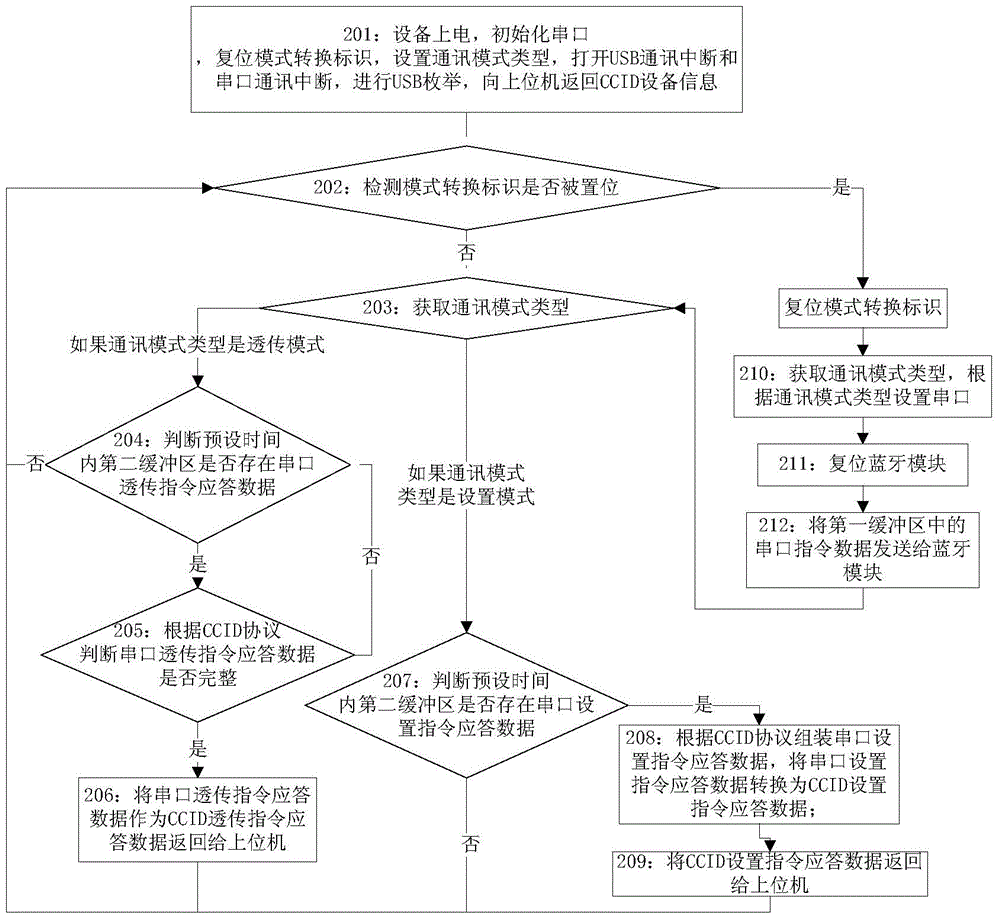

CCID equipment with Bluetooth interface and working method of CCID equipment

ActiveCN105005540ARealize multi-interface communicationImprove developmentElectric digital data processingBluetoothUSB

The invention provides CCID equipment with a Bluetooth interface and a working method of the CCID equipment. The working method comprises the following steps: detecting whether a communication mode type is changed or not; if not, returning CCID instruction responding data back to an upper computer according to the communication mode type and data in a second buffering region; if so, resetting a Bluetooth module and returning the CCID instruction responding data back to the upper computer; after acquiring the CCID instruction data by a USB module, determining whether the type of the CCID instruction data is matched with the communication mode type or not; if so, transmitting serial port instruction data to the Bluetooth interface according to the type of the CCID instruction data; otherwise, setting a matched communication mode type according to the type of the CCID instruction data and storing the serial port instruction data into a first buffering region; and after acquiring the serial port instruction responding data by a Bluetooth module, storing the serial port instruction responding data to the second buffering region.

Owner:FEITIAN TECHNOLOGIES