Delay lock loop circuit

A delay-locked loop and circuit technology, applied in the direction of automatic control of electrical components and power, can solve the problem that the delay-locked loop circuit cannot be adjusted automatically, and achieve the effect of reducing the difficulty of design and avoiding trouble.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

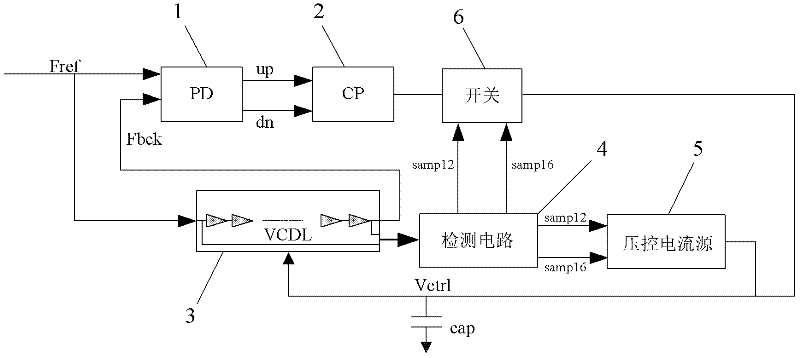

[0023] Specific embodiments of the present invention will be described in detail below in conjunction with the accompanying drawings.

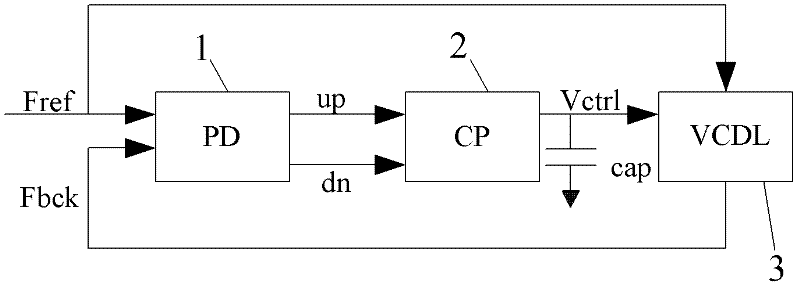

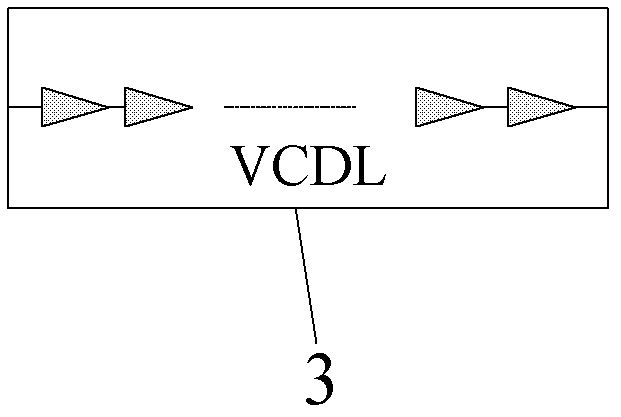

[0024] like image 3 As shown, the delay locked loop circuit of the present invention includes a phase comparator (PD) 1 for comparing the phase relationship between the input clock signal Fref and the feedback signal Fbck to generate a leading signal up and a lagging signal dn. and a charge pump (CP) 2 controlled by the hysteresis signal dn, a filter capacitor cap connected to the output terminal of the charge pump 2 and used to provide the DC voltage signal, and a filter capacitor cap used to respond to the DC voltage signal to process the input clock signal Fref In addition to delaying the voltage-controlled delay chain (VCDL) 3 that generates the feedback signal Fbck, it also includes a detection circuit 4, a voltage-controlled current source 5 and a switch 6, wherein,

[0025] The detection circuit 4 is configured to judge the magnitude ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com