NRZI (non return to zero invert) decoding parallel design circuit

A technology for designing circuits and decoding circuits, applied in the field of decoding circuits, can solve problems such as increasing circuit power consumption, and achieve the effects of reducing power consumption and clock frequency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0012] specific implementation plan

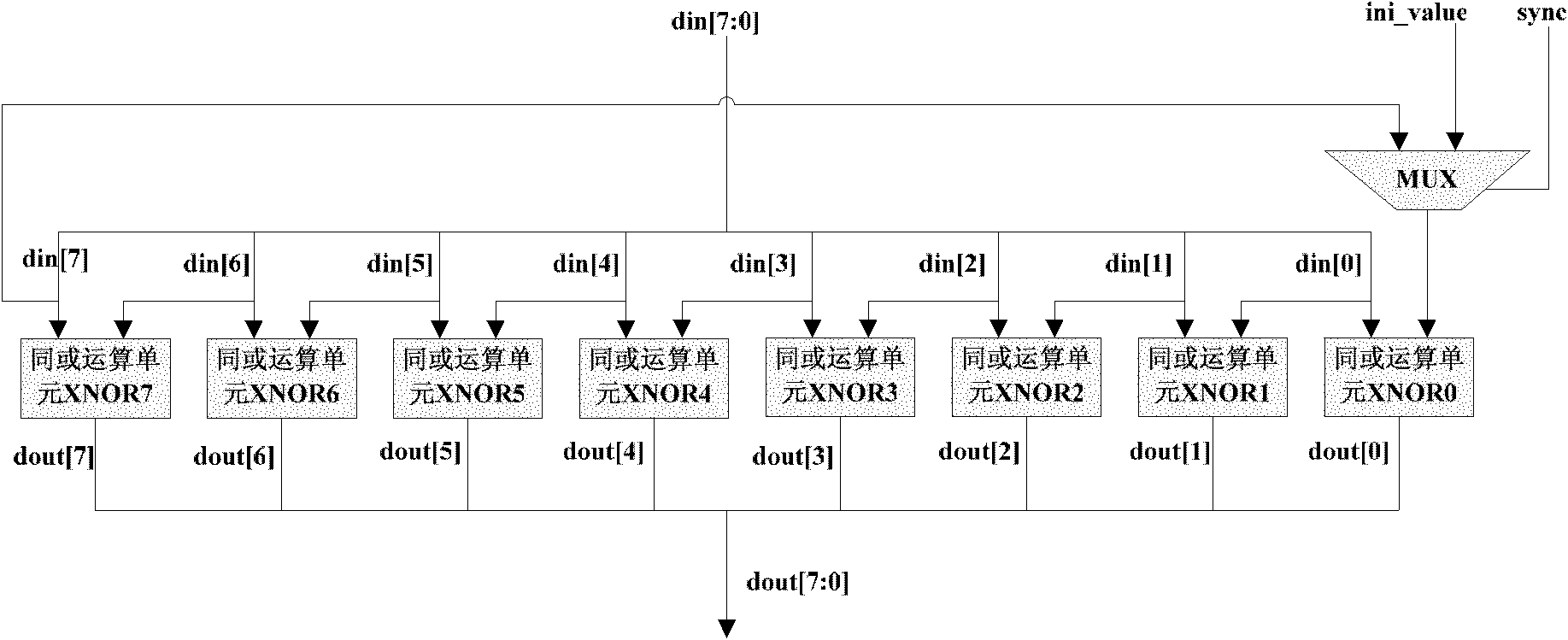

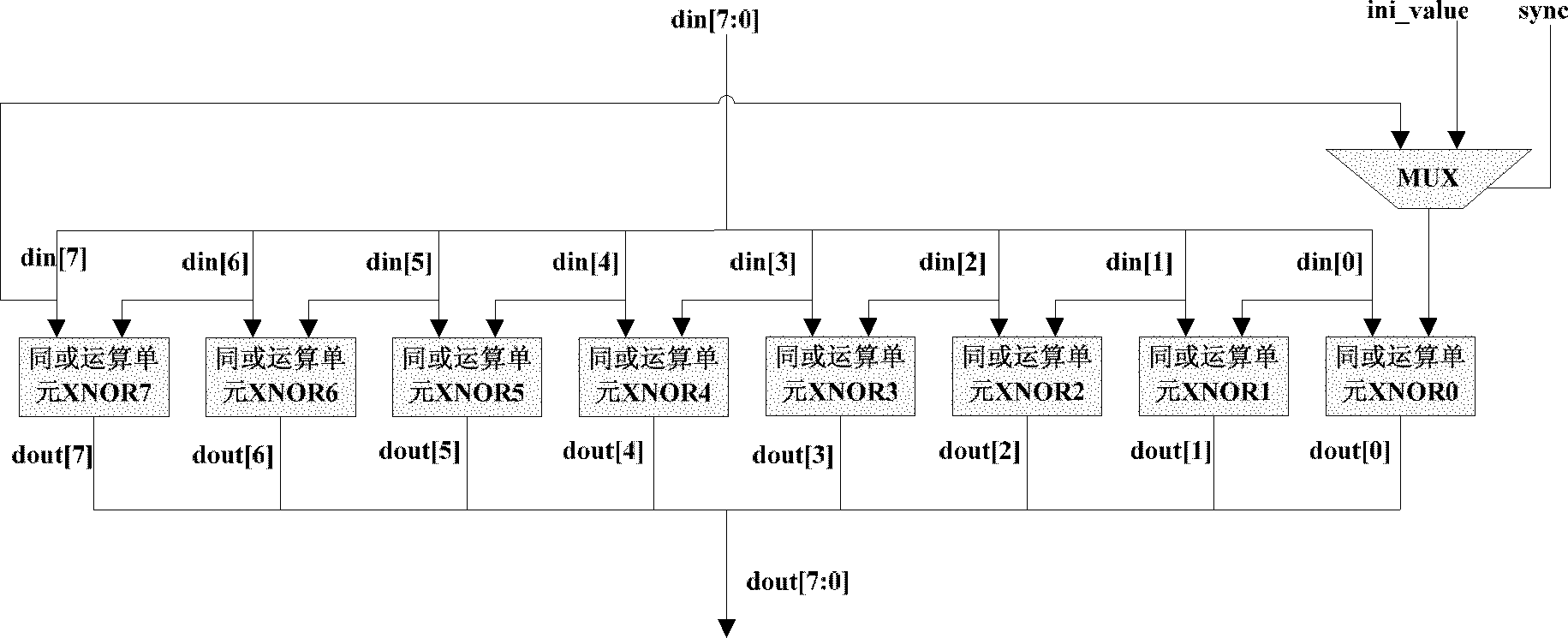

[0013] The following is attached figure 1 The contents proposed by the present invention are described in detail. figure 1 It is the circuit structure diagram of the present invention, as shown in the figure, the eight same-or operation units are respectively the same-or operation unit XNOR0, the same-or operation unit XNOR1, the same-or operation unit XNOR2, the same-or operation unit XNOR3, and the same-or operation unit XNOR4 , the same-or operation unit XNOR5, the same-or operation unit XNOR6 and the same-or operation unit XNOR7. The two-to-one selector MUX inputs the initial value of the NRZI decoding operation under the control of the sync signal, and the eight exclusive OR operation units XNOR sample the eight-bit data input from the outside, simultaneously perform the same OR operation and generate the operation result.

[0014] When there is data and signal transmission, the circuit first judges whether the current byte of data ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com