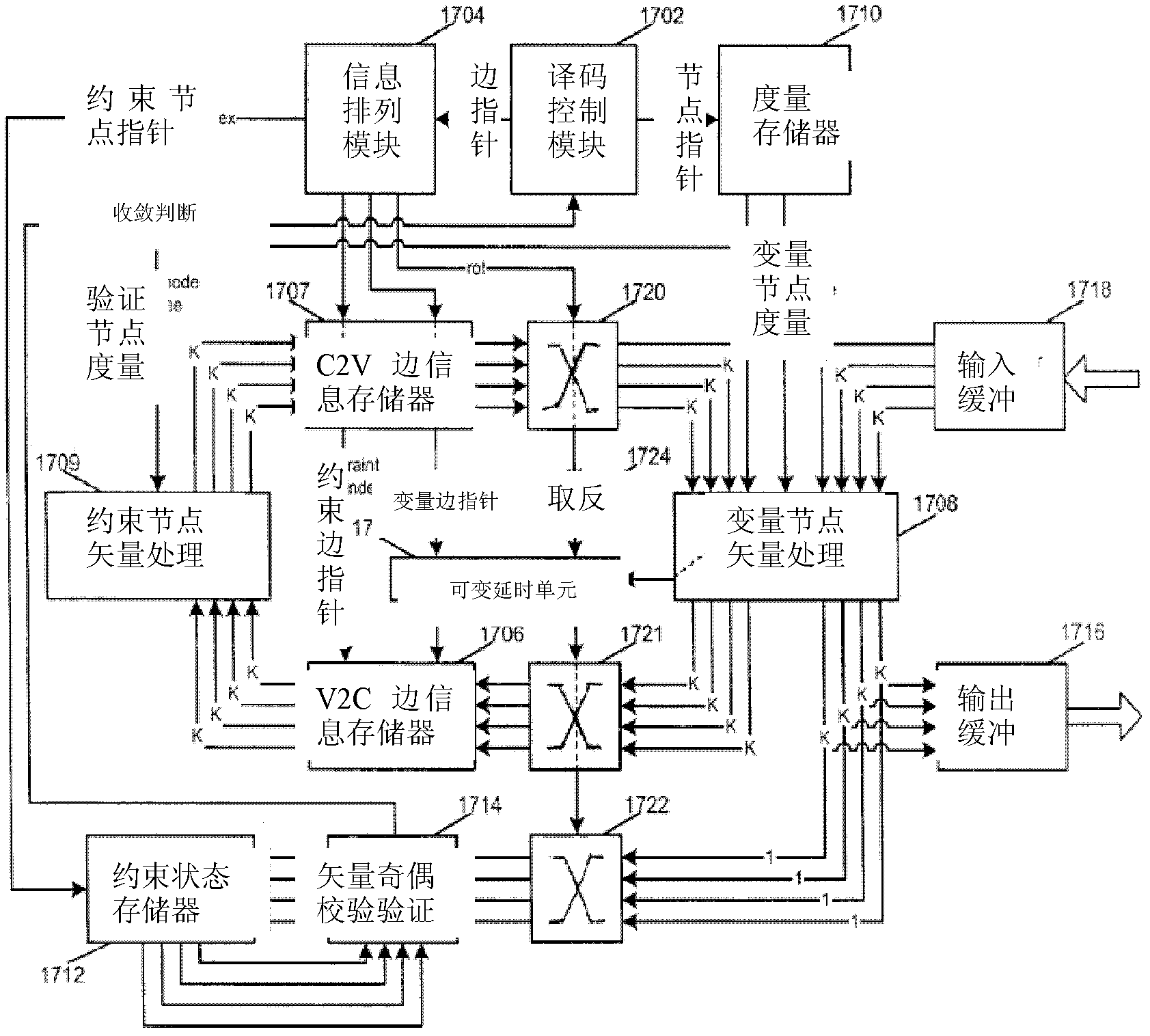

LDPC (low density parity check) decoder

A decoder and memory technology, applied in the field of encoding and decoding error-correcting codes, can solve problems such as high complexity, slow speed, and complicated processing flow control, and achieve the effect of reducing scale and complexity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0030] First, explain the basis of the present invention, block code and block matrix:

[0031] (1) Block code

[0032] Usually block codes can be expressed as (n, k), where n is the length of a code group, k is an information bit, and n-k is a parity bit. When encoding, the generator matrix G is usually used, which is a k×n matrix; the input information is E, which is a 1×k matrix (that is, a row vector), and the code group after encoding is B, which is 1×n matrix. B=E·G, give an example: k=4, n=7; G is a 4×7 matrix

[0033] G = 1 0 0 0 1 1 1 0 1 0 ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More