Discrete transceiver circuit suitable for high-speed 1553 bus

A transceiver circuit and bus technology, applied in the direction of bus network, data exchange through path configuration, etc., can solve the problems of increased system development cost, increased development cycle, poor flexibility, etc., to achieve strong scalability, good versatility, Cost and time savings

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0031] The present invention will be further described below in conjunction with drawings and embodiments.

[0032] The present invention adopts the method of building discrete devices, and is divided into two parts: a transmitter and a receiver.

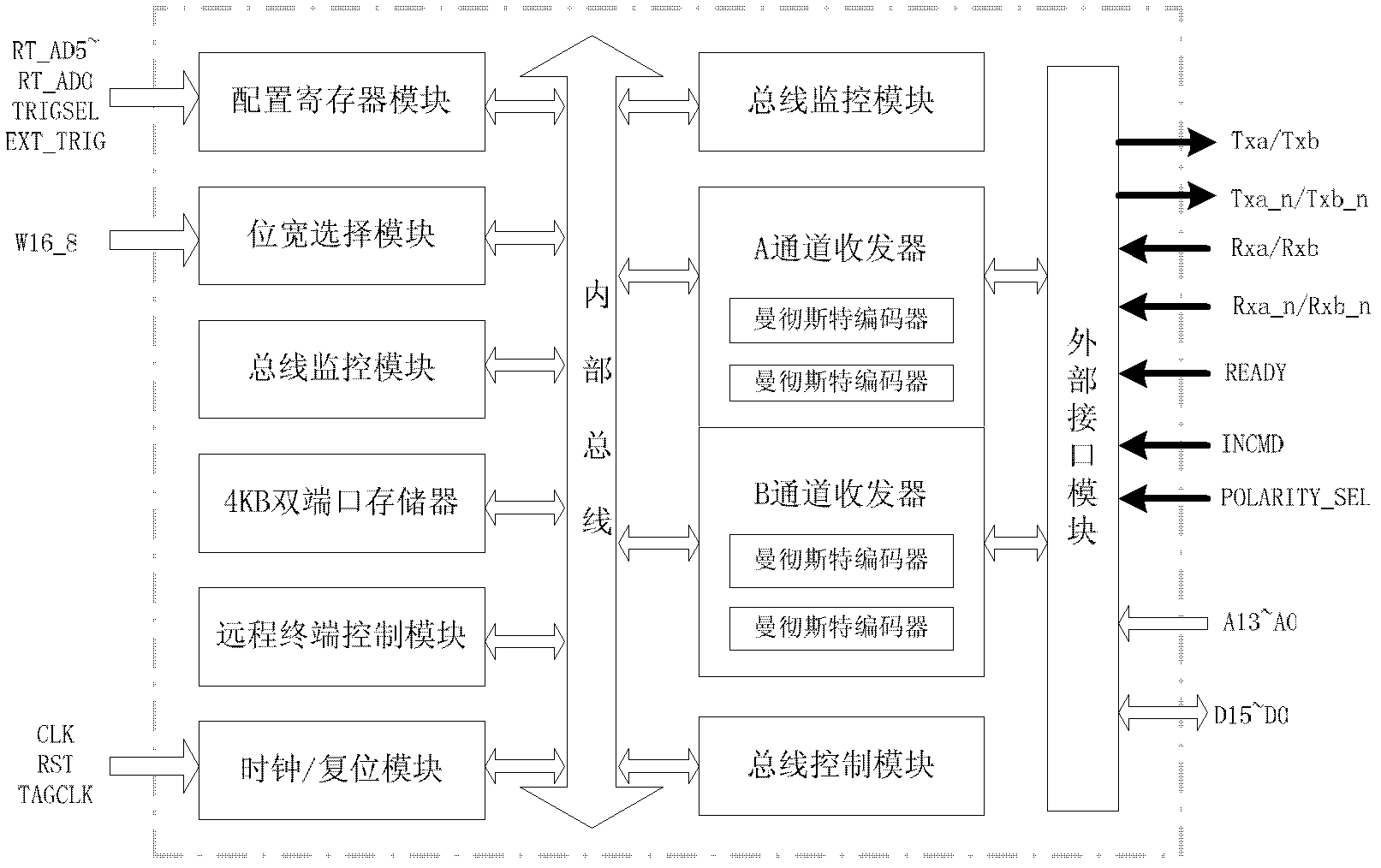

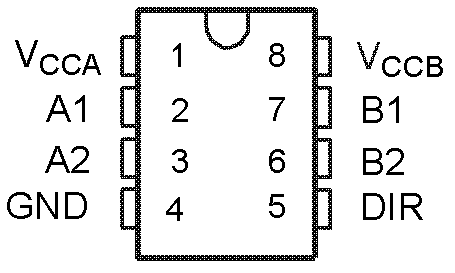

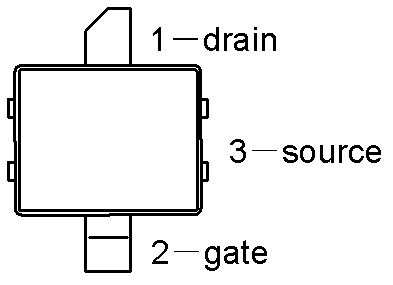

[0033] The transmitter is connected with the protocol processor to complete the transmission of high-speed Manchester code. It consists of a bidirectional voltage conversion driver with three-state output, LDMOS (or NMOS) and resistors / capacitors with certain resistance and capacitance. The structural block diagram of the high-speed protocol processor circuit, and the circuit pin diagram of SN74LVC2T45 and LDMOS-BLF6G21-10G are respectively shown in figure 1 , figure 2 with image 3 .

[0034] Such as figure 1 As shown, the high-speed protocol processor circuit includes: a dual-channel communication protocol processing module, an external interface logic module, a configuration register module, a storage management module, a bi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com