Semiconductor device and manufacturing method thereof

A manufacturing method and semiconductor technology, which is applied in the direction of semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve problems such as not being able to meet the stress requirements of devices, and achieve the effects of enhancing stress, increasing stress, and enhancing stress

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

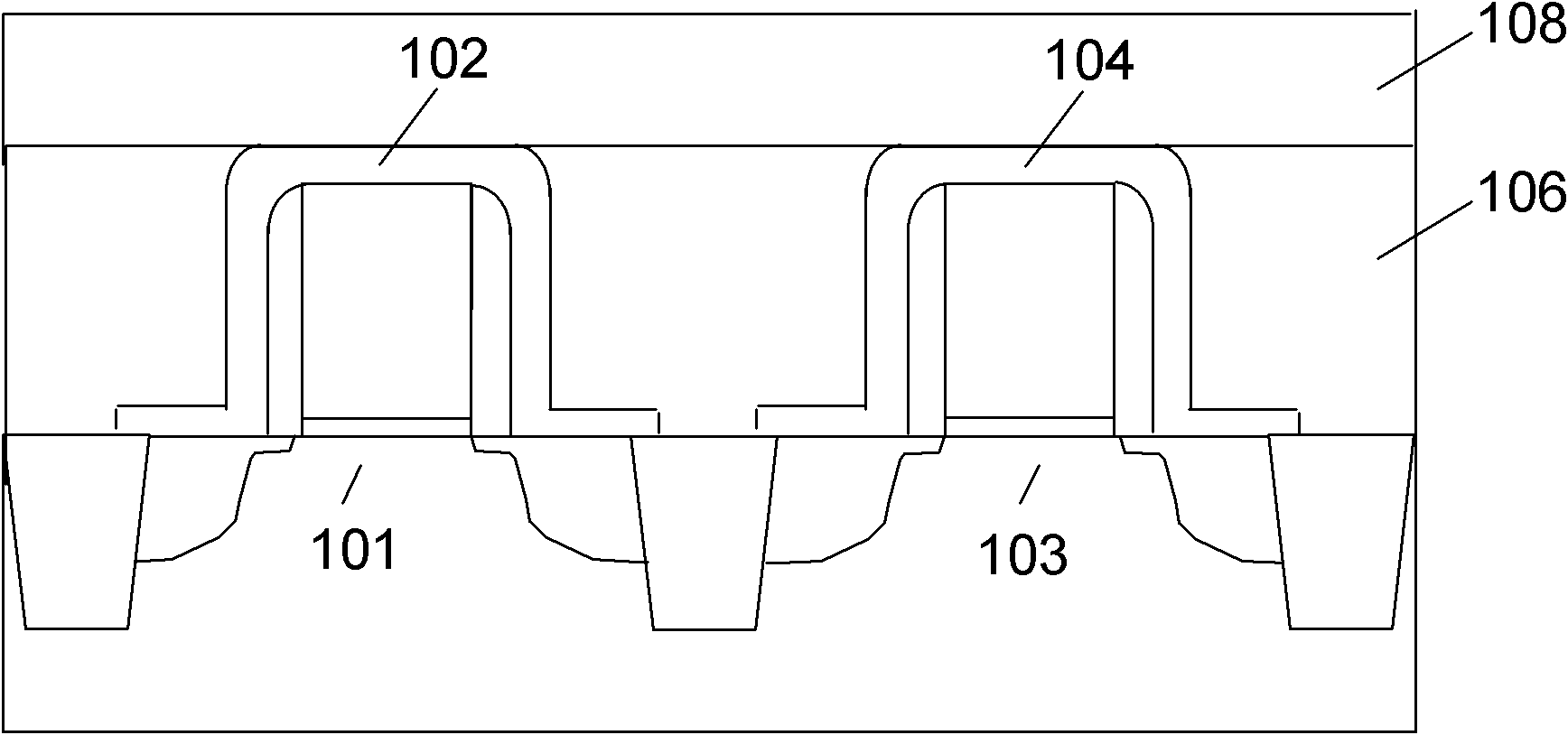

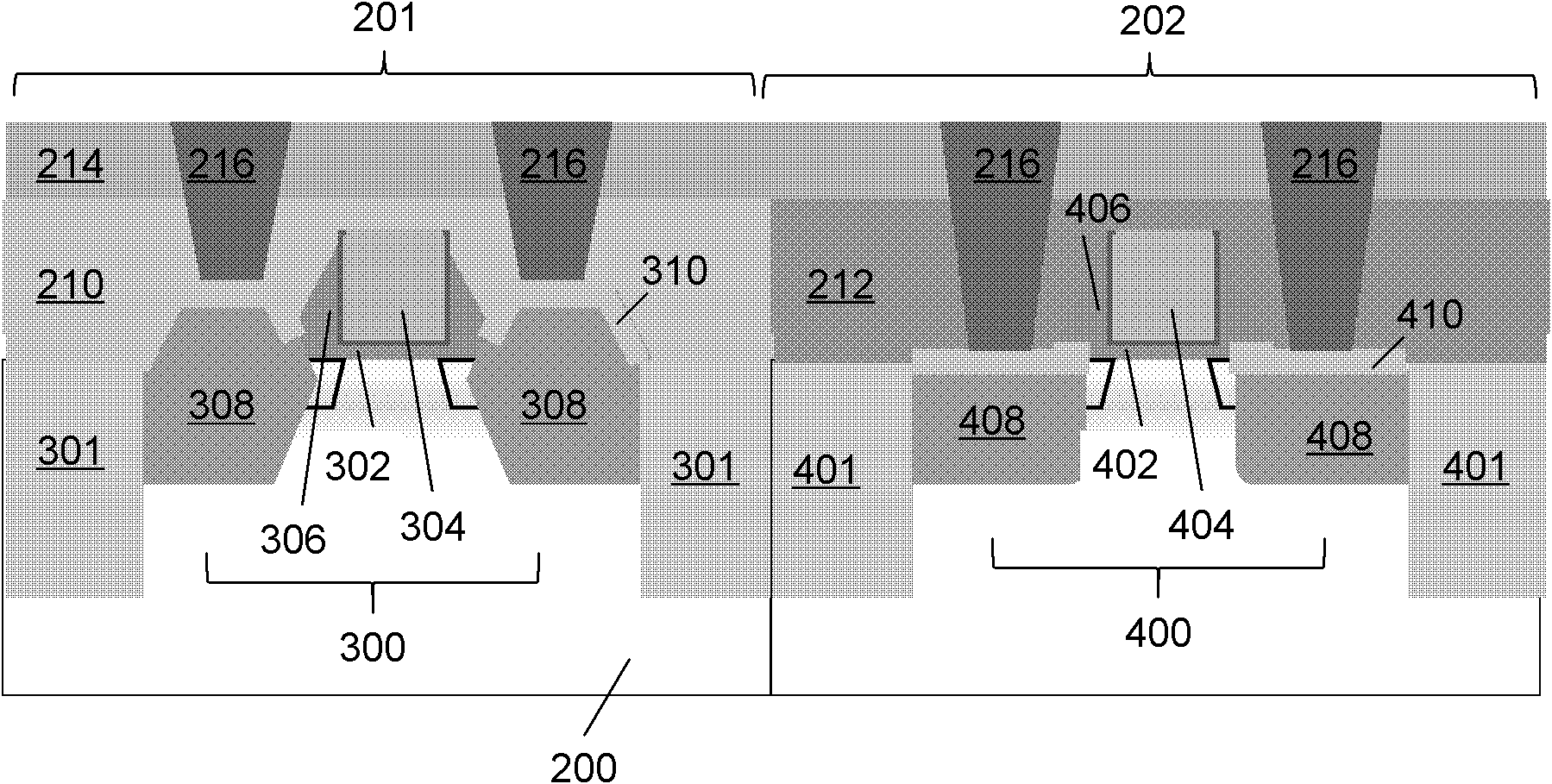

[0075] The following combination Figure 3-Figure 9 The first embodiment of the semiconductor device manufacturing method of the above-mentioned embodiments will be described in detail.

[0076] First, refer to image 3 , in step S11 , providing a substrate 200 including an NMOS region 202 and a PMOS region 201 .

[0077] In this embodiment, the substrate 200 is a silicon substrate, and an N well and a P well can be formed respectively by performing well doping on the substrate, wherein the N well will be used to form a PMOS device, and the P well will be used to form a PMOS device. It will be used to form NMOS devices, therefore, in this embodiment, the N well can be understood as the PMOS region 201 , and the P well can be understood as the NMOS region 202 . At the same time, isolation regions 301 and 401 are formed on the substrate 200, and the isolation regions may include silicon dioxide or other materials that can separate active regions of devices.

[0078] Then, ref...

no. 2 example

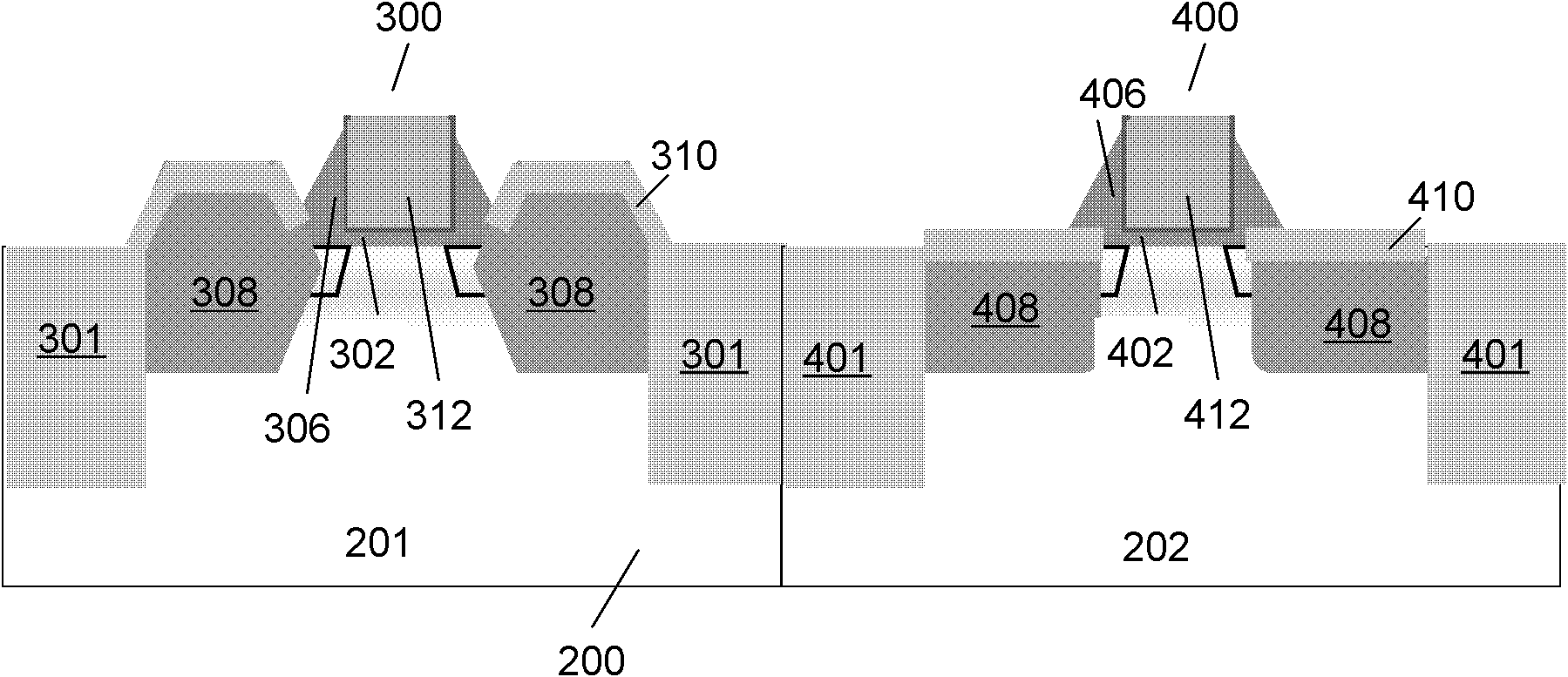

[0095] The first embodiment in which the semiconductor device of the present invention is formed by using the gate-last process has been described in detail above, and only the differences between the second embodiment and the first embodiment will be described below. Parts not described should be considered to be performed using the same steps, methods or processes as those in the first embodiment, so details will not be repeated here.

[0096] First, refer to Figure 10 , in step S21 , providing a substrate 200 including an NMOS region 202 and a PMOS region 201 . It is the same as step S11 in the first embodiment, and will not be repeated here.

[0097] Then, refer to Figure 10 , in step S22 , the NMOS device 400 in the NMOS region 202 and the PMOS device 300 in the PMOS region 201 are provided. Only the step of forming the gate stack is different from the step S12 of the first embodiment, and other steps are the same, and will not be repeated here. In this embodiment, ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More