Address mapping method and device of FFT (Fast Fourier Transform) of parallel branch butterfly unit

A butterfly unit and address mapping technology, applied in the field of communication, can solve the problem of inability to guarantee the continuity and effectiveness of FFT operations, and achieve the effect of reducing implementation cost and complexity, and ensuring continuity and effectiveness.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

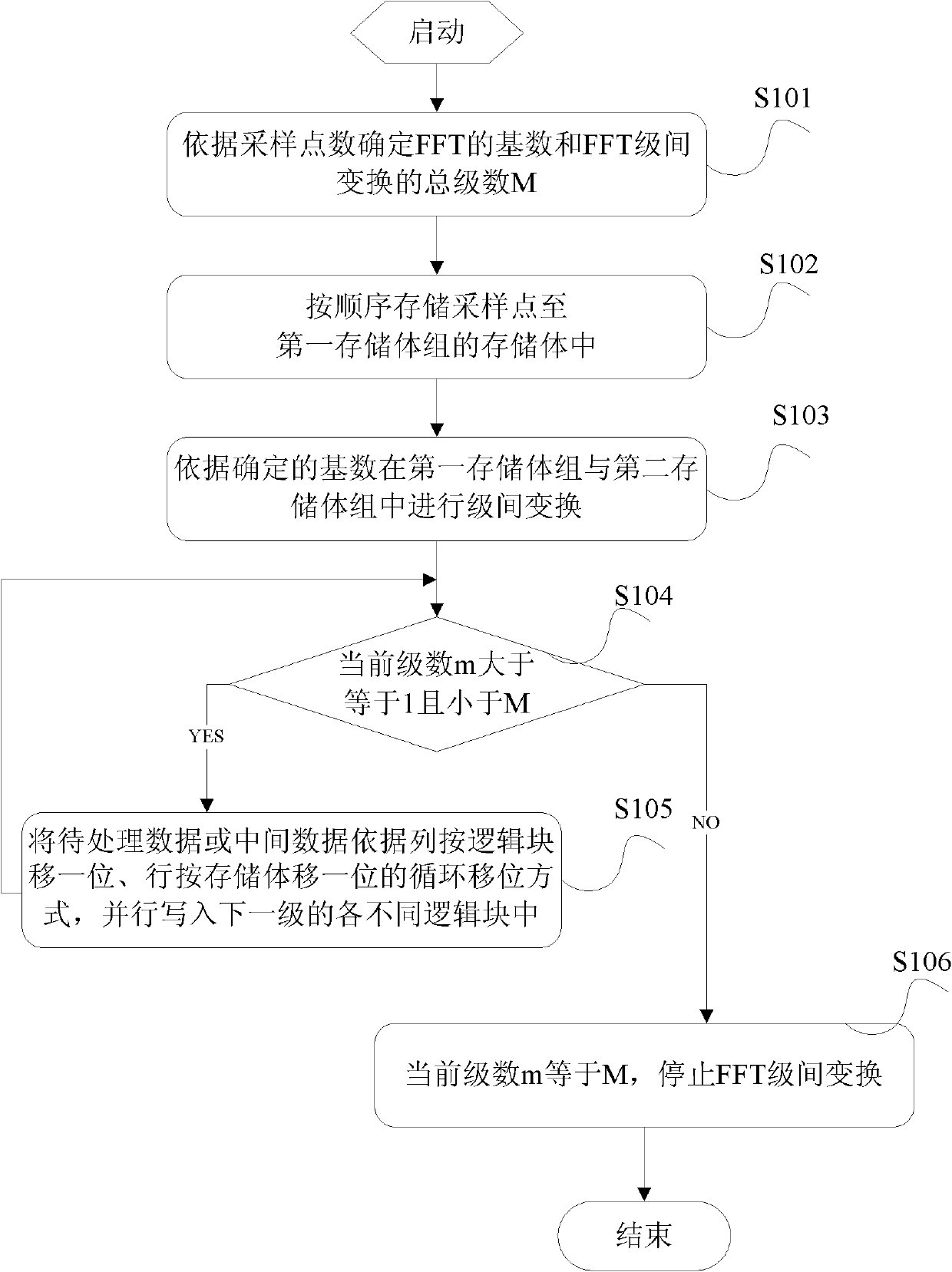

[0047] Please refer to the attached figure 1, is a flow chart of the address mapping method of the FFT of a parallel branch butterfly unit disclosed by the present invention, mainly comprising the following steps:

[0048] Step S101 , according to the number N of sampling points of the FFT, determine the radix D of the FFT, and the total number of stages M of the FFT inter-stage transformation corresponding to the radix D.

[0049] In the execution step S101, the FFT of the radix D is the radix of the FFT butterfly unit, and the value of D is related to the number N of sampling points. The total number of stages M of the FFT interstage transformation corresponding to the base D is related to the base D and the number N of sampling points. The bases in the present invention mainly include: base 8, base 4 and base 2. Generally, the larger the base, the higher the efficiency. Wherein, the number of sampling points can be extracted according to DIF, or can be extracted according...

Embodiment 2

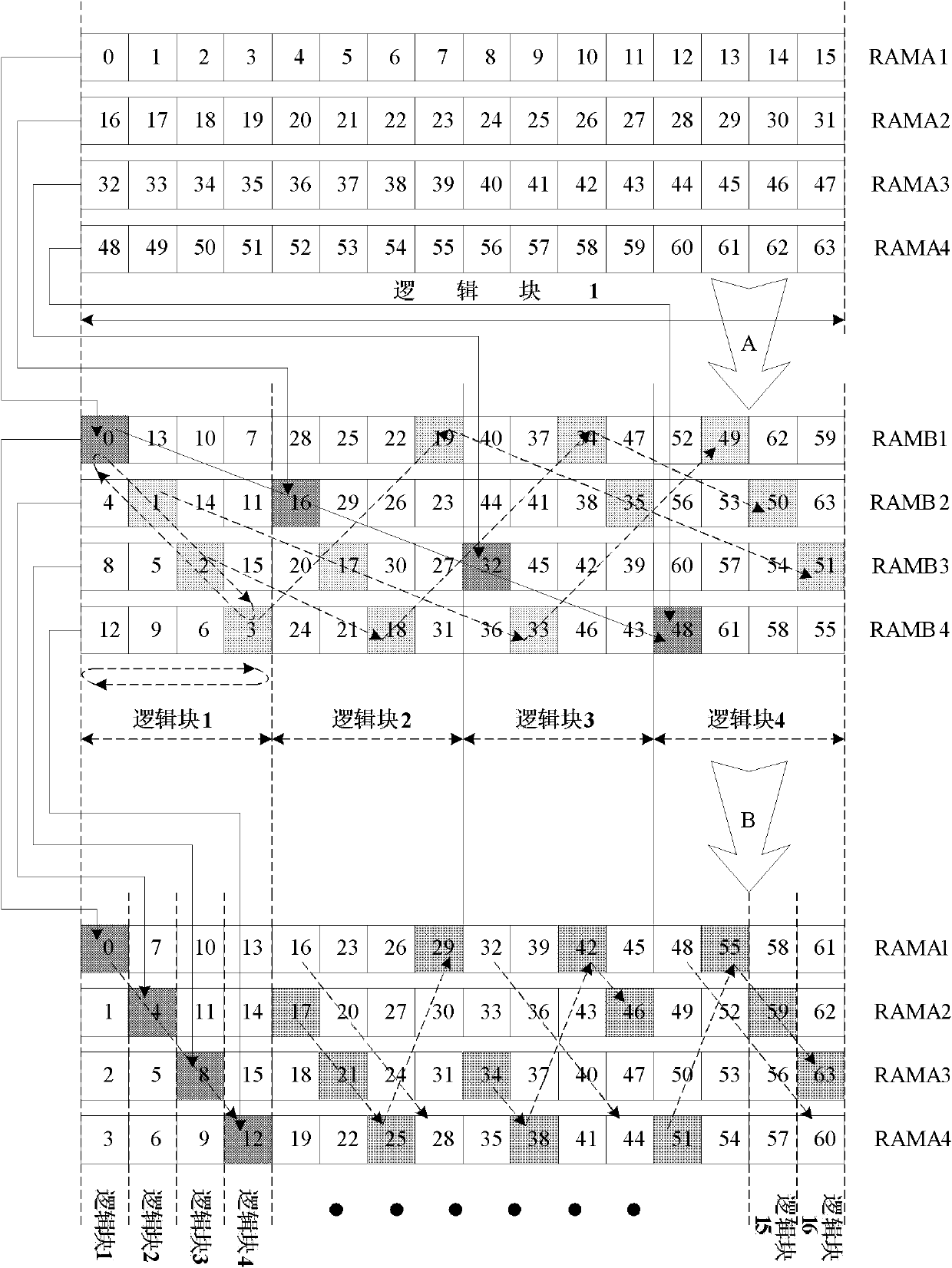

[0080] Please refer to the attached figure 2 , is a schematic flowchart of a parallel branch butterfly unit FFT 64 point DIF4 address conversion shown in the present invention, and the specific conversion process is as follows:

[0081] Such as figure 2 As shown, a total of 64 points are sampled (extracted) according to the frequency extraction method according to DIF, and the operation is performed according to the base 4 of FFT, that is, the value of D is 4, and the value of N is 64. Thus, it can be drawn according to formula (1) that the total number of stages M of the FFT is 3, and the intermediate stages of the FFT transformation of the 64-point DIF4 are 2 stages successively, as figure 2 A and B shown in , wherein, A represents the first-level transformation memory bank group, and B represents the second-level transformation memory bank group.

[0082] Such as figure 2 As shown, the two memory bank groups in the two-level transformation are:

[0083] Group 1 incl...

Embodiment 3

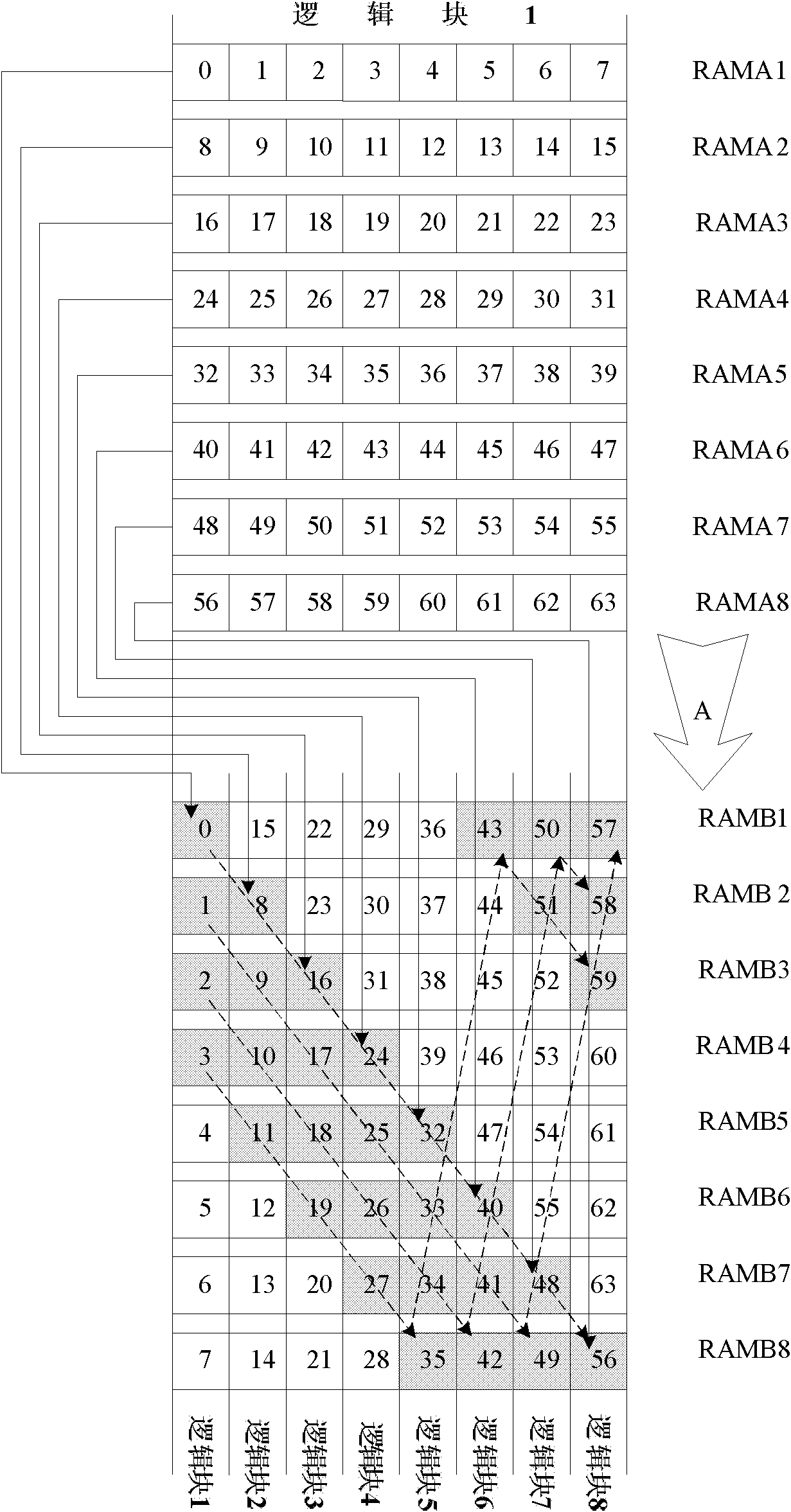

[0096] On the basis of the disclosure of the above-mentioned embodiments of the present invention, as image 3 As shown, the present invention also discloses a schematic flow chart of parallel branch butterfly unit FFT 64-point DIF8 address conversion, and the specific conversion process is as follows:

[0097] Such as image 3 As shown, a total of 64 points are sampled (extracted) according to the method of frequency extraction according to DIF, and the operation is performed according to the base 8 of FFT, that is, the value of D is 8, and the value of N is 64. Thus, it can be drawn according to formula (1) that the total number of stages M of the FFT is 2, and the intermediate stages of the FFT transformation of the 64-point DIF4 are 1 stage successively, as image 3 The A shown in represents the first-level transformation.

[0098] Such as image 3 As shown, the two memory bank groups in the two-level transformation are:

[0099] Group 1 includes, RAMA1, RAMA2, RAMA3, ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More