Manufacturing method of top-gate oxide thin-film transistor

A technology of oxide film and manufacturing method, which is applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

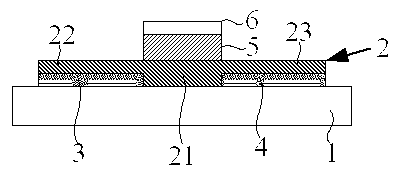

[0040] like figure 1 As shown, a top gate oxide thin film transistor of an embodiment includes a substrate 1, a source 3 and a drain 4 formed on the substrate 1, an oxide semiconductor formed on the source 3, the drain 4 and the substrate 1 layer 2, a gate insulating layer 5 on the oxide semiconductor layer 2, and a gate 5 on the gate insulating layer 5, the oxide semiconductor layer 2 includes a channel region 21 corresponding to the gate region, and a channel A region 22 and a region 23 on both sides of the region 21 are respectively in contact with the source 3 and the drain 4, and the channel region 21 is located between the source 3 and the drain 4, wherein the gate 6 and the insulating layer 5 and the channel region 21 can be form self-alignment.

[0041] The manufacturing method of the top gate oxide thin film transistor of this embodiment includes the following steps:

[0042] 1.1. The substrate 1 can be glass, quartz, silicon wafer or other flexible substrates such ...

Embodiment 2

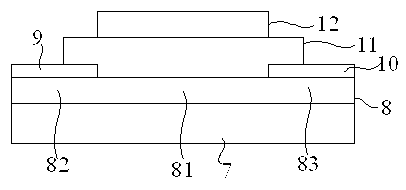

[0053] like figure 2 As shown, the top gate oxide thin film transistor includes a substrate 7, an oxide semiconductor layer 8 formed on the substrate 7, a source 9 and a drain 10 formed on the oxide semiconductor layer 8, a source 3 and a drain formed on the 4 and the gate insulating layer 11 on the oxide semiconductor layer 8, and the gate 12 formed on the gate insulating layer 11. The oxide semiconductor layer 8 includes a channel region 81 corresponding to the gate region, and the two sides of the channel are respectively contacted. To the regions 82 and 83 of the source and drain electrodes 9 and 10, the channel region is located between the source 9 and the drain 10;

[0054] The manufacturing method of the top gate oxide thin film transistor of this embodiment includes the following steps:

[0055] 2.1. The substrate 7 can be glass, quartz, silicon wafer or other flexible substrates such as plastic, stainless steel, etc., and an oxide semiconductor film is deposited on...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Carrier concentration | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More