Metal oxide semiconductor (MOS) transistor and manufacturing method thereof

A technology of a MOS transistor and a manufacturing method, which are applied in the field of MOS transistors and the manufacturing thereof, can solve the problems of increasing the effective thickness of a gate insulating film, affecting the gate resistance value, and being unable to equalize the first dielectric layer 10 .

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0065] refer to Figure 7 As shown, this embodiment provides a method for manufacturing an NMOS transistor, including:

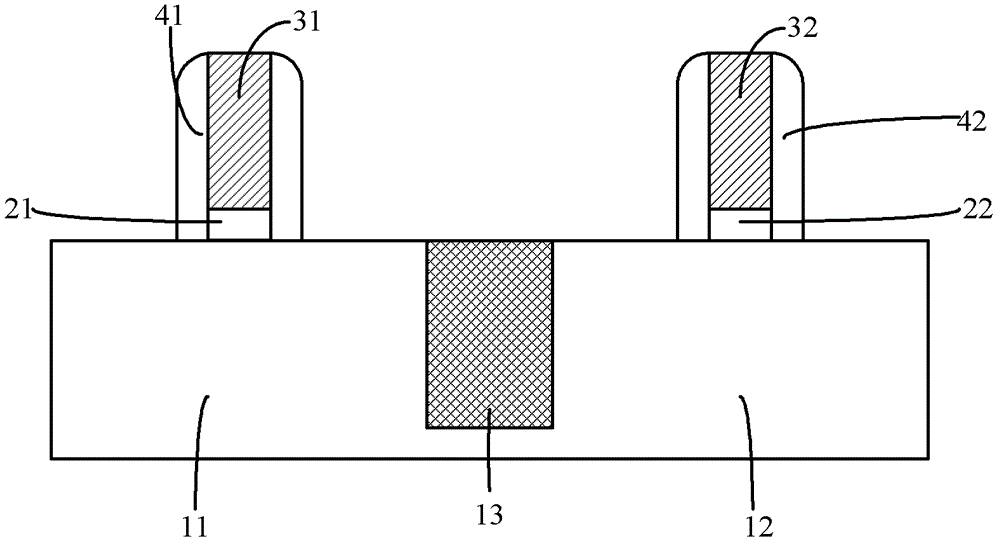

[0066] Step S11, providing a semiconductor substrate, sequentially forming a gate dielectric layer and a dummy gate electrode on the semiconductor substrate, and forming source / drain regions in the semiconductor substrate;

[0067] Step S12, forming a first dielectric layer on the semiconductor substrate, the upper surface of the first dielectric layer being flush with the upper surface of the dummy gate electrode;

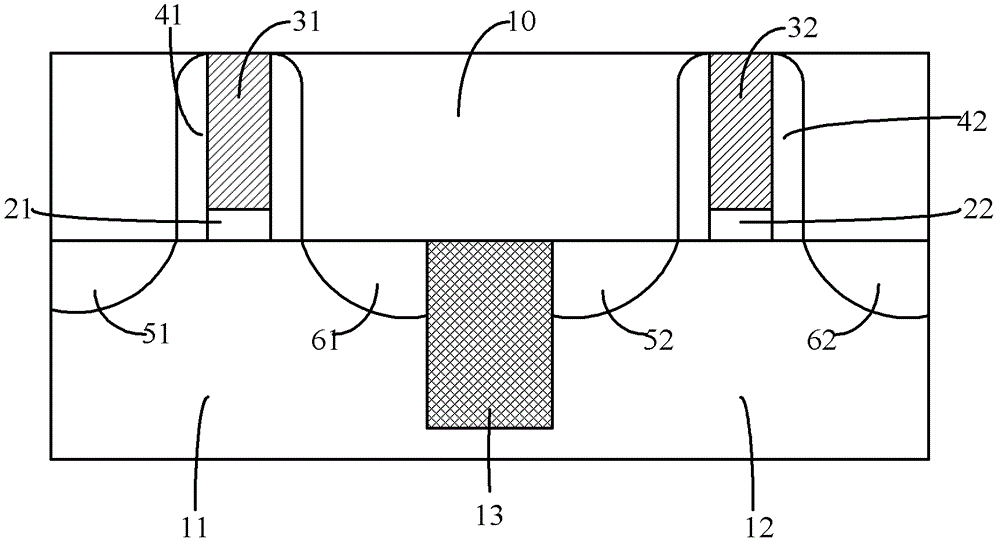

[0068] Step S13, removing the dummy gate electrode, forming a first via hole, forming a second via hole in the first dielectric layer corresponding to the source region, and forming a third via hole in the first dielectric layer corresponding to the drain region hole;

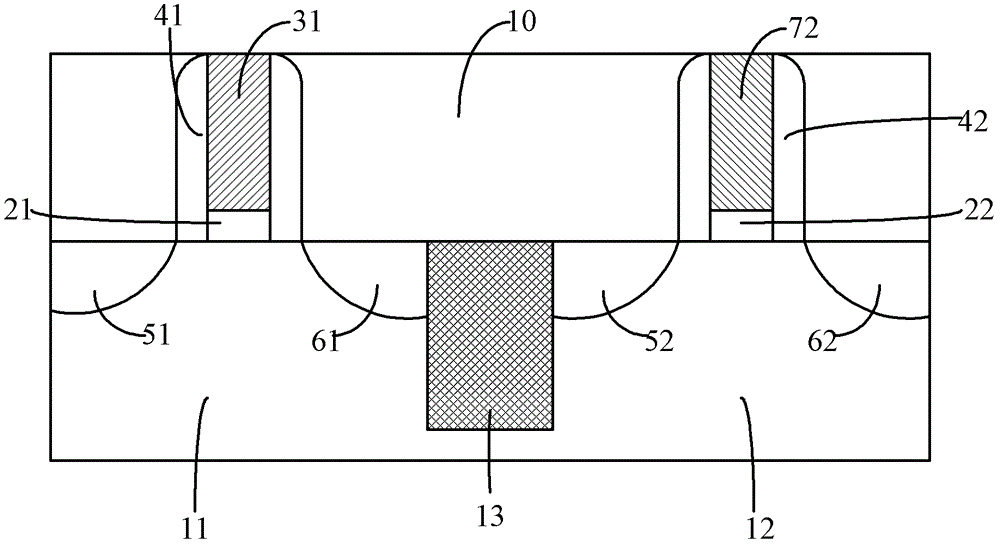

[0069] Step S14, respectively filling the sidewalls and bottoms of the first through hole, the second through hole and the third through hole in sequence with a work function m...

Embodiment 2

[0097] This embodiment provides a method for manufacturing a PMOS transistor, including:

[0098] Provide semiconductor substrates;

[0099] sequentially forming a gate dielectric layer, dummy gate electrodes, and spacers surrounding the gate dielectric layer and dummy gate electrodes on the semiconductor substrate;

[0100] Forming source / drain regions in the semiconductor substrate by using the gate dielectric layer, dummy gate electrodes and sidewalls as masks;

[0101] forming a first dielectric layer on the semiconductor substrate, the upper surface of the first dielectric layer being flush with the upper surface of the dummy gate electrode;

[0102] removing the dummy gate electrode, forming a first through hole, forming a second through hole in the first dielectric layer corresponding to the source region, and forming a third through hole in the first dielectric layer corresponding to the drain region;

[0103] Filling the sidewalls and bottoms of the first through ho...

Embodiment 3

[0116] This embodiment provides a method for manufacturing a CMOS transistor, including:

[0117] A semiconductor substrate is provided, the semiconductor substrate includes a PMOS transistor region and an NMOS transistor region, a first gate dielectric layer and a first dummy gate electrode are sequentially formed on the NMOS transistor region, and a first dummy gate electrode is formed in the NMOS transistor region. A source / drain region; a second gate dielectric layer and a second dummy gate electrode are sequentially formed on the PMOS transistor region, and a second source / drain region is formed in the PMOS transistor region. Forming a CMOS transistor including a dummy gate electrode is well known to those skilled in the art and will not be repeated here.

[0118] A first dielectric layer is formed on the semiconductor substrate, and the upper surface of the first dielectric layer, the upper surface of the first dummy gate electrode and the upper surface of the second dum...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com