Time digital converter based on antifuse field programmable gata array (FPGA) and temperature drift correcting method thereof

A time-digital and temperature-drift technology, applied in analog/digital conversion, code conversion, electrical unknown time interval measurement, etc., can solve the problems of large R&D expenses, long R&D cycle, fixed functions, etc., and achieve low cost and flexible use , the effect of low dead time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0019] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be described in further detail below in conjunction with specific embodiments and with reference to the accompanying drawings.

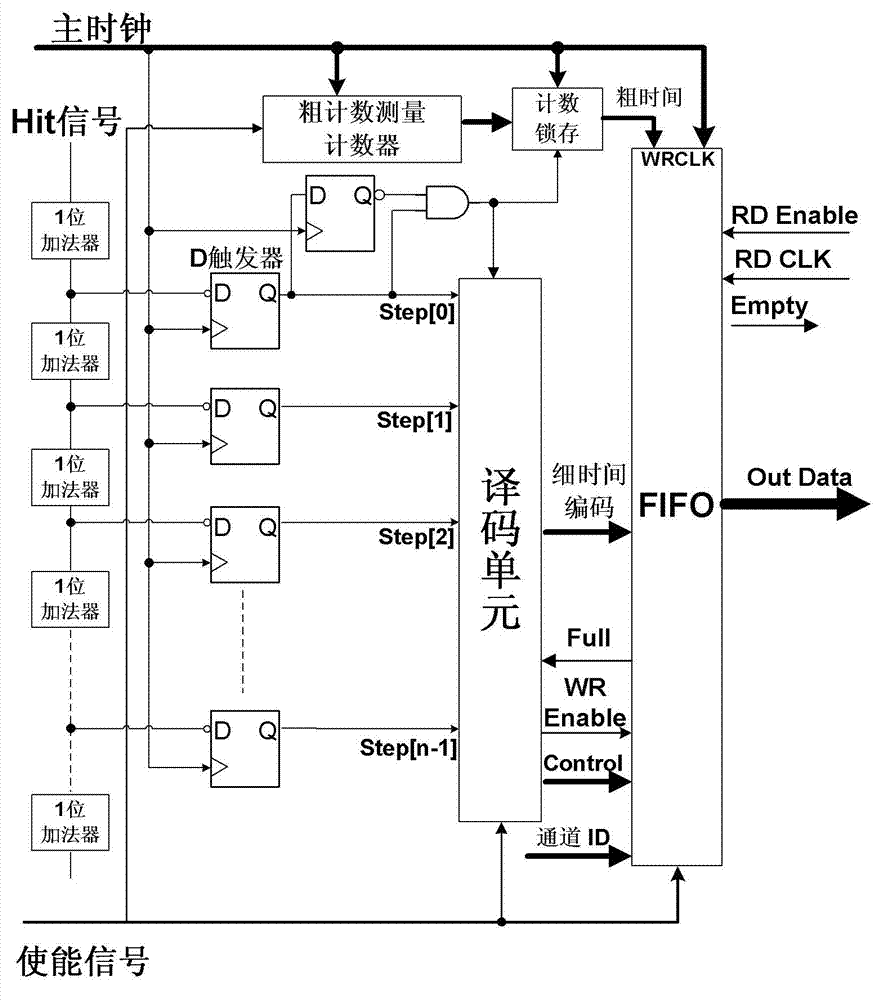

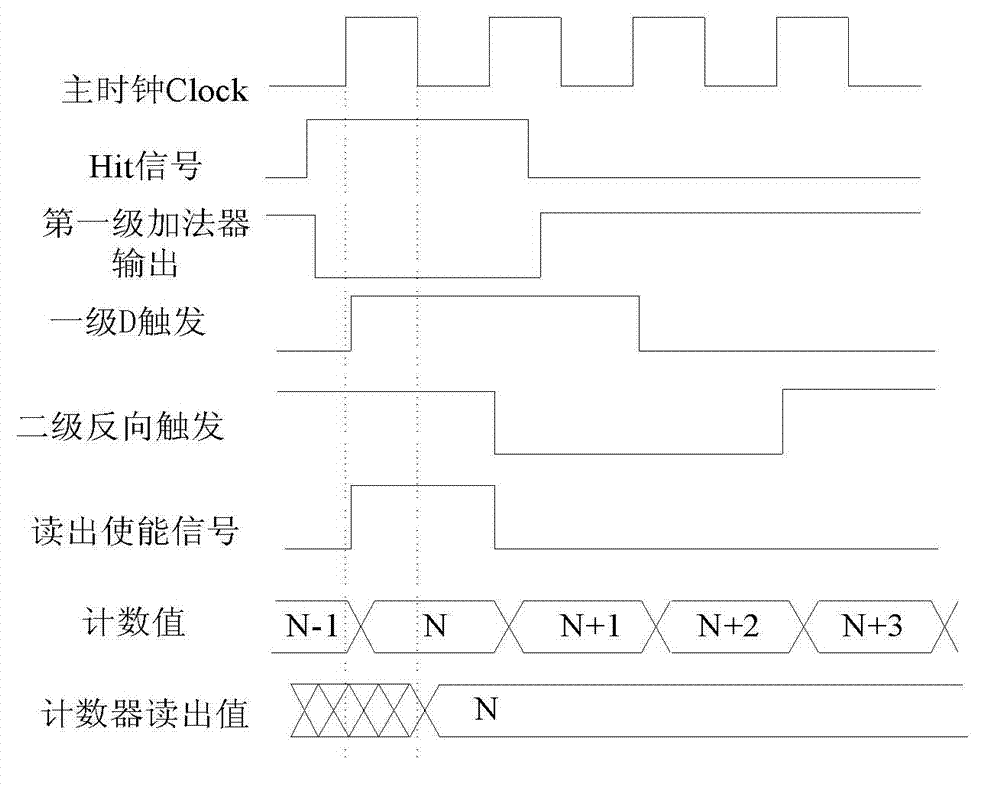

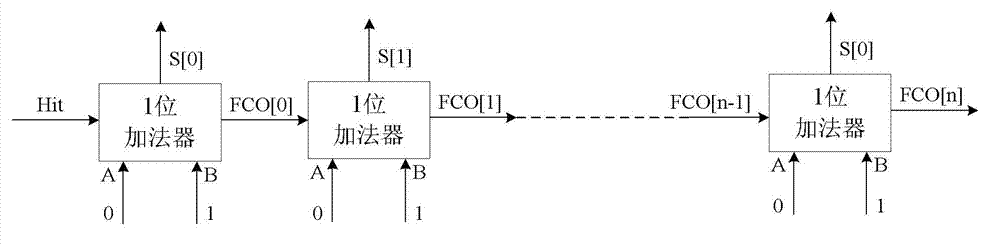

[0020] The present invention realizes the principle structure framework of the measurement of coarse time and fine time in antifuse FPGA as figure 1 As shown, it includes a fine time measurement unit, a decoding unit, a coarse time measurement unit and a data buffer unit, all of which are implemented in an antifuse FPGA. Wherein the fine time measurement unit utilizes the carry cascade delay line in the antifuse FPGA to interpolate the main clock cycle, and the carry cascade delay line is formed by cascading multi-stage delay units, a preferred embodiment of the present invention In the embodiment, a one-bit adder is selected to realize the delay unit, and the fixed time delay of each stage is very small, and the delay of...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More