Mixed compensating type high-stability LDO (low-dropout regulator) chip circuit

A high-stability, hybrid compensation technology, applied in the direction of adjusting electrical variables, control/regulating systems, instruments, etc., can solve the problems of high output impedance, unusable, output voltage oscillation, etc., to achieve the effect of reducing the area and reducing the cost

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

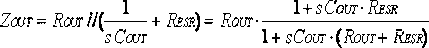

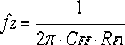

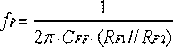

[0014] Please refer to the attached figure 1 As shown, the present invention is a hybrid compensation type high-stability LDO chip circuit, including a differential input amplifier A1, a push-pull buffer amplifier A2, an integrated PMOS device P0, resistors Rc, RF1, RF2, capacitors Cc, CFF, and a chip output capacitor Cout, the equivalent series resistance Resr of Cout, the chip output load Rload.

[0015] The output of A1 is connected to A2, Rc and Cc are connected in series across both ends of A2, the output of A2 is connected to the gate of P0, the drain of P0 is the output terminal Vout, connected to one end of RF1, Cout, and Rload, RF1 and RF2 are connected in series to ground, and CFF is connected to RF1 At both ends, the intersection of RF1 and RF2 is connected to the negative input terminal of A1, Cout and Resr are connected in series to ground, and the other end of Rload is grounded.

[0016] The detailed circuit diagram of the hybrid compensation type high-stability...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More