Crystalline silicon solar cells

A technology of solar cells and crystalline silicon wafers, which is applied in the direction of circuits, electrical components, semiconductor devices, etc., can solve the problems of reducing the utilization efficiency of solar cells, high production costs of solar cells, and increased use of conductive paste, etc., to achieve increased Effects of large surface passivation area, area reduction, and print weight reduction

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

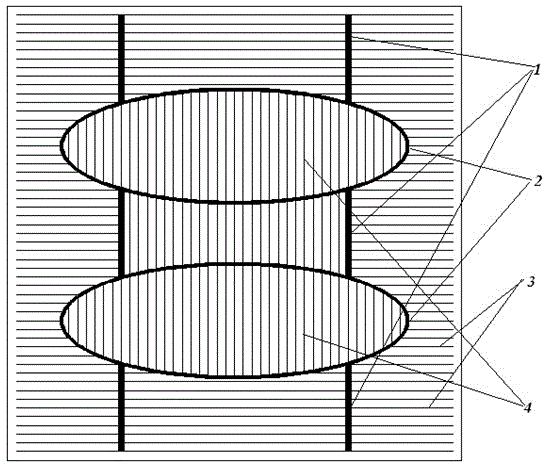

[0031] Select 156 quasi-monocrystalline silicon wafer cells, the front grid line structure includes: first-level main grid 1, second-level main grid 2 and auxiliary grid; among them, there are two first-level main grids 1 parallel to each other, and each first-level main grid 1 is divided into three sections, the second-level main grid 2 connects the segments of the first-level main grid 1 in sequence and forms two ovals, the first-level auxiliary grid 3 is perpendicular to the first-level main grid 1 and connected together and is located on the second-level main grid In addition to the pattern of the grid 2, the second-level sub-gate 4 is parallel to the first-level main grid 1 and is located within the graphics of the second-level main grid 2 and connected to the second-level main grid; the width of the second-level main grid ≤ the first-level main grid width. There are two electrodes on the back, and the shape and structure correspond to the first-level busbar 1 on the fron...

Embodiment 2

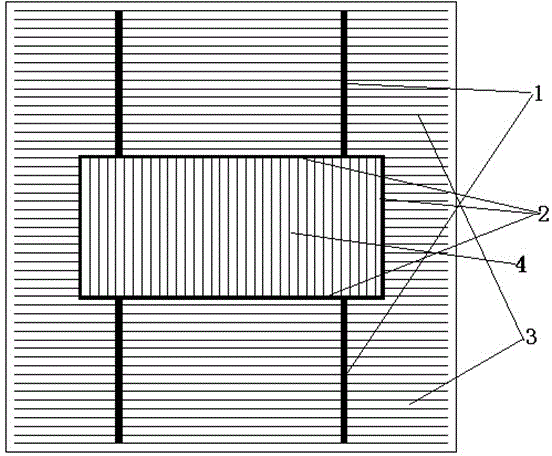

[0033] Select 125 monocrystalline silicon wafer cells, the front grid line structure includes: first-level main grid 1, second-level main grid 2 and auxiliary grid; among them, there are two first-level main grids 1 parallel to each other, and each first-level main grid 1 Divided into two sections, the second-level main grid 2 is square and connects the first-level main grid 1 segmentally, the first-level auxiliary grid 3 is perpendicular to the first-level main grid 1 and connected together, and is located between the graphics of the second-level main grid 2 In addition, the secondary sub-gate 4 is parallel to the primary main gate 1 within the pattern of the secondary main gate 2 and connected to the secondary main gate; the width of the secondary main gate ≤ the width of the primary main gate. There are two electrodes on the back, and the shape and structure correspond to the first-level busbar 1 on the front.

Embodiment 3

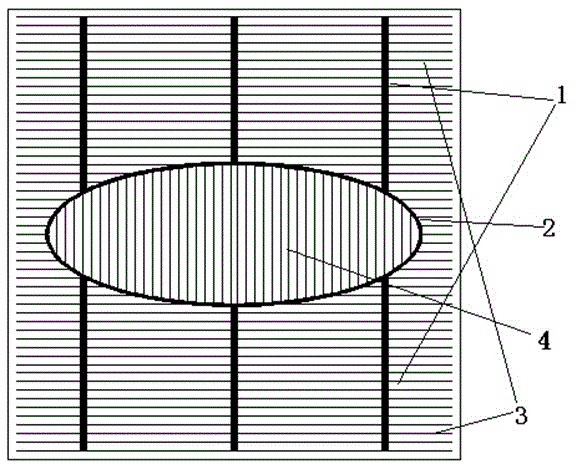

[0035] Select 156 monocrystalline silicon wafer cells, the front grid line structure includes: first-level main grid 1, second-level main grid 2 and auxiliary grid; among them, the first-level main grid 1 consists of two parallel to each other, and each first-level main grid 1 Set in two sections, the secondary main grid 2 is elliptical and connects the first-level main grid 1 in sections, the first-level sub-grid 3 is perpendicular to the first-level main grid 1 and connected together, and is located in the figure of the second-level main grid 2 In addition, the secondary sub-gate 4 is parallel to the primary main gate 1 within the pattern of the secondary main gate 2 and connected to the secondary main gate; the width of the secondary main gate ≤ the width of the primary main gate. There are three electrodes on the back, and the shape and structure correspond to the first-level main grid 1 on the front.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More