Integrated circuit fault detection method based on feature extraction

An integrated circuit and fault detection technology, applied in the field of integrated circuit fault detection based on feature extraction, can solve the problems of noise sensitivity, reduced reliability, reliability and reproducibility, and high requirements for test signals

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

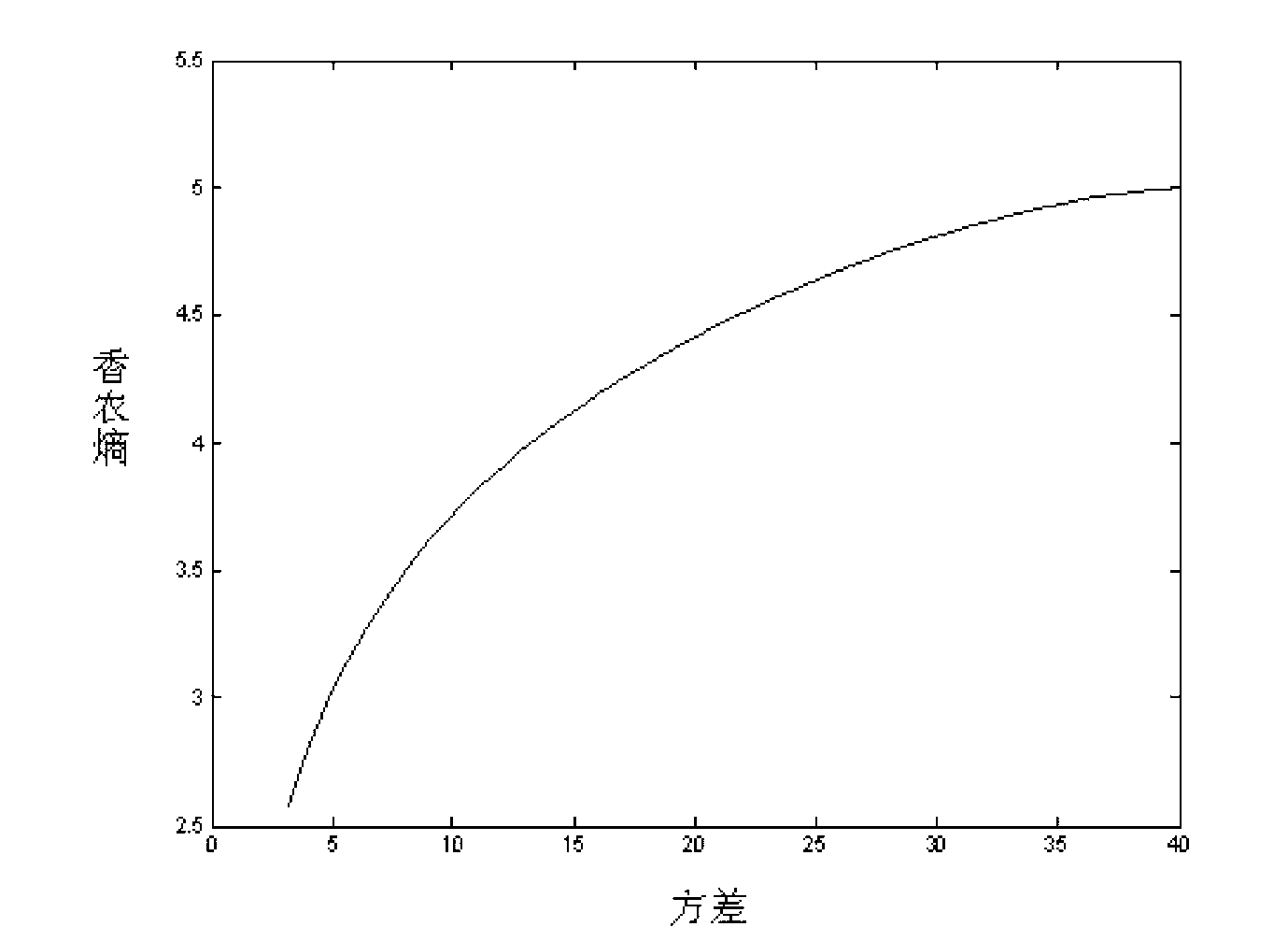

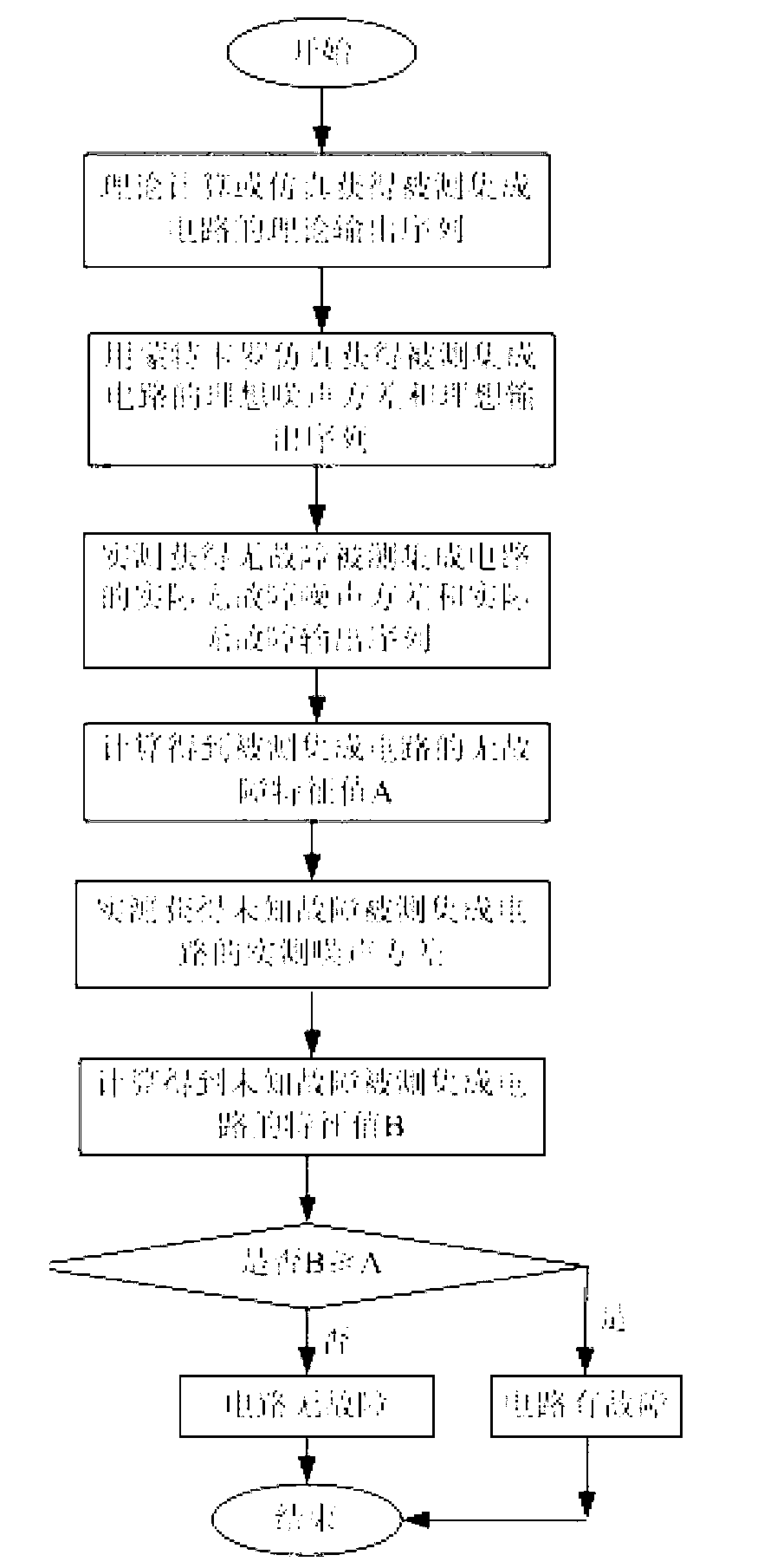

[0077] Such as figure 2 , image 3 shown. The simulation test carried out on the leapfrog filter circuit is realized on a personal computer with a 3GHz processor and a 1-GB random access device, and all software codes are programmed and realized under the Matlab environment. The nominal parameters of all resistors are 10KΩ, and the capacitance C 1 and C 4 The nominal parameter of C 1 =C 4 =0.01μF, capacitance C 2 and C 3 The nominal parameter of C 2 =C 3 =0.02μF. The leapfrog filter of the circuit under test is a low-pass filter, which is based on the MI-TEL semiconductor complementary metal oxide semiconductor technology (CMOS) process. The signal source is a 1kHz sine wave, the sampling rate is 200kHz, and 2048 points are sampled (the length of all the sequences below is 2048 points, that is, L=S×Q=2048). The specific implementation steps are as follows:

[0078] (1) Set the parameters of each component of the tested integrated circuit as nominal parameters, sim...

Embodiment 2

[0109] Such as figure 2 , Figure 4 shown. The same places as in Embodiment 1 will not be described again, the difference is that: the state variable filter in the international standard circuit is selected to verify the method of the present invention. The nominal parameters of each component of the state variable filter are: R 2 =3KΩ,R 1 =R 3 =R 4 =R 5 =R 6 =R 7 =10KΩ, C 1 =C 2 =0.02μF. The output measurement node is at the bandpass output port, ie Figure 4 Node "4" in . The sampling frequency is 25kHz. The simulation results are in Table 2.

[0110] The meanings of each column in Table 2 are the same as those in Table 1. The method of the invention is effective for both parametric faults and catastrophic faults. It can be seen from Table 2 that, using the method of the present invention, a one-to-one correspondence relationship is established between faults and fault characteristic values (Shannon entropy). For example, the Shannon entropy of the noise ...

Embodiment 3

[0114] Such as figure 2 , Figure 5 , Figure 6 shown. The same places as in Embodiment 1 will not be described again, the difference is that this embodiment is completed by actual measurement on the actually manufactured circuit board, so step (9) is completed by actual measurement. Figure 6 is according to Figure 5 The Tow-Thomas filter circuit actually made. Figure 5 The nominal parameters of the components in are: R 1 =R 2 =R 3 =R 4 =16KΩ, R 5 =R 6 =10KΩ, C 1 =C 2 =1nF. Figure 5 The operational amplifier in is a TL084 device produced by TI Company of the United States, which has been installed in Figure 6 middle. The input excitation of the Tow-Thomas filter circuit under test is a 1 volt, 10-kHz sinusoidal signal, and the output of the Tow-Thomas filter circuit under test is collected by a TDS2012 oscilloscope from Tektronix Instruments, Inc. of the United States. The sampling rate of this oscilloscope is It is 1GS / s, and the sampling bandwidth is 100...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More