Wafer level semiconductor encapsulation structure with stacking chips and manufacturing method thereof

A manufacturing method and semiconductor technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, semiconductor/solid-state device components, etc., can solve the problems of high cost of through-hole forming process, increase of product horizontal size and packaging structure, etc., to reduce product Dimensional and structural stress, the effect of saving packaging costs

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0014] In order to make the above objects, features and advantages of the present invention more comprehensible, preferred embodiments of the present invention are exemplified below and described in detail in conjunction with the accompanying drawings. Furthermore, the directional terms mentioned in the present invention, such as "up", "down", "front", "back", "left", "right", "inside", "outside", "side", etc., It is only for orientation with reference to the attached drawings. Therefore, the directional terms used are used to illustrate and understand the present invention, but not to limit the present invention.

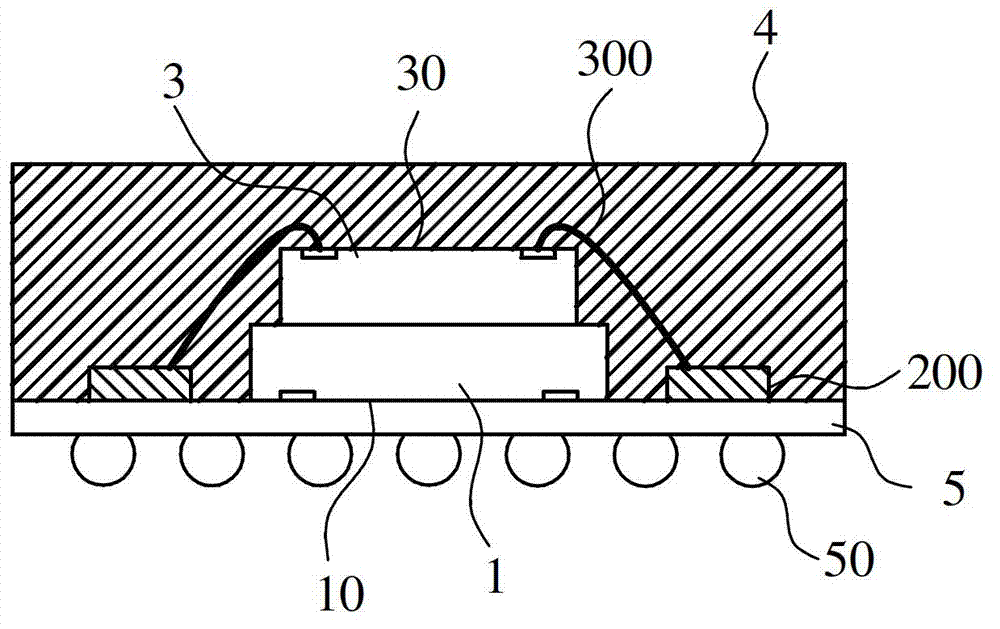

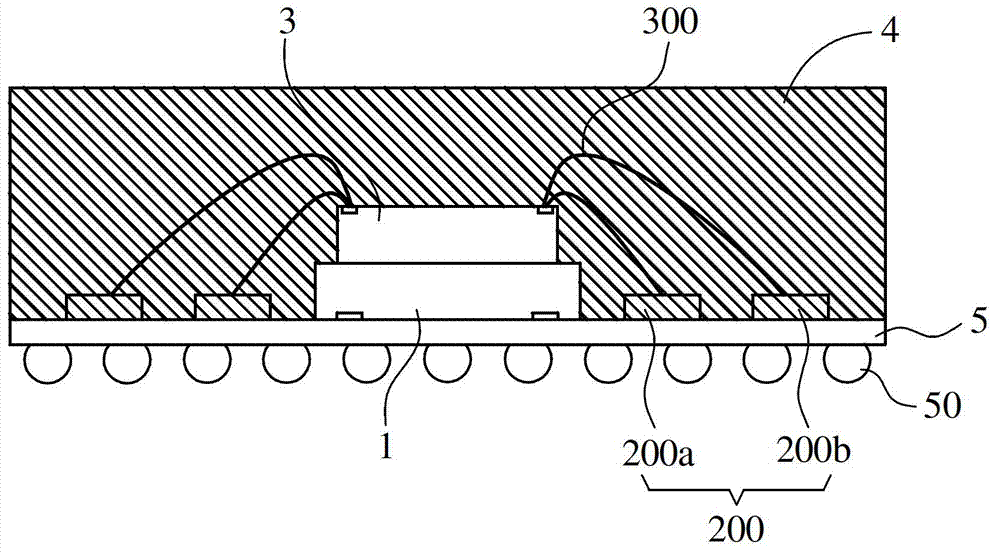

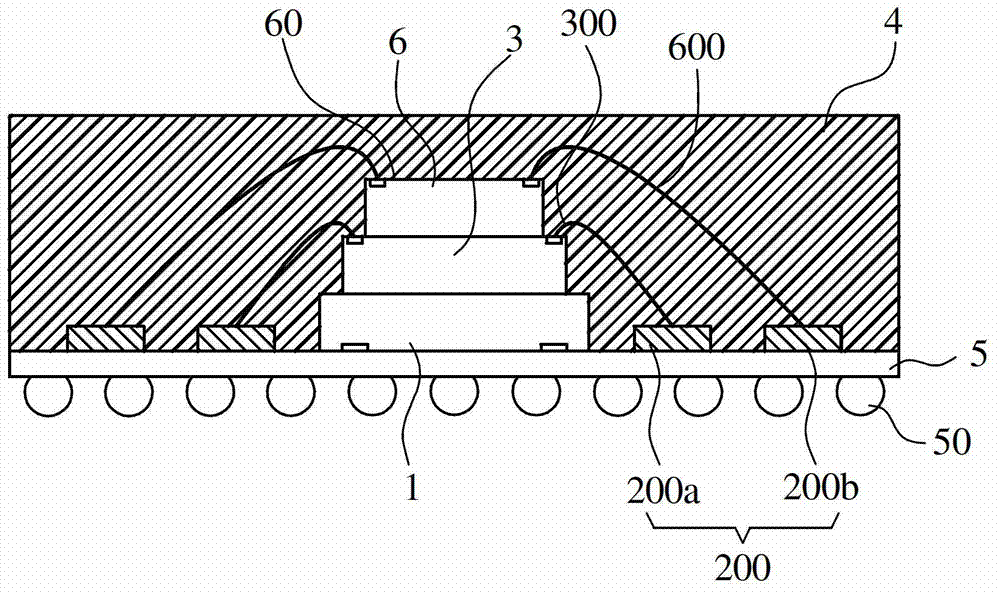

[0015] Please refer to figure 1 as shown, figure 1 It is a schematic structural view of a wafer-level semiconductor package structure with stacked chips according to an embodiment of the present invention. figure 1 The disclosed wafer-level semiconductor packaging structure with stacked chips mainly includes a first chip 1 , a plurality of lead frame terminals 2...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More