Layout Layer Design Method of Semiconductor Chip and Mask Plate

A design method and semiconductor technology, which is applied in semiconductor/solid-state device manufacturing, photolithographic process of patterned surface, and original parts used in photomechanical processing, etc., which can solve the problems of low optical accuracy, short cycle time, and low computational efficiency, etc. problem, to achieve the effect of improving calculation efficiency, reducing graphics area, and improving accuracy

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

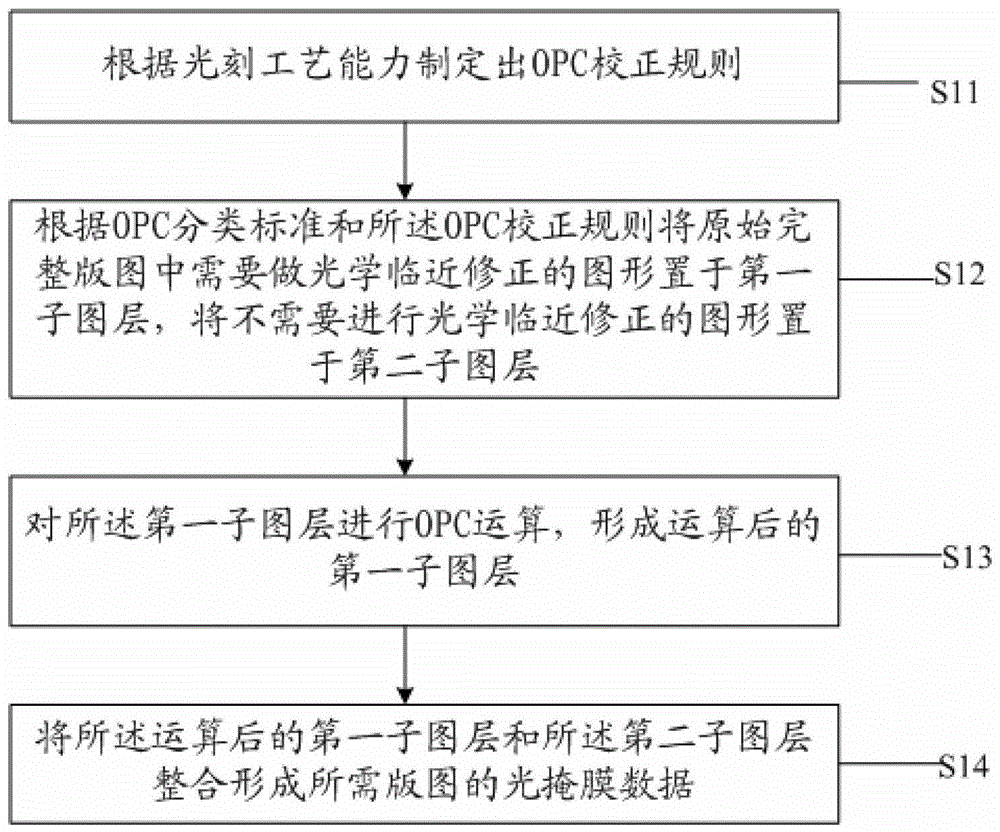

[0019] The layout layer design method of the semiconductor chip and its mask plate proposed by the present invention will be further described in detail below in conjunction with the accompanying drawings and specific embodiments. Advantages and features of the present invention will be apparent from the following description and claims. It should be noted that all the drawings are in a very simplified form and use imprecise scales, and are only used to facilitate and clearly assist the purpose of illustrating the embodiments of the present invention.

[0020] The core idea of the present invention is that the semiconductor chip layout layer design method provided by the present invention only needs to perform optical proximity correction on the first sub-layer, and does not perform any processing on the second sub-layer. The actual calculation amount, The calculation graphic area is greatly reduced, the calculation efficiency is greatly improved, the work efficiency of the ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More