Inter-processor communication method and system on chip

A system-level chip and communication method technology, which is applied in the communication method between processors and the SOC field, can solve problems such as not easy to expand, and achieve the effects of improving mailbox resource utilization, improving use flexibility, and saving implementation costs

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

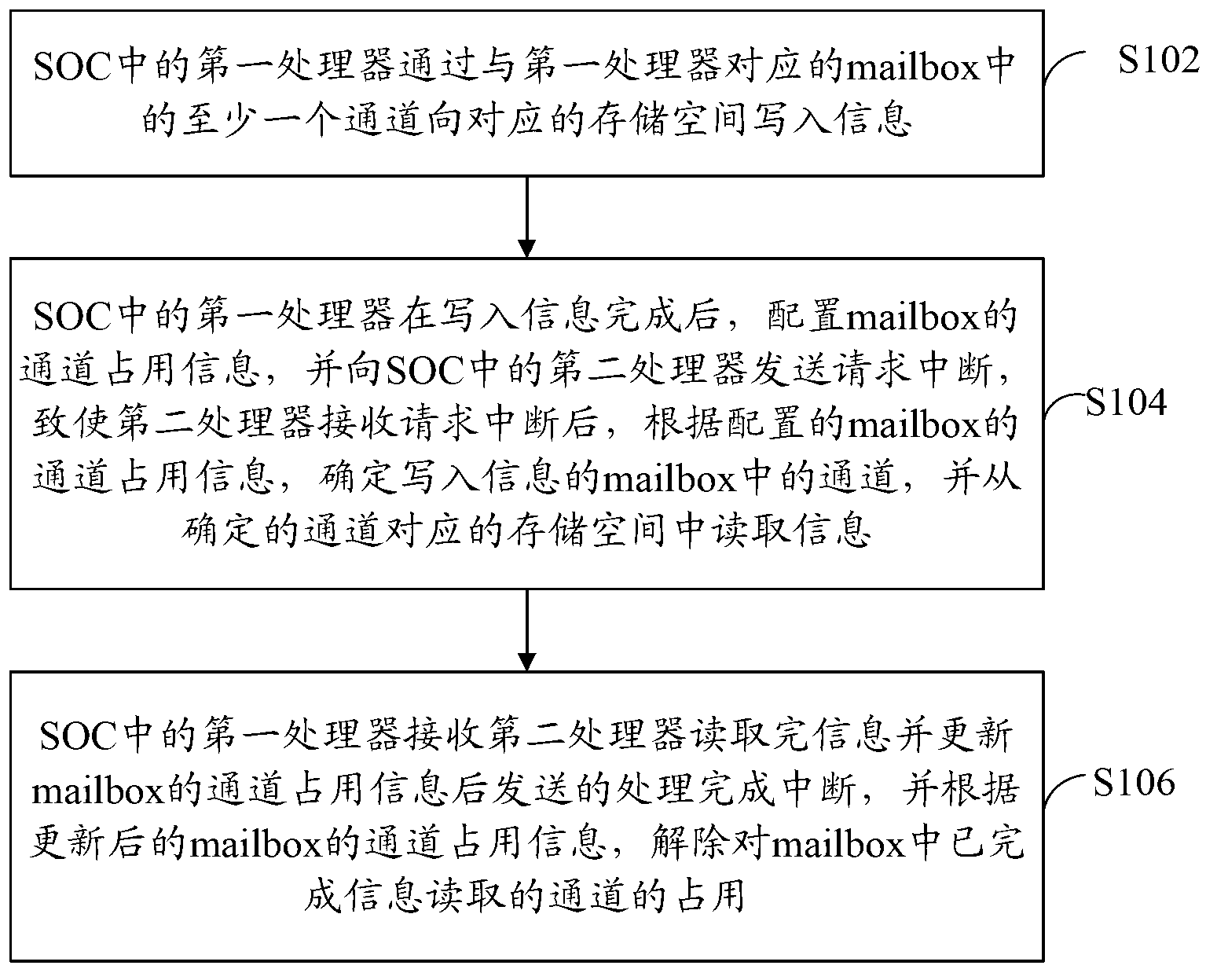

[0029] refer to figure 1 , shows a flow chart of steps of an inter-processor communication method according to Embodiment 1 of the present invention.

[0030] The inter-processor communication method in this embodiment includes the following steps:

[0031] Step S102: the first processor in the SOC writes information to the corresponding storage space through at least one channel in the mailbox corresponding to the first processor.

[0032] Wherein, the mailbox is allocated by the SOC for the communication between the first processor and the second processor in the SOC, and each mailbox includes multiple channels.

[0033] In this embodiment, the SOC includes multiple processors, and the multiple processors include a first processor and a second processor. In a specific application, the number of processors is determined by system requirements, and at least two processors are included in an SOC using a mailbox. In the present invention, the specific number of processors inc...

Embodiment 2

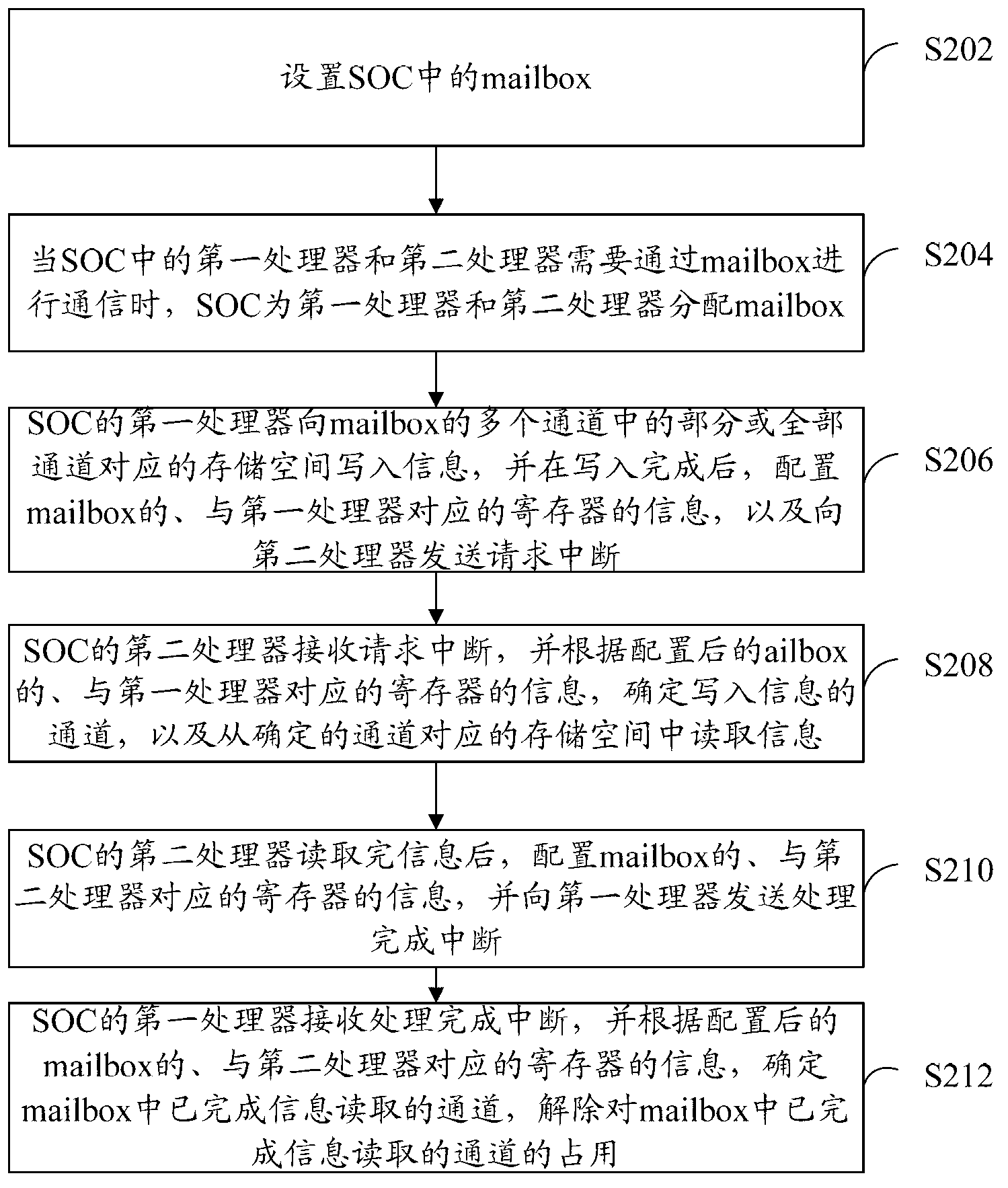

[0045] refer to figure 2 , shows a flow chart of steps of a method for inter-processor communication according to Embodiment 2 of the present invention.

[0046] The inter-processor communication method in this embodiment includes the following steps:

[0047] Step S202: setting a mailbox in the SOC.

[0048] In this embodiment, the setting mailbox includes multiple channels, a status register indicating the status of the multiple channels, an initiation request register for applying for the multiple channels, and a processing completion register indicating the completion of reading information of the multiple channels. Wherein, the register corresponding to the processor (the first processor in this embodiment) that writes data includes an initiation request register and a status register; and the processor that reads data (the second processor in this embodiment) Corresponding registers include a processing completion register and a status register. That is, the status r...

Embodiment 3

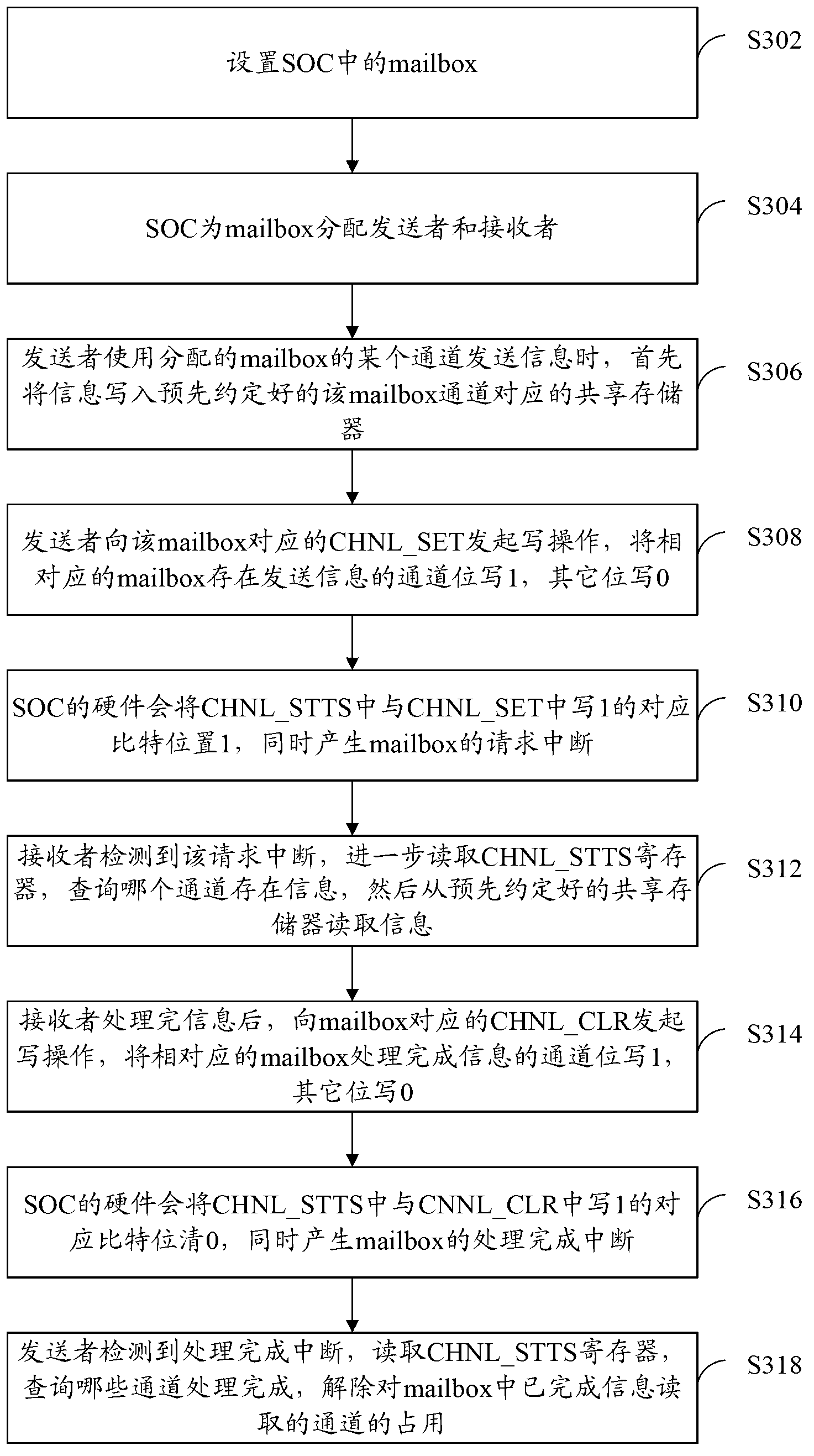

[0065] refer to image 3 , shows a flow chart of steps of an inter-processor communication method according to Embodiment 3 of the present invention.

[0066] The inter-processor communication method in this embodiment includes the following steps:

[0067] Step S302: setting a mailbox in the SOC.

[0068] In this embodiment, each mailbox resource in the SOC is set to include a 32-bit status register (CHNL_STTS), a 1-bit request interrupt (REQ_INT) and a 1-bit processing completion interrupt (ACK_INT); in addition, in order to facilitate multiple processors to complete the For mailbox request and processing completion control, two additional 32-bit interface registers need to be implemented, one is the initiation request register (CHNL_SET), and the other is the processing completion register (CHNL_CLR). The structure of the above-mentioned mailbox is as follows Figure 4 shown. Among them, CHNL_STTS indicates the status of the 32 channels corresponding to the mailbox. Set ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More