Method and structure for three-dimensional packaging based on TSV

A three-dimensional packaging and packaging structure technology, which is applied in the manufacturing of electrical components, electrical solid-state devices, semiconductor/solid-state devices, etc. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

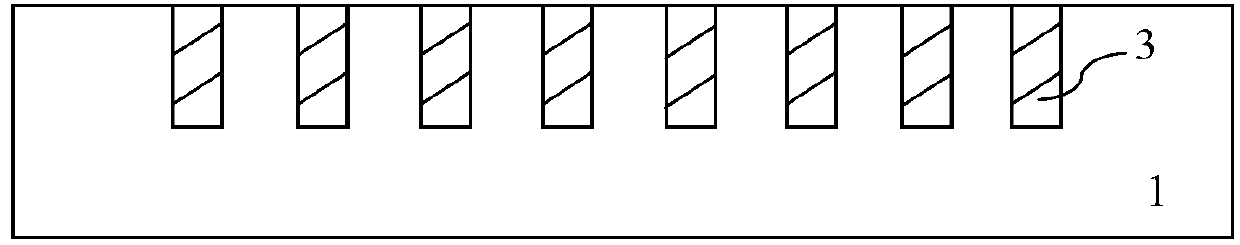

Image

Examples

Embodiment Construction

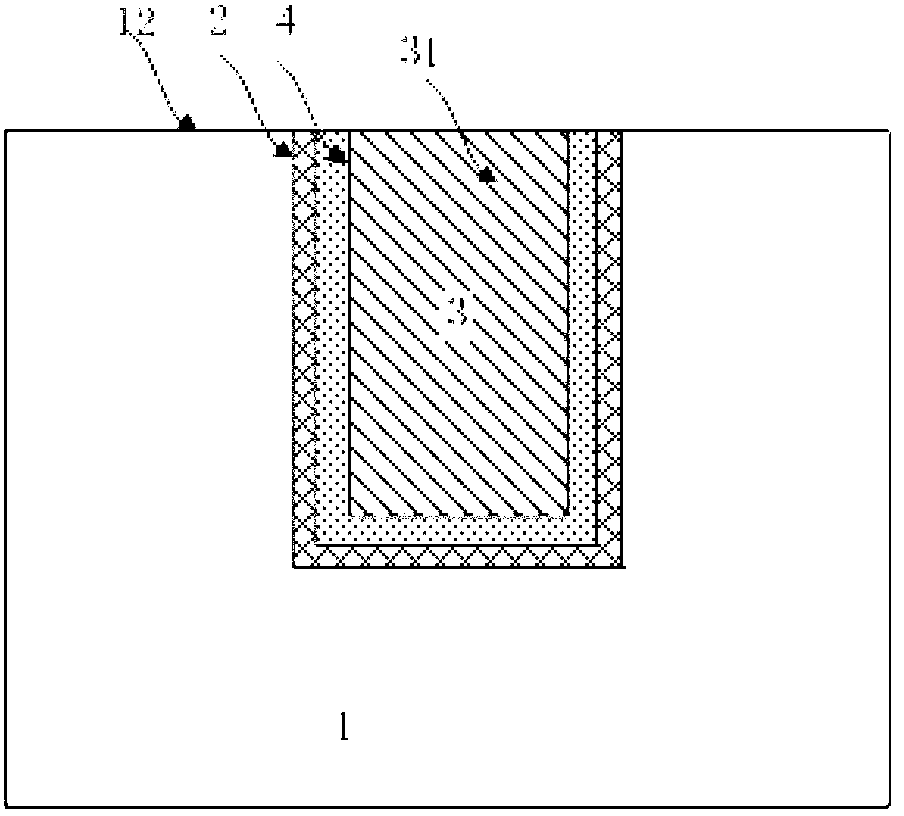

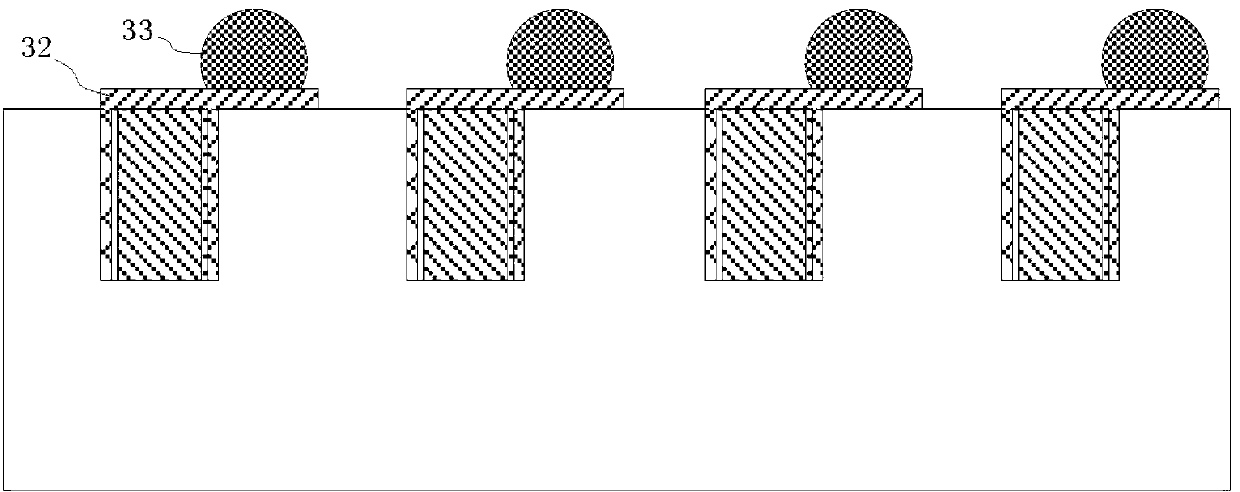

[0027] As mentioned in the background technology, for the existing wafers based on TSV packaging technology, during the packaging process, due to the difference in thermal expansion coefficient between the plastic packaging material and the wafer itself, it is easy to cause excessive stress on the wafer during the packaging process resulting in wafer warpage. Facing this problem, some existing technical solutions need to inject some dopants into the wafer to change the warping characteristics of the wafer. However, these technical solutions are not only complicated in process and high in cost, but also easily bring some additional quality problems to the wafer after modification.

[0028] Therefore, aiming at the defects in the prior art, the present invention proposes a new low-stress three-dimensional packaging structure and method based on TSV technology. The TSV packaging structure is provided with at least two layers of different plastic encapsulants on the wafer and the ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More