Trench VDMOS device and manufacturing method thereof

A trench type and device technology, which is applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve the problems of multiple layers of photolithography and low device cell density, so as to increase cell density and reduce manufacturing costs , the effect of reducing the number of photolithography layers

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

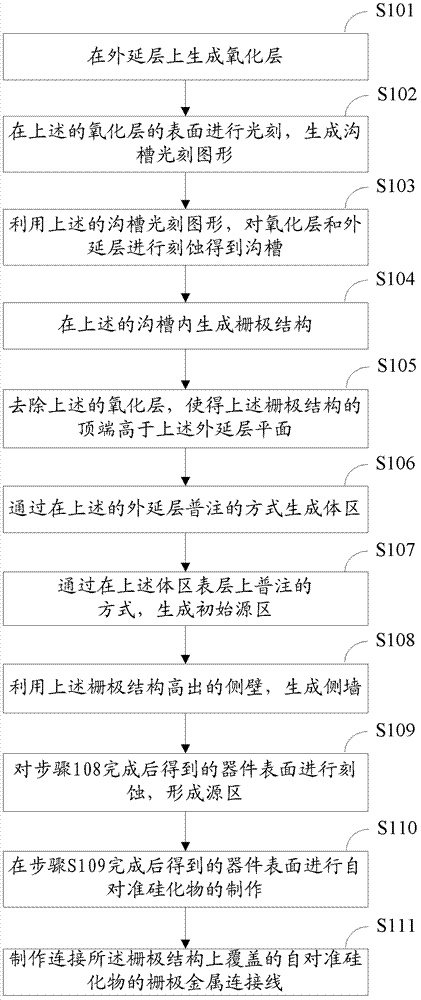

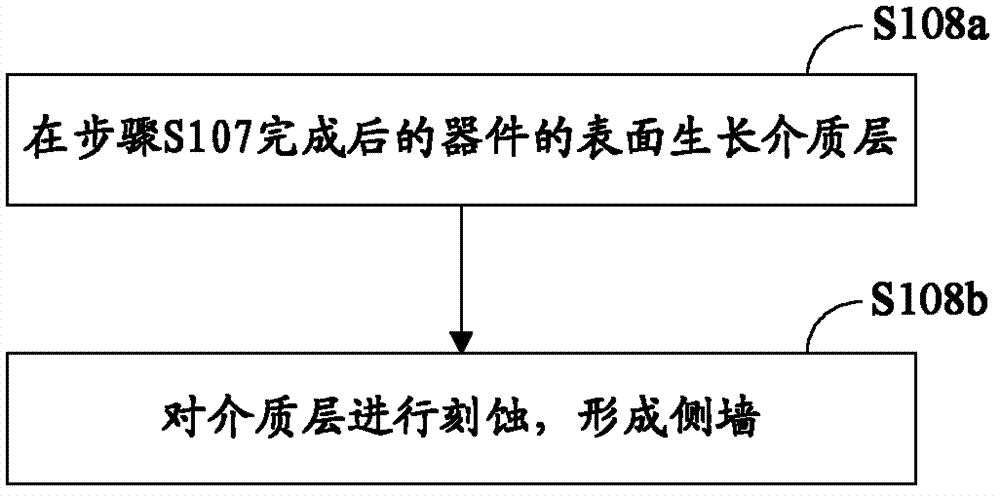

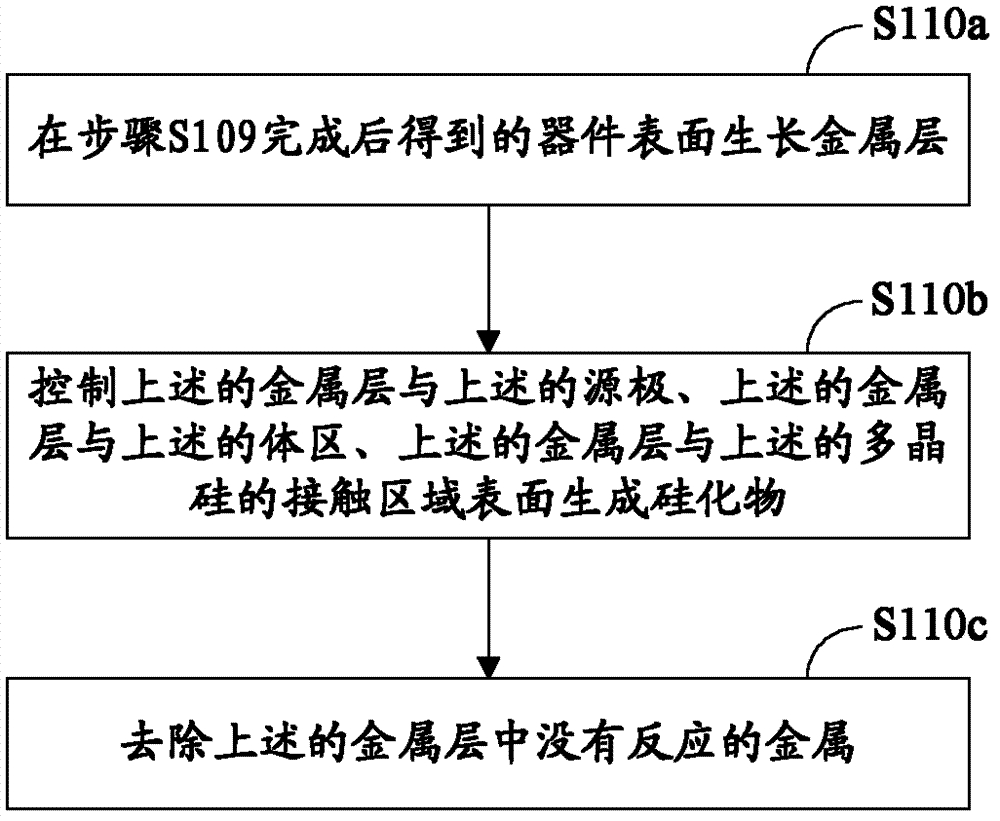

[0044] An embodiment of the present invention provides a method for manufacturing a trench-type VDMOS device, and its preferred implementation is as follows figure 1 , mainly including the following operations:

[0045] S101, forming an oxide layer 10 on the epitaxial layer.

[0046] Wherein, the above-mentioned epitaxial layer (such as N-type epitaxial layer) is made on the substrate (such as N-type substrate), and the purpose of forming the oxide layer 10 on the epitaxial layer is to make the polysilicon top of the gate structure grown in subsequent steps Higher than the plane of the epitaxial layer, the thickness of the oxide layer 10 should meet the requirement for the height of the polysilicon top of the gate structure to be higher than the plane of the epitaxial layer during subsequent processing.

[0047] S102 , performing photolithography on the surface of the above-mentioned oxide layer 10 to generate a trench photolithography pattern.

[0048] S103. Etching the oxi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More