Forming method of semiconductor structure and forming method of transistor

A semiconductor and crystal orientation technology, applied in the formation of semiconductor structures and the formation of transistors, can solve the problems of complex process and high production cost, and achieve the effects of simple process, easy operation and low production cost

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

[0055] Please refer to Image 6 , is a schematic flowchart of a method for forming a semiconductor structure according to the first embodiment of the present invention, including steps:

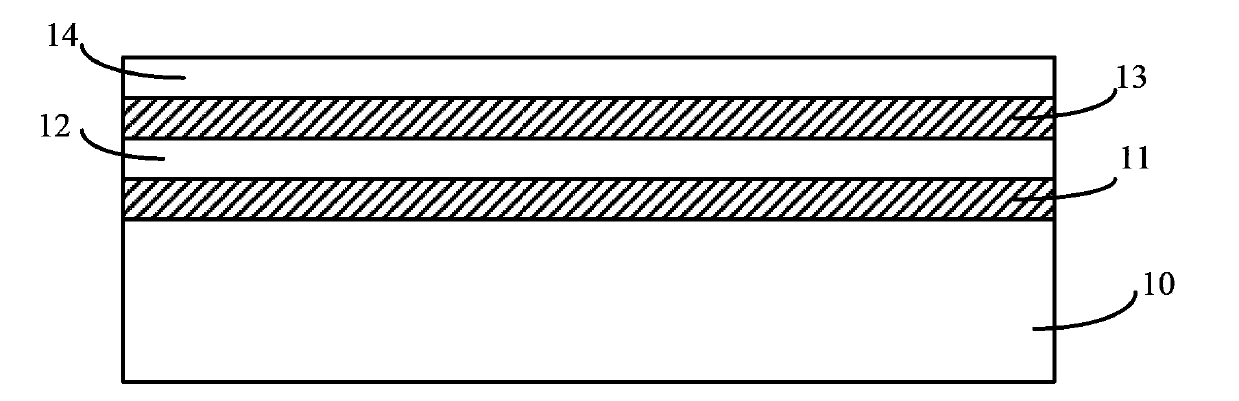

[0056] Step S101, providing a semiconductor substrate, and the semiconductor substrate is a semiconductor-on-insulator, and the semiconductor-on-insulator includes: a substrate, an insulating layer on the surface of the substrate, and a semiconductor layer on the surface of the insulating layer;

[0057] Step S102, forming a hard mask layer on the surface of the semiconductor substrate;

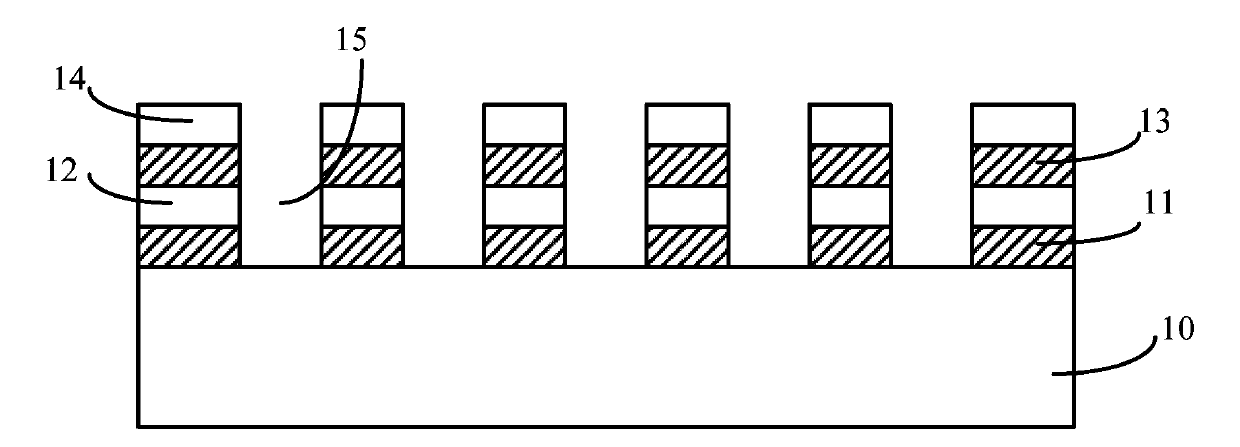

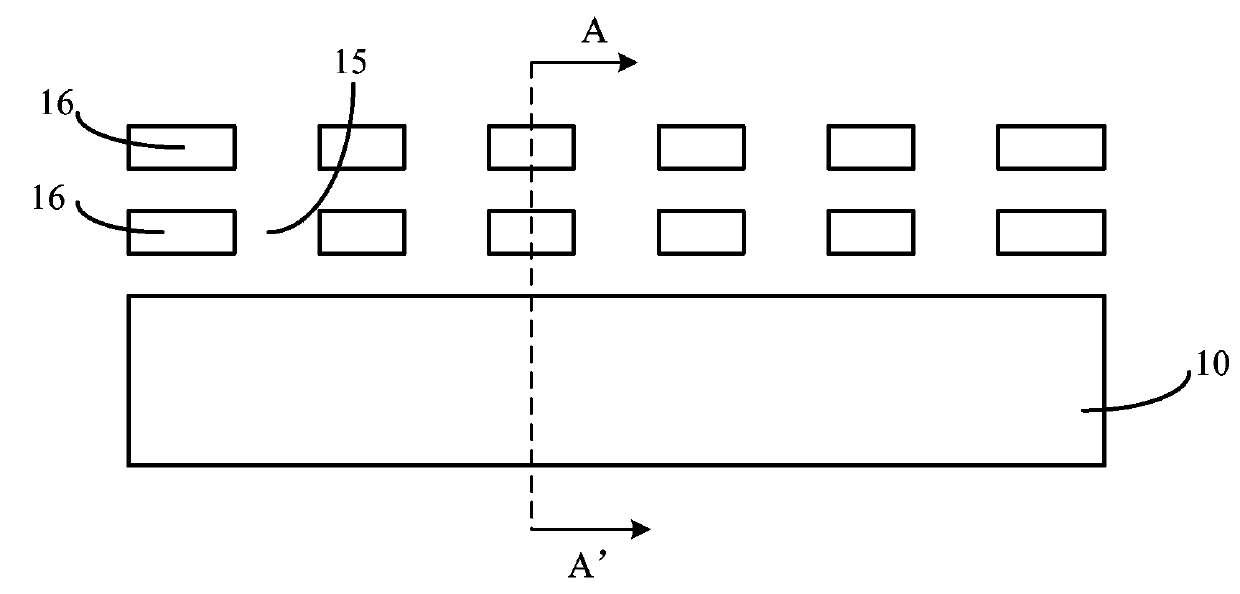

[0058] Step S103, removing part of the hard mask layer, and using the remaining hard mask layer as a mask to form a number of openings in the semiconductor layer to expose the surface of the insulating layer;

[0059] Step S104, using an anisotropic wet etching method to form the sidewall of the opening to form double-layer discrete nanowires;

[0060] Step S105, after the crystal direction anisotropic wet...

no. 2 example

[0087] The present invention also provides a method for forming a transistor, and the method for forming a transistor in this embodiment will be described below with reference to the accompanying drawings.

[0088] First, double-layer discrete nanowires suspended above the substrate are formed, and the cross-section of the nanowires is circular. Both ends of the nanowires are connected to the remaining semiconductor layer and supported by the remaining insulating layer.

[0089] For the formation method of the double-layer nanowire, please refer to Figure 7 to Figure 12 The method for forming the semiconductor structure of the first embodiment will not be repeated here.

[0090] In the first embodiment Figure 12 Based on that, please continue to refer to Figure 13 with Figure 14 , Figure 14 for Figure 13 A schematic cross-sectional structure view in the CC' direction, after thermal annealing, a gate dielectric layer 107 is formed on the surface of the nanowire 106a;...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More