Multichannel RAM (random-access memory) reading/writing circuit and method

A multi-channel, circuit technology, applied in the field of multi-channel read/write RAM circuits, can solve the problems of bus arbitration, complex decoding mechanism, and increased system design complexity, and achieve increased average power consumption, improved access bandwidth, and easy access. effect achieved

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0031] In order to make the technical solutions and advantages of the present invention clearer, the present invention will be further described in detail below through specific embodiments in conjunction with the accompanying drawings.

[0032] In this application, the general idea of the invention is: in order to improve RAM access bandwidth, multiple RAMs are provided in the circuit, and multiple RAMs can simultaneously accept read / write operations from multiple Masters on the bus. The specific implementation method is as follows:

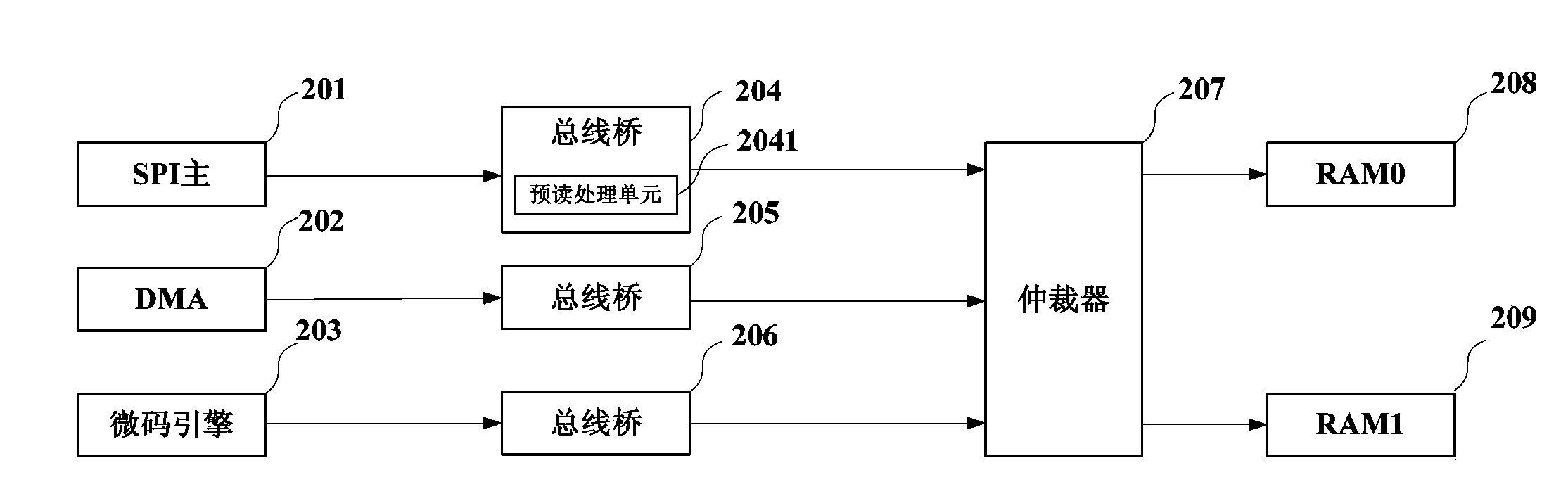

[0033] The present invention provides a multi-channel read / write RAM circuit, which includes at least two master devices, at least two bus bridges, arbitrators and at least two RAMs; wherein, each master device is connected to the arbitrator through a bus bridge , at least two RAMs are connected to the arbiter.

[0034] Master is used to issue the system bus signal for reading / writing RAM, and pass it to the bus bridge for conversion.

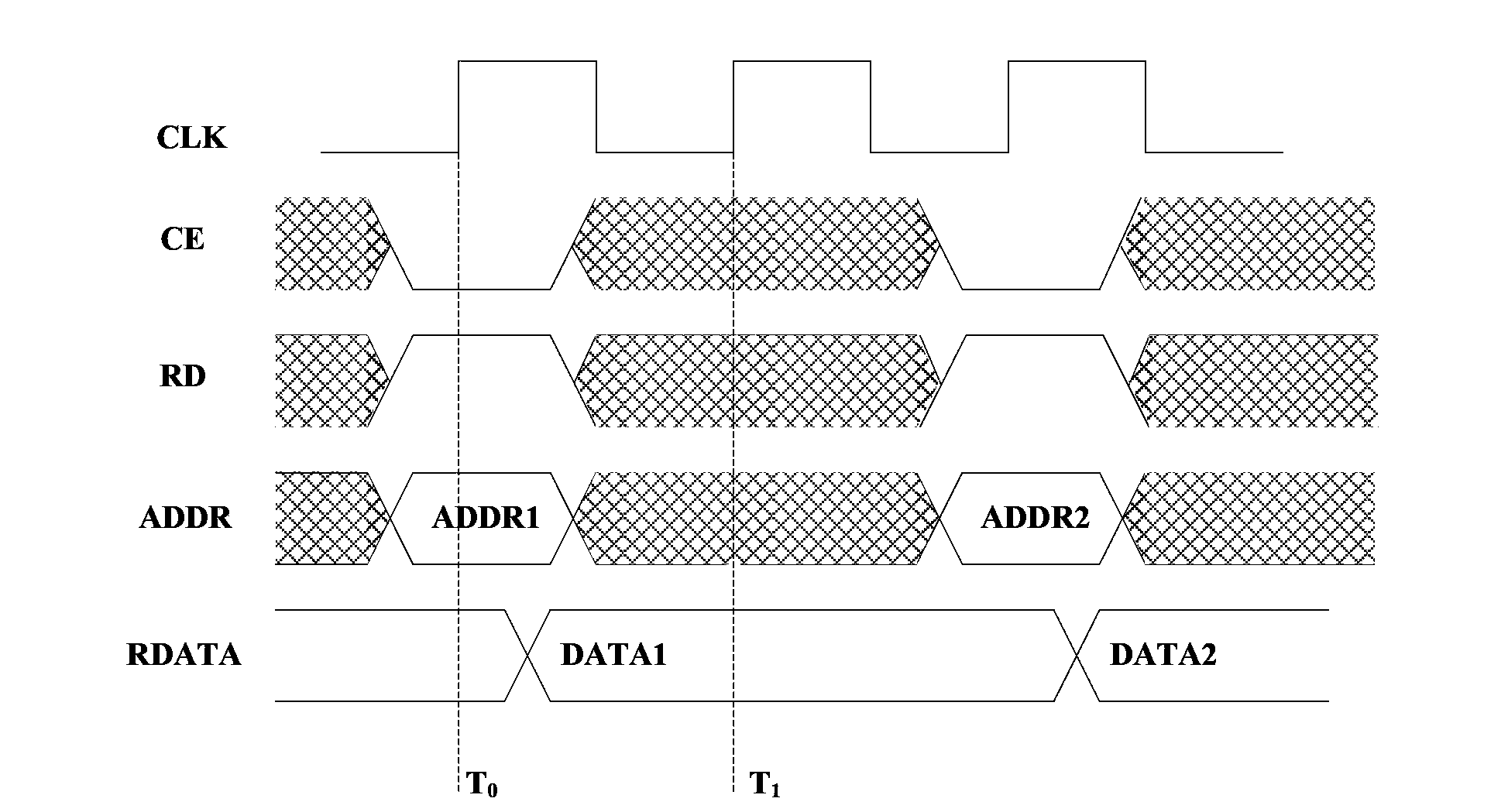

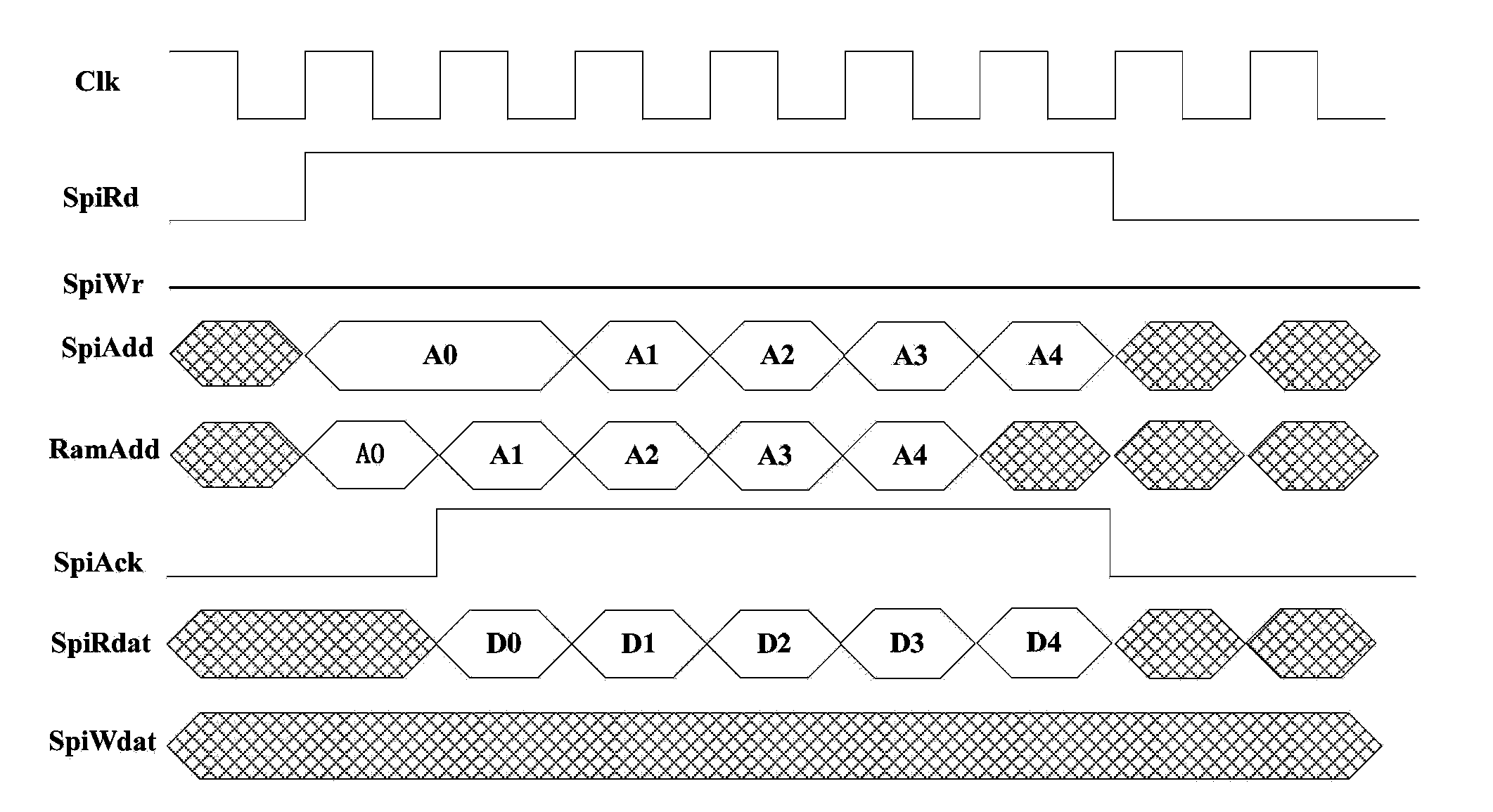

[003...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More