Sigma-delta PLL frequency measuring circuit and method

A frequency measurement and circuit technology, applied in the fields of electronics and time-frequency measurement, can solve the problems of limiting frequency measurement accuracy, difficulty in implementation, quantization error, etc., and achieves improved frequency measurement resolution, improved resolution performance, and low device requirements. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0021] The present invention will be described in further detail below in conjunction with the accompanying drawings and specific embodiments.

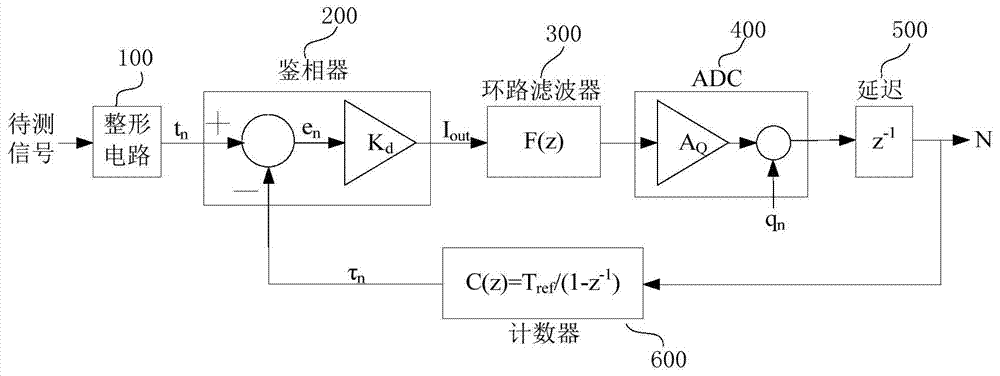

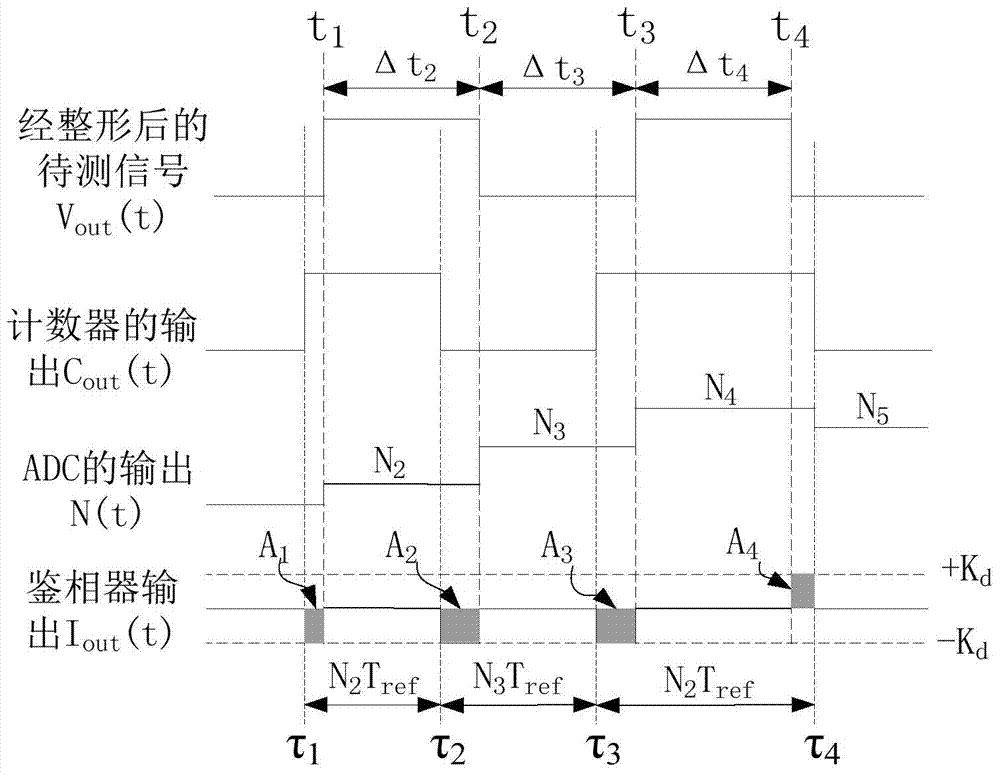

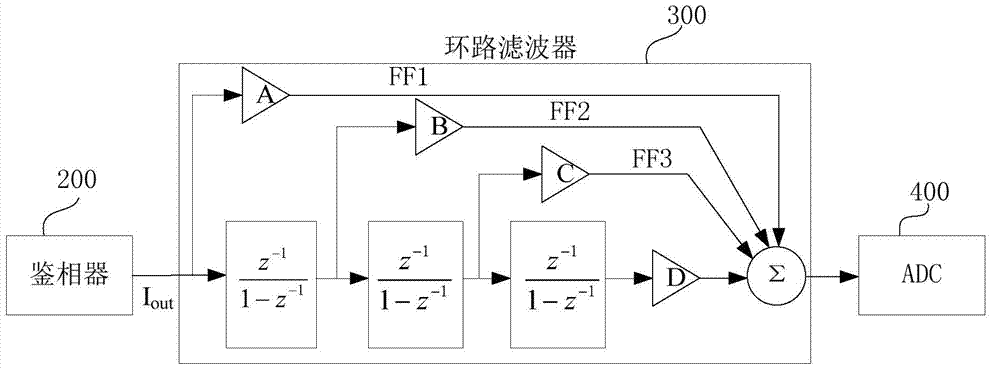

[0022] combine figure 1 , the sigma-delta PLL frequency measurement circuit of the present invention is a closed-loop negative feedback system as a whole, including a shaping circuit 100, a phase detector 200, a loop filter 300, an ADC400 and a delay link 500 arranged sequentially from the input end, And the output terminal of the delay link 500 is fed back to the phase detector 200 through the counter 600, wherein: the shaping circuit 100, after filtering and amplifying the signal to be tested, converts it into a square wave signal V of the same frequency out ; Phase detector 200, measuring the signal V to be tested after shaping out with the counter output signal C out The zero-crossing time difference, and the output area and time difference e n proportional to the pulse current signal I out ; Loop filter 300, to the output cur...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More