Semiconductor device manufacturing method

A device manufacturing method and semiconductor technology, which are applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve problems such as large silicon loss value and substrate damage, and achieve improved driving current, improved gate control capability, and reduced Effects of EoT

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0029] The features and technical effects of the technical solution of the present invention will be described in detail below with reference to the accompanying drawings and in combination with exemplary embodiments. It should be pointed out that similar reference numerals represent similar structures, and the terms "first", "second", "upper", "lower", "thick", "thin" and the like used in this application can be used for Modify various device structures. These modifications do not imply a spatial, sequential or hierarchical relationship of the modified device structures unless specifically stated.

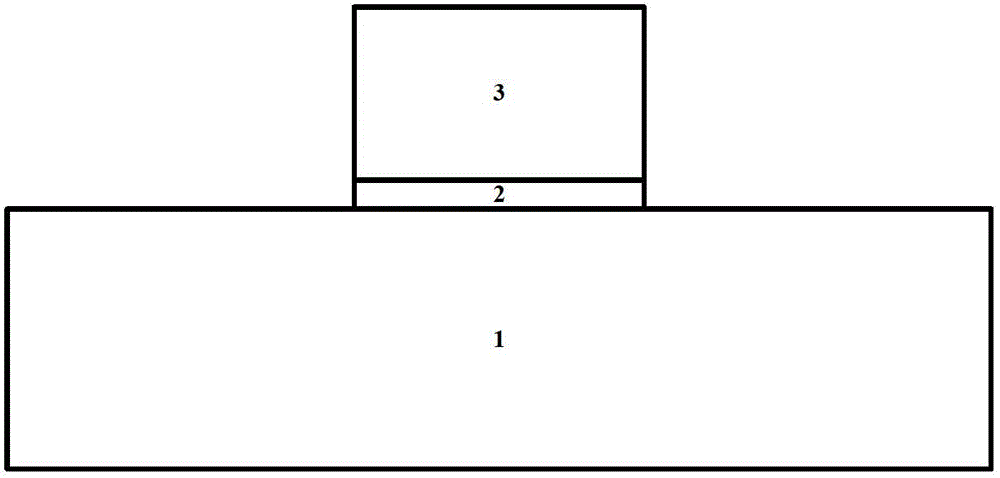

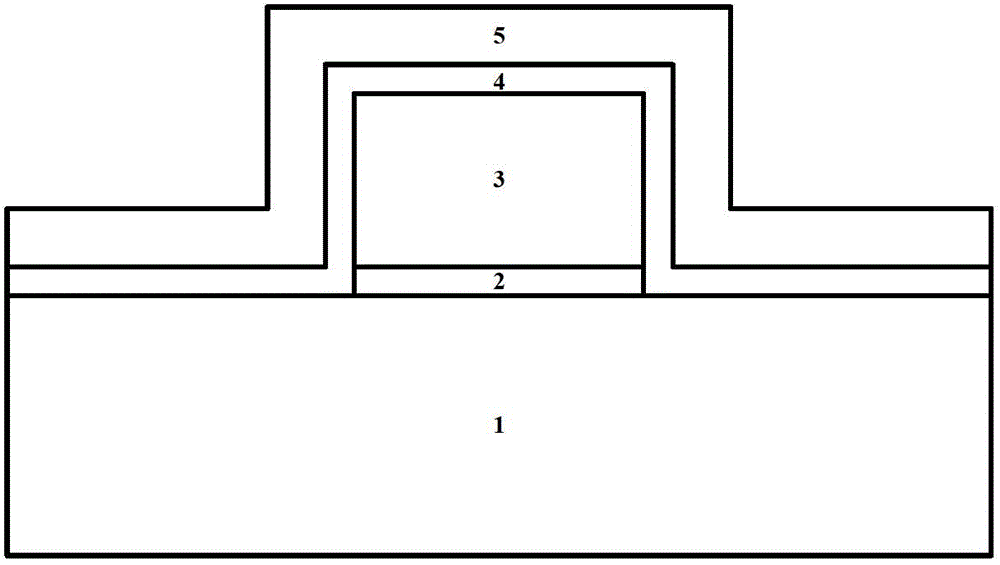

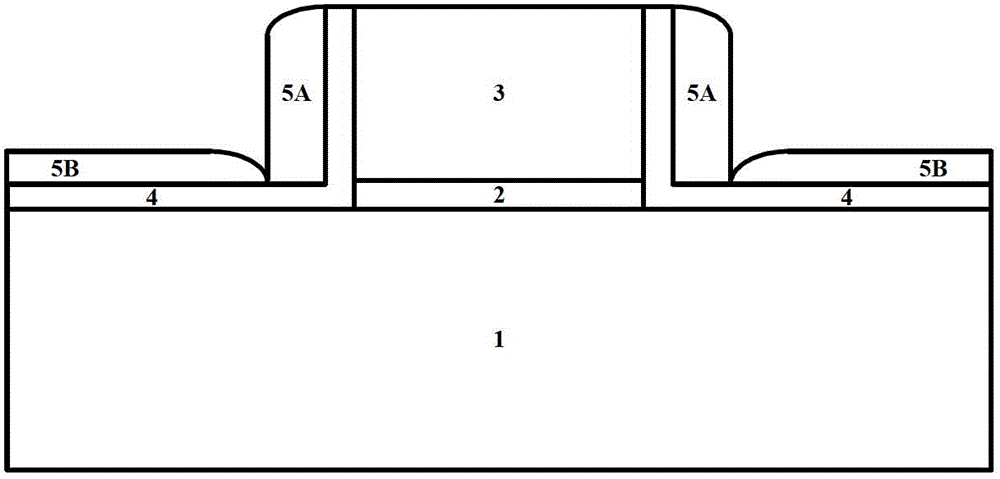

[0030] refer to Figure 6 as well as figure 1 , forming a gate stack structure on the substrate, which may be a gate stack of a gate-first process, or a dummy gate stack of a gate-last process. A substrate 1 is provided, which may be bulk Si, SOI, bulk Ge, GeOI, SiGe, GeSb, or a III-V or II-VI compound semiconductor substrate, such as GaAs, GaN, InP, InSb, etc. In order to be...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More