Low-temperature polycrystalline silicon thin film transistor array substrate, manufacturing method thereof and display device

A technology of thin-film transistors and low-temperature polysilicon, applied in the direction of transistors, semiconductor/solid-state device manufacturing, semiconductor devices, etc., can solve the problems of affecting the display device display, the on-state current affecting TFT characteristics, and the uneven deposition of thin films and etching processes. Achieve the effect of ensuring display quality, improving process stability and reliability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

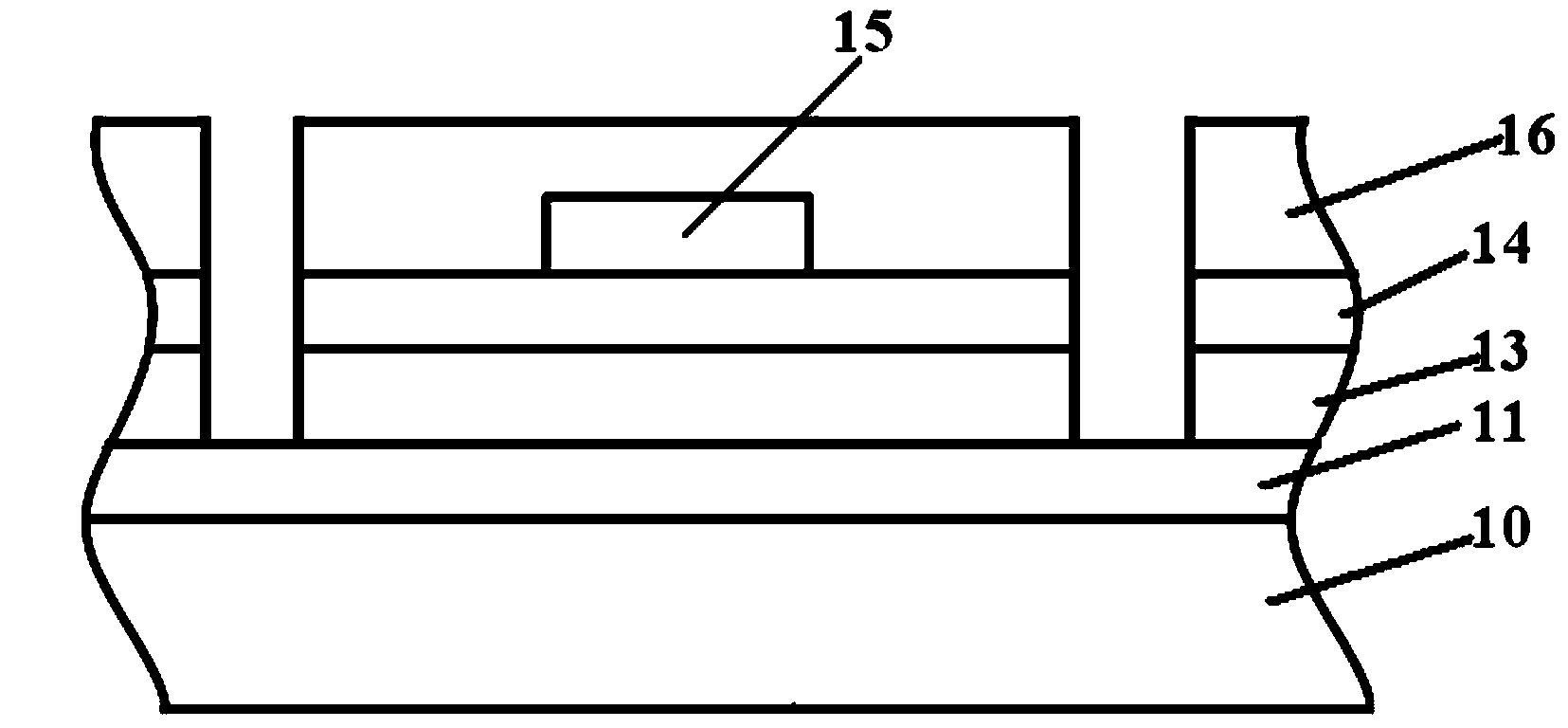

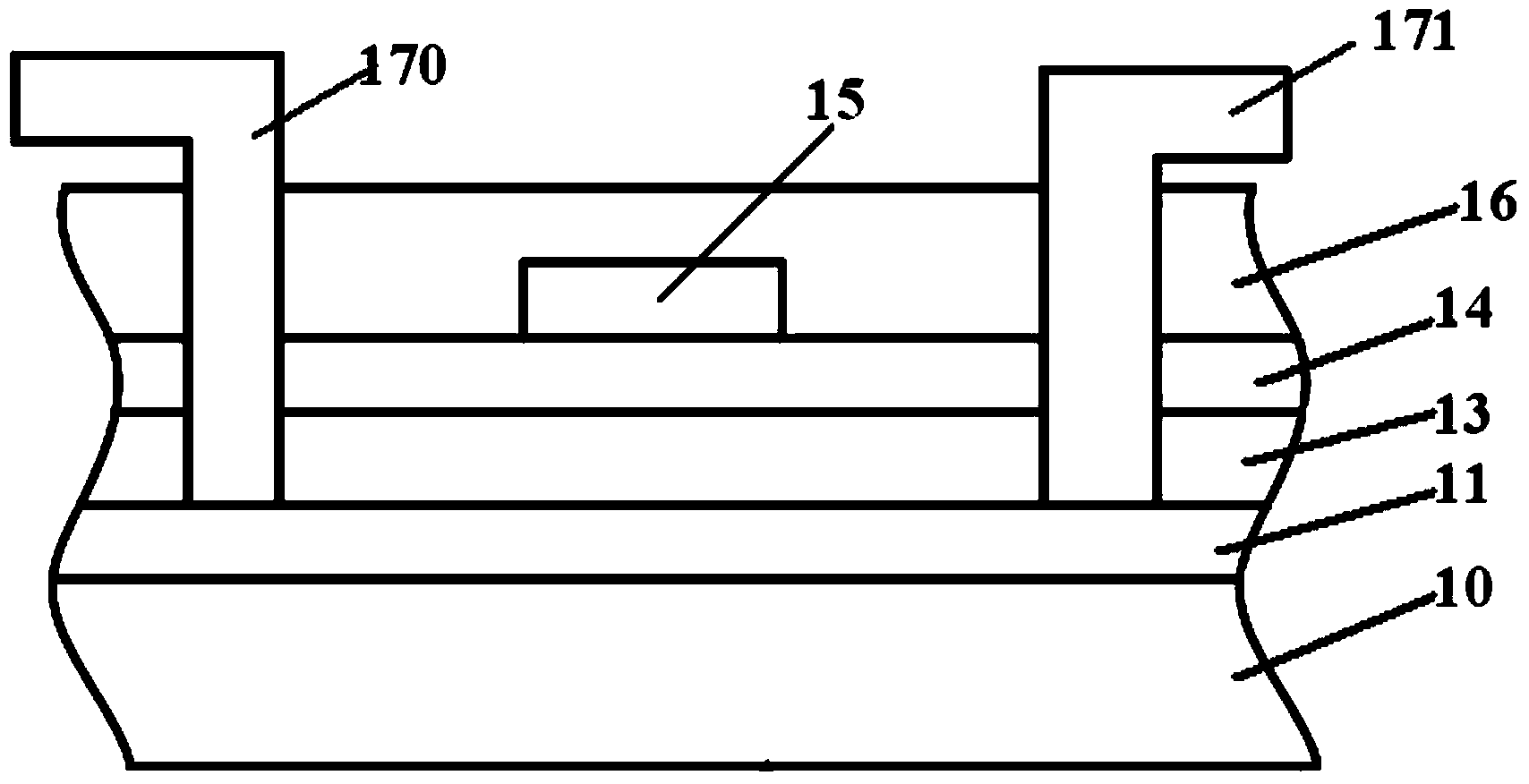

[0114] A low-temperature polysilicon thin film transistor array substrate with a top-gate structure can be manufactured through this embodiment, and the method for manufacturing the array substrate of this embodiment includes the following steps:

[0115] Step a1: providing a base substrate 10, and forming a buffer layer 11 on the base substrate 10;

[0116] Wherein, the base substrate 10 may be a glass substrate or a quartz substrate. Specifically, a plasma-enhanced chemical vapor deposition (PECVD) method can be used to deposit a thickness of about The buffer layer 11, wherein the material of the buffer layer can be selected from oxide, nitride or oxynitride, and the buffer layer can be a single-layer, double-layer or multi-layer structure. Specifically, the buffer layer may be SiNx, SiOx or Si(ON)x.

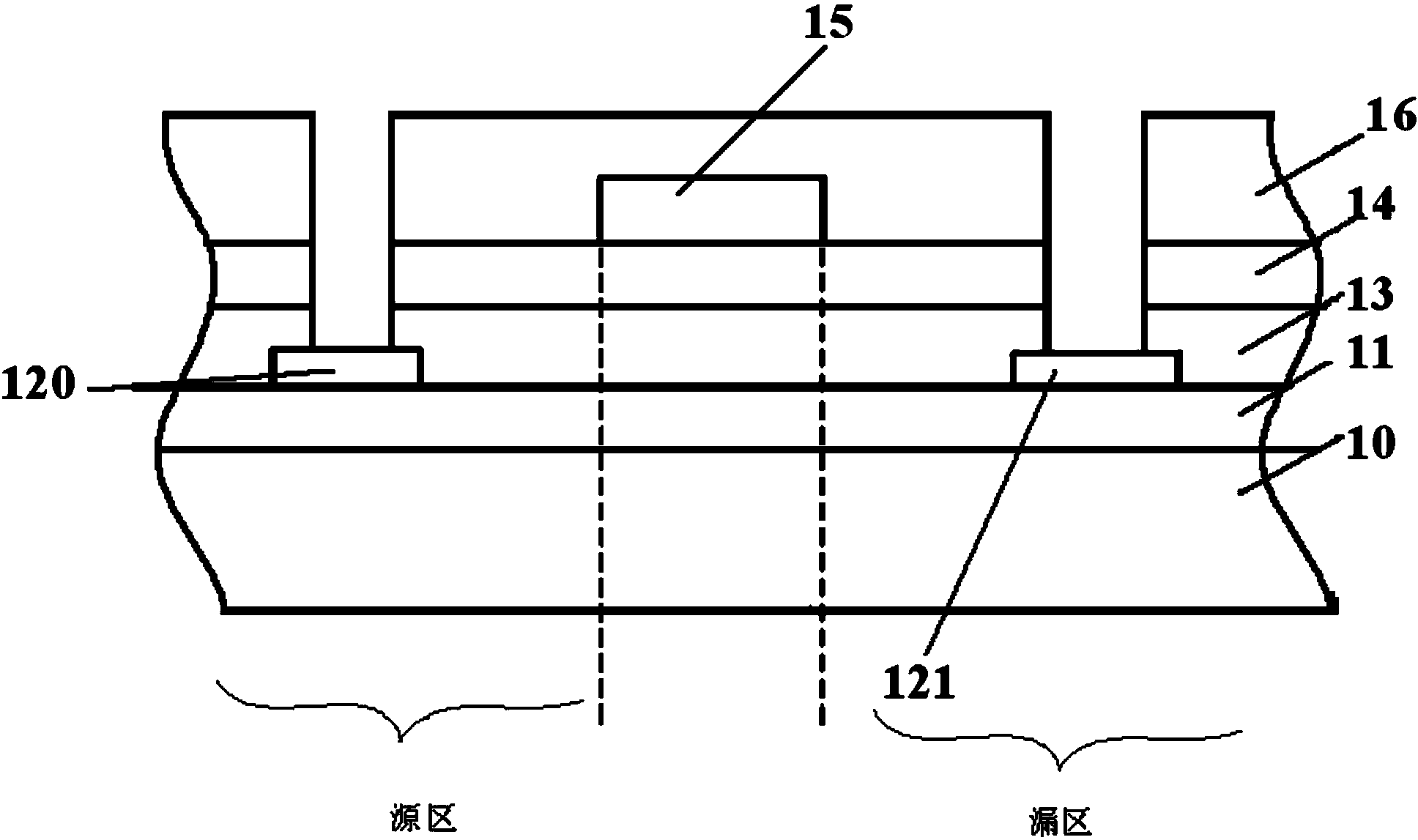

[0117] Step a2: forming conductive patterns 120, 121 capable of connecting to the active layer on the buffer layer 11 at positions corresponding to the contact holes;

[0...

Embodiment 2

[0133] Through this embodiment, a low-temperature polysilicon thin film transistor array substrate with a bottom gate structure can be manufactured, and the method for manufacturing the array substrate of this embodiment includes the following steps:

[0134] Step b1: providing a base substrate, and forming a buffer layer on the base substrate;

[0135] Wherein, the base substrate may be a glass substrate or a quartz substrate. Specifically, the plasma-enhanced chemical vapor deposition (PECVD) method can be used to deposit a thickness of about The buffer layer, wherein the material of the buffer layer can be selected from oxide, nitride or oxynitride, and the buffer layer can be a single-layer, double-layer or multi-layer structure. Specifically, the buffer layer may be SiNx, SiOx or Si(ON)x.

[0136] Step b2: forming patterns of gate electrodes and gate lines on the base substrate after step b1 through a patterning process;

[0137] Specifically, a layer with a thickness...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More