Device and method for CPU (central processing unit) to access local bus on basis of PCIE (peripheral component interface express) protocol

A local bus and protocol technology, applied in transmission systems, electrical components, instruments, etc., can solve the problems of poor scalability, high hardware implementation cost, low transmission rate, etc., achieve high reliability and performance, improve reading and writing efficiency, simplify The effect of sophistication

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0045] The present invention will be further described in detail below in conjunction with the accompanying drawings and specific embodiments.

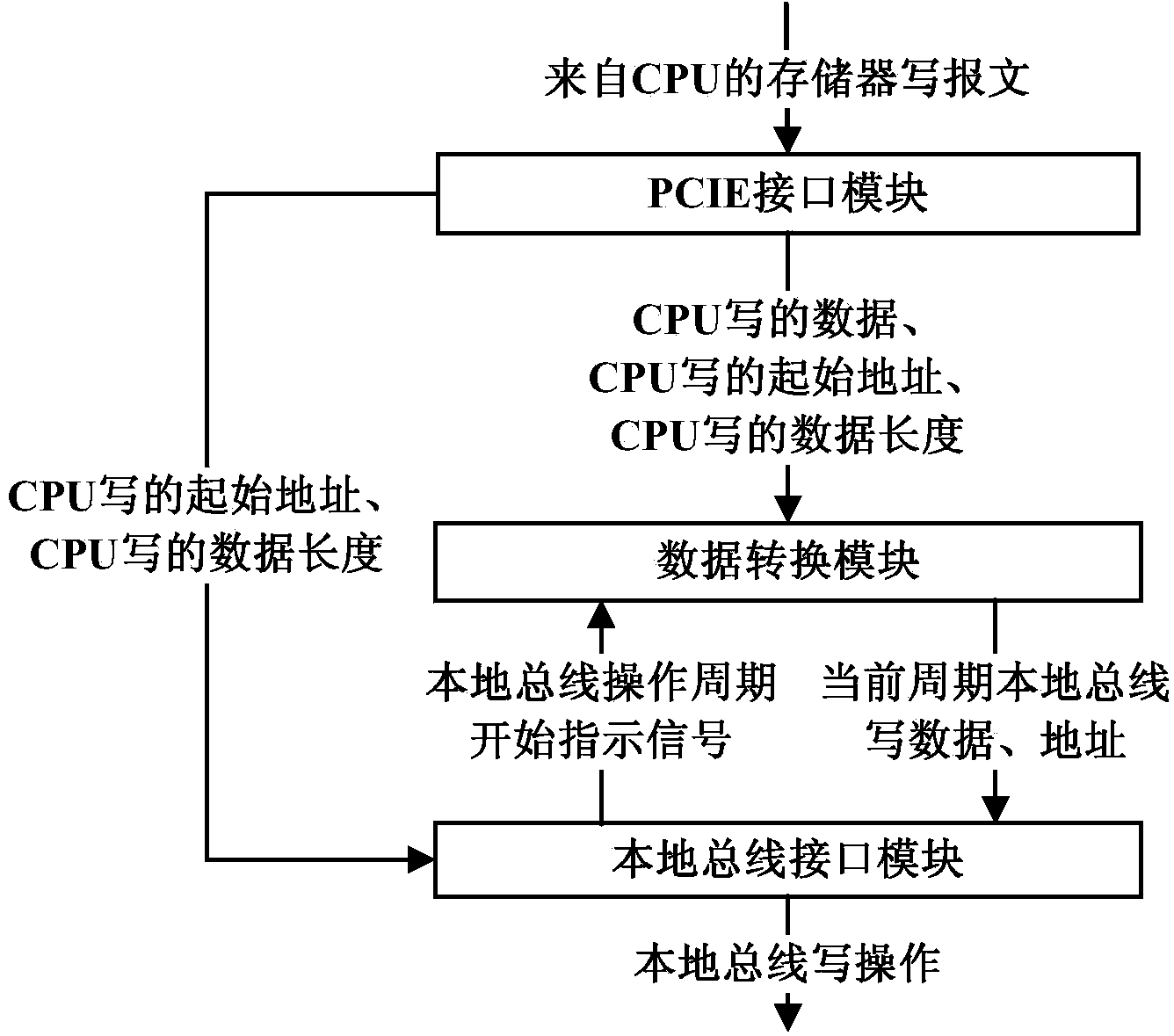

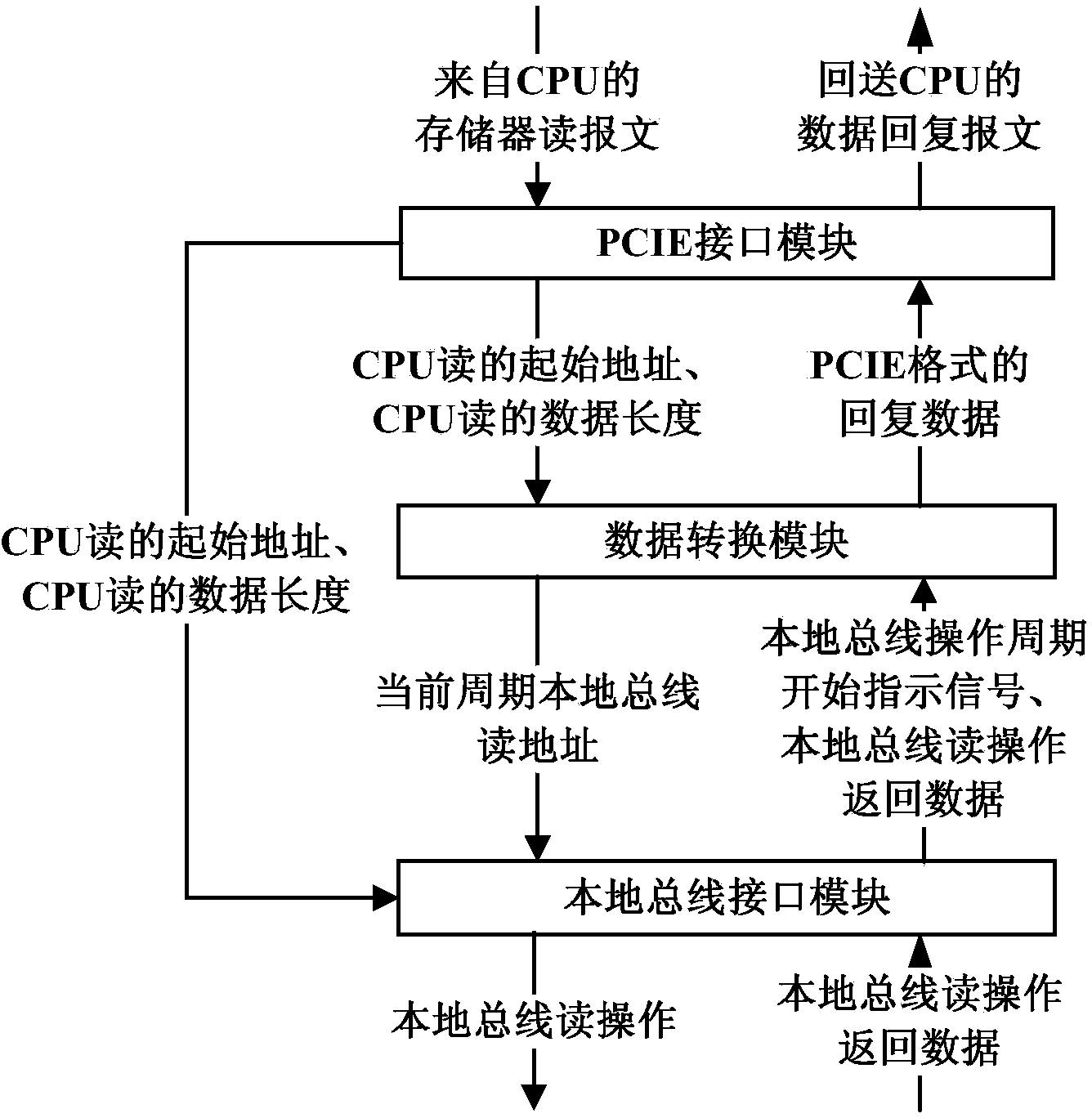

[0046] see figure 1 As shown, the embodiment of the present invention provides a kind of device based on PCIE agreement CPU access local bus, comprises PCIE interface module, data conversion module and local bus interface module, wherein:

[0047] The PCIE interface module is used to: implement the PCIE underlying protocol, so that the device works as a PCIE slave device (EP) under the PCIE system;

[0048] The data conversion module is used for: realizing the conversion between the data format carried by the PCIE read and write message and the local bus data format;

[0049] The local bus interface module is used for: simulating the timing of the traditional local bus, and realizing read and write access to FPGA local registers or external chips bridged by FPGA.

[0050] The PCIE interface module is designed according to the three-...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More