Waveguide electro-optic modulator and manufacturing method thereof

An electro-optic modulator and manufacturing method technology, which are applied in the fields of instruments, optics, nonlinear optics, etc., can solve the problems of reducing modulation efficiency, difficult to further reduce the half-wave voltage, disadvantageous to low-power electro-optic modulation devices, etc., so as to reduce the impact, The effect of improving modulation characteristics

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

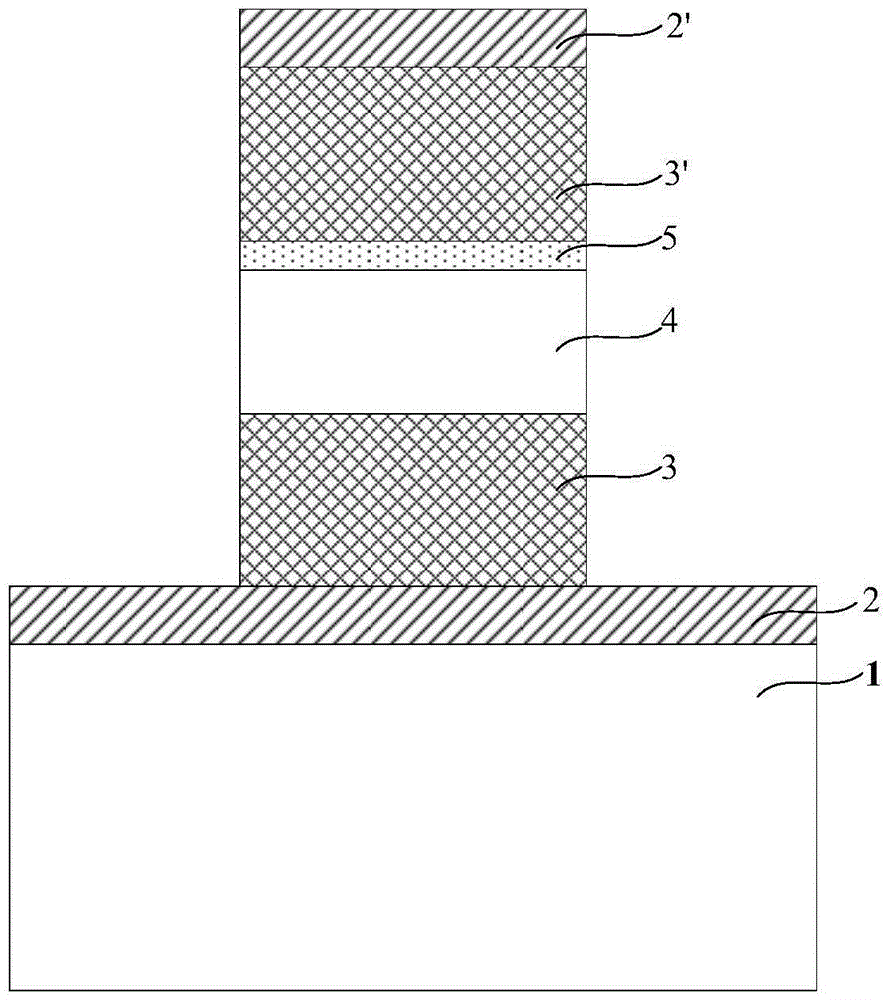

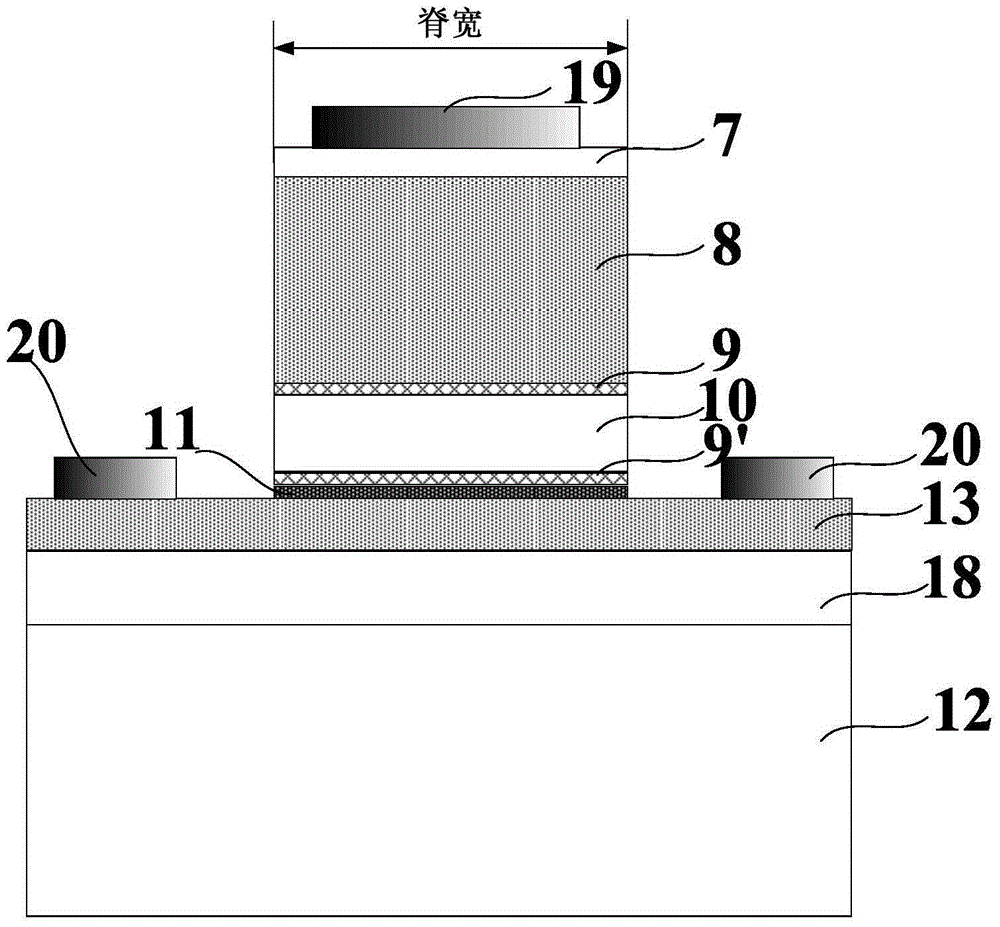

[0043] figure 2 It is a schematic structural diagram of a waveguide electro-optic modulator according to an embodiment of the present invention. Such as figure 2 As shown, it is InP-InGaAlAs / InAlAs-SiO 2 - Si (N-I-O-N type) ridge waveguide structure electro-optic modulator.

[0044] Specifically, there are two production methods.

[0045] The first production method includes the following steps:

[0046] Step 11, sequentially forming a device with an upper N-type semiconductor cladding layer, a semiconductor core layer and an insulator layer on the substrate;

[0047] Step 12. Surface-bond the insulator layer of the device on a (silicon-on-insulator) SOI substrate by surface bonding technology; wherein, the SOI substrate includes a silicon substrate, a silicon dioxide A silicon buried oxide layer and an N-type doped silicon layer, where the N-type doped silicon layer serves as a lower N-type semiconductor cladding layer;

[0048] Step 13, respectively forming an upper ...

Embodiment 2

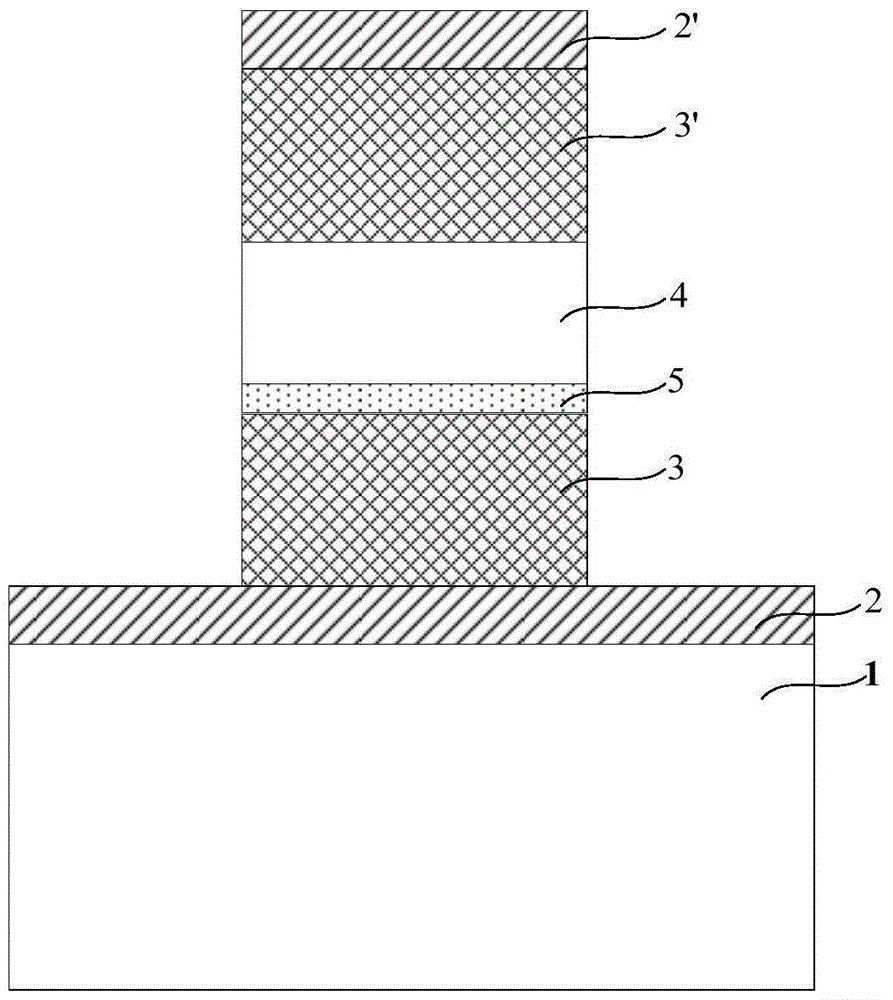

[0064] image 3It is a schematic structural diagram of a waveguide electro-optic modulator according to Embodiment 2 of the present invention. Such as image 3 As shown, it is InP-InGaAsP / InP-Al 2 o 3 - InP (N-I-O-N type) ridge waveguide structure electro-optic modulator.

[0065] The preparation method comprises the following steps:

[0066] Step 31, growing a lower N-type semiconductor cladding layer, a semiconductor core layer, a semiconductor layer containing Al, and an upper N-type semiconductor cladding layer sequentially on the substrate;

[0067] Step 32. Oxidize or nitride the Al-containing semiconductor layer into Al2O3 by lateral oxidation or nitridation 2 o 3 or aluminum nitride AlN insulator layer;

[0068] Step 33, respectively forming an upper electrode on the surface of the upper N-type doped ohmic contact layer, and forming a lower electrode on the surface of the lower N-type doped ohmic contact layer.

[0069] Specifically, the epitaxial materials of ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| length | aaaaa | aaaaa |

| length | aaaaa | aaaaa |

| width | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More