Dynamic bottleneck analytical method of semiconductor production line

A bottleneck analysis and production line technology, applied in the direction of comprehensive factory control, electrical program control, comprehensive factory control, etc., can solve the problems of reducing the timeliness, backwardness and lack of production control

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

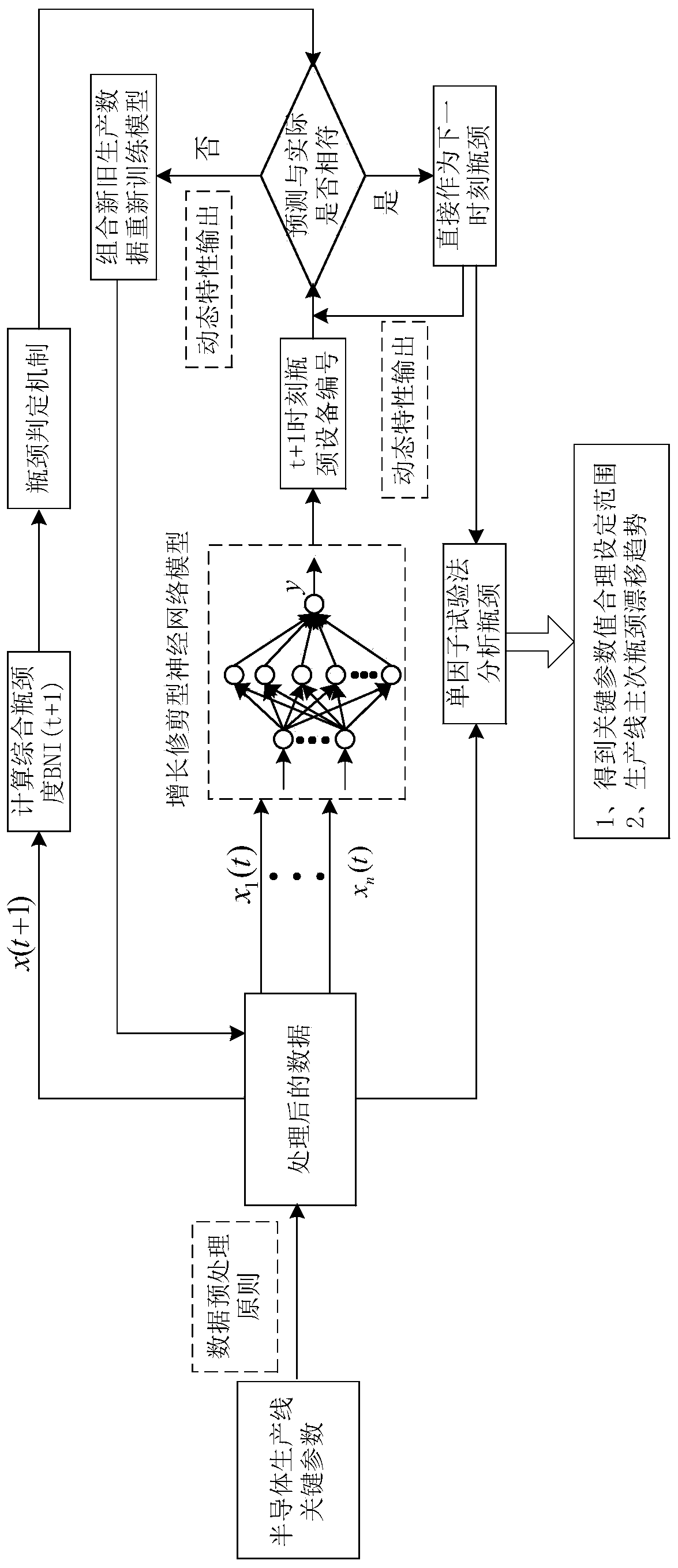

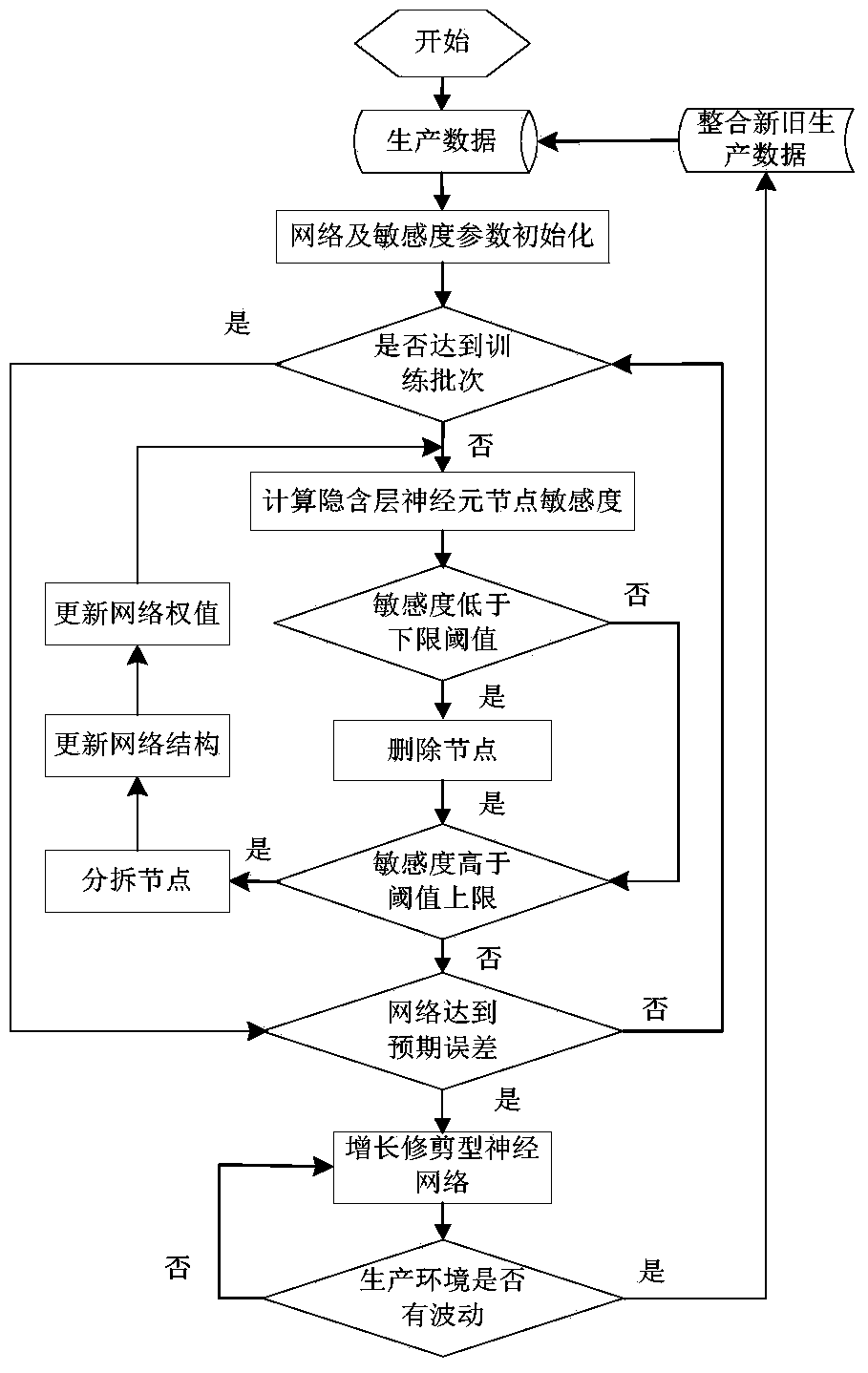

Method used

Image

Examples

Embodiment Construction

[0094] The content of the present invention will be described in detail below in conjunction with the accompanying drawings and specific examples.

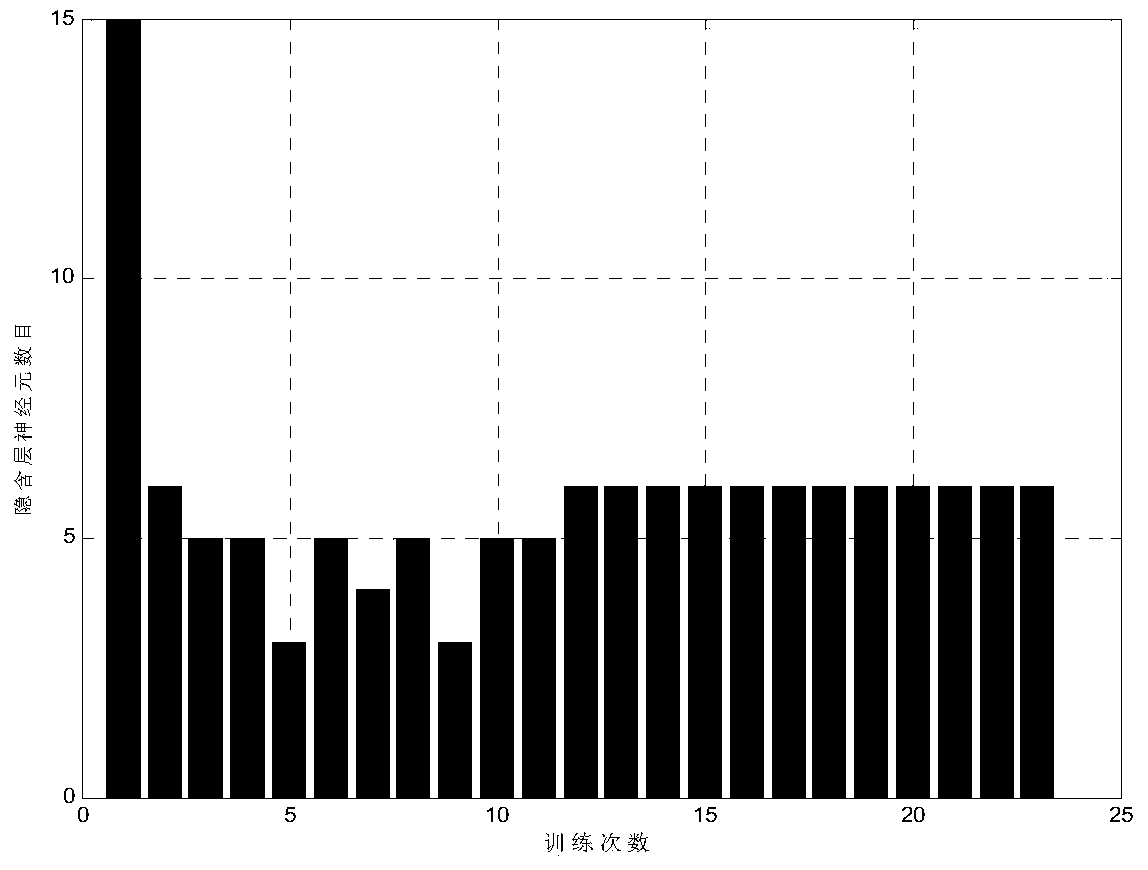

[0095] Taking a semiconductor production line standard model HP24 as an example, the technical solution adopted by the present invention is analyzed in detail, wherein HP24 is a model developed by the silicon wafer production technology center. This model has 24 equipment groups, with a total of 72 equipment, including 4 batch processing equipment and 68 single-piece processing equipment, processing 3 types of products in total.

[0096] This paper constructs the HP24 semiconductor production line model on the Plant Simulation simulation platform, adopts the fixed feeding strategy CONWIP, sets the WIP value between 25 lots and 35 lots, and adopts the FLNQ (Longest Lots at the Next Queue) rule to carry out the simulation operation, the simulation time is 3 years (25920 hours), and the pre-simulation time is half a year (4320 hours)...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More