Method for encapsulating chips and support plates

A packaging method and chip technology, which is applied in the manufacture of electrical components, electrical solid devices, semiconductor/solid devices, etc., can solve the problems of uncompetitiveness, cost increase, and expensive packaging molding materials, so as to avoid bending, Effects of saving cost and reducing total thickness

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0047] The implementation of the invention will be described in more detail below in conjunction with the drawings and component symbols, so that those skilled in the art can implement it after studying this specification.

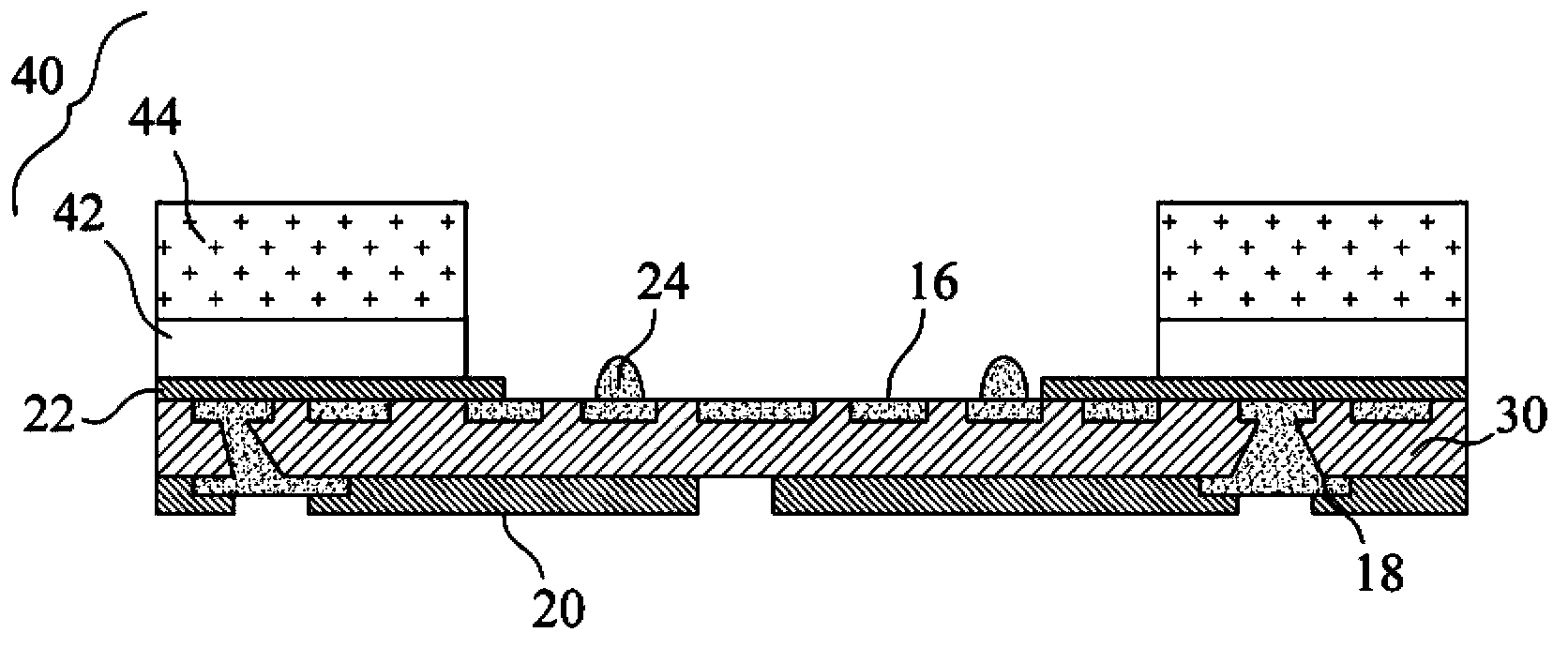

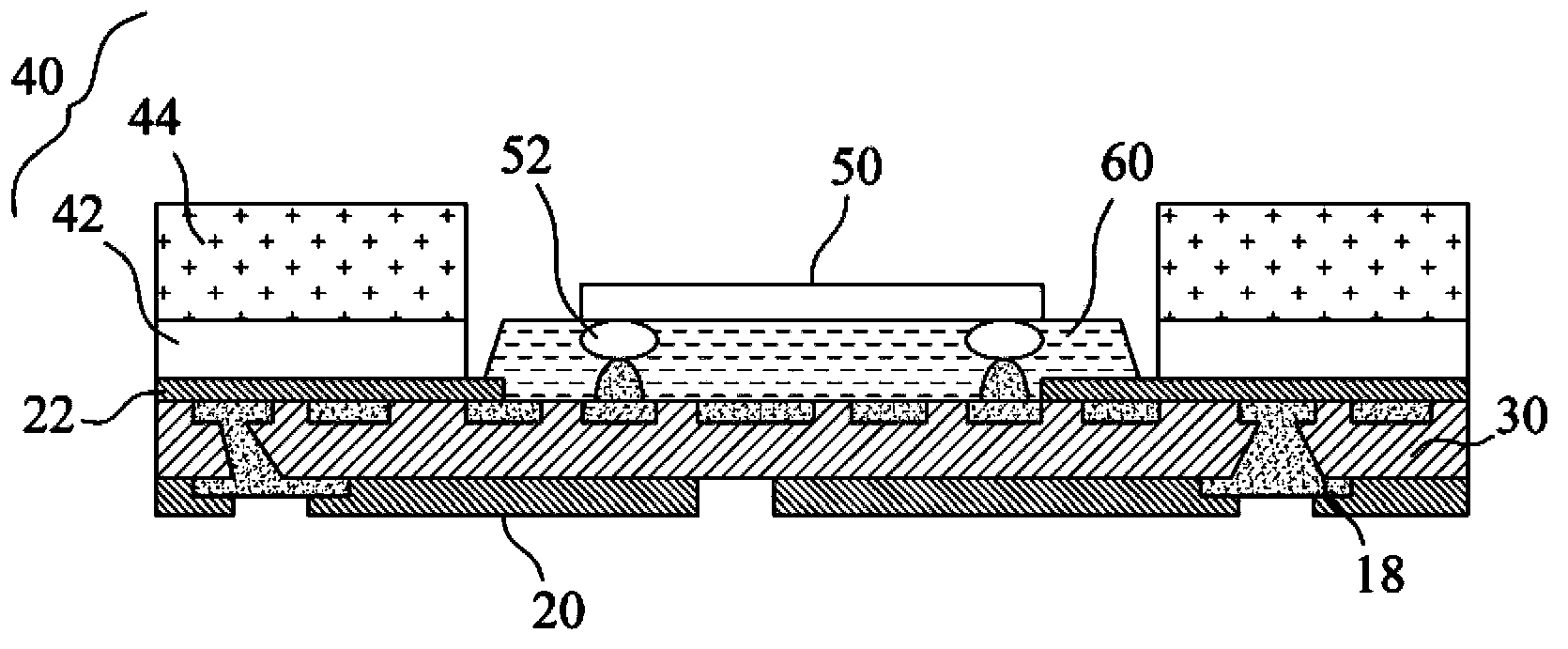

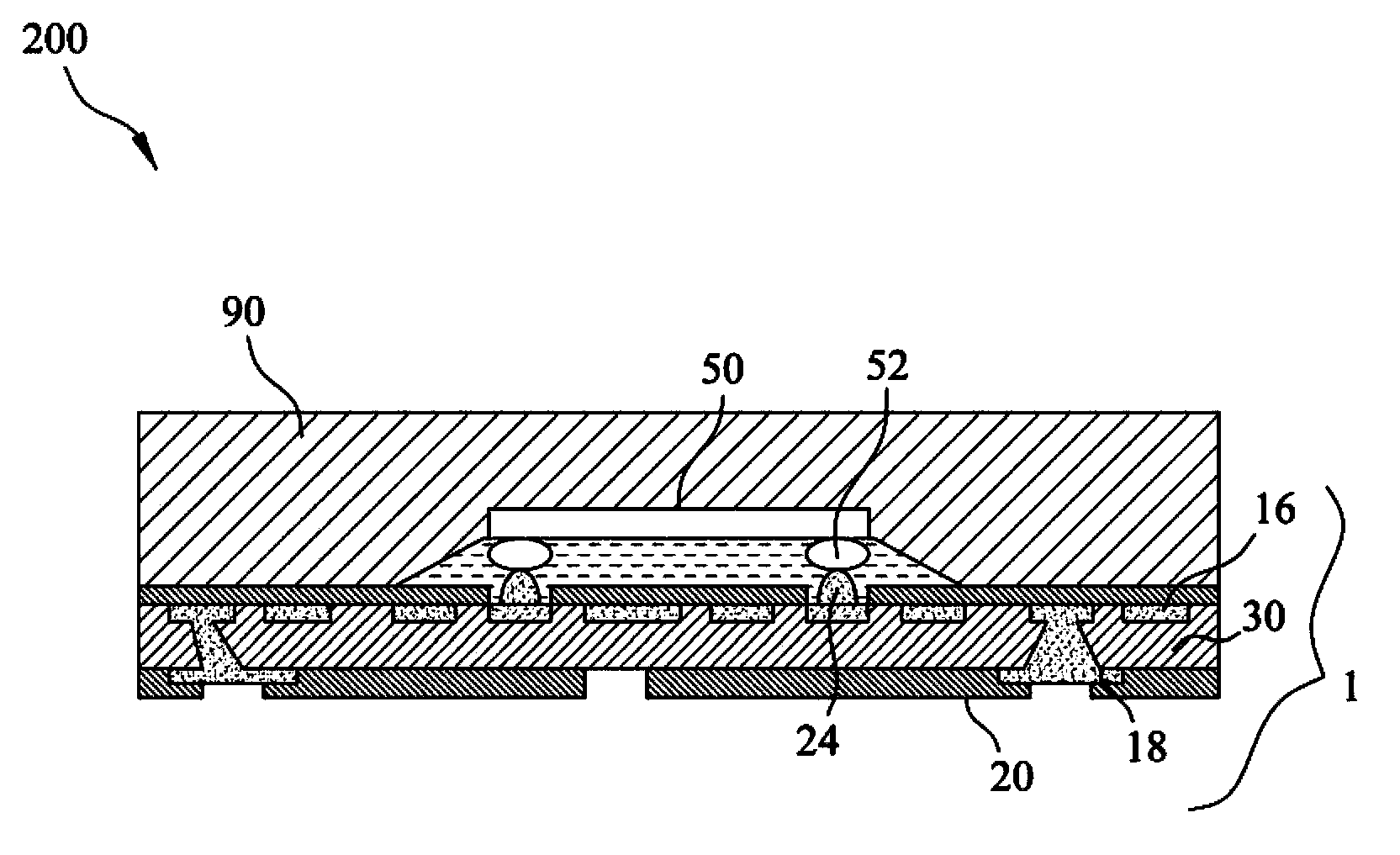

[0048] see figure 2 , is a flow chart of the chip and carrier board packaging method of the present invention. The chip and carrier packaging method S1 of the present invention includes a thin chip carrier manufacturing step S10, a structural layer manufacturing step S20, a chip connection step S30, and an injection material filling step S40. Thin chip carrier production step S10 includes substrate preparation step S11, partial etching step S13, image transfer step S15, layer build-up step S17, and carrier removal and etching step S19, the detailed method will be coordinated with Figure 3A to Figure 3K to explain step by step.

[0049] like Figure 3A As shown, the substrate preparation step S11 is to prepare a carrier 100 with a copper layer 10, the ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More