Method for forming shallow trench isolation region

A shallow trench isolation area and trench technology, which is applied in electrical components, semiconductor/solid-state device manufacturing, circuits, etc., can solve the problem of incomplete etching of polysilicon gates, reduce adhesion, increase filling density, and improve performance Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0028] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be further described in detail below with reference to the accompanying drawings and examples.

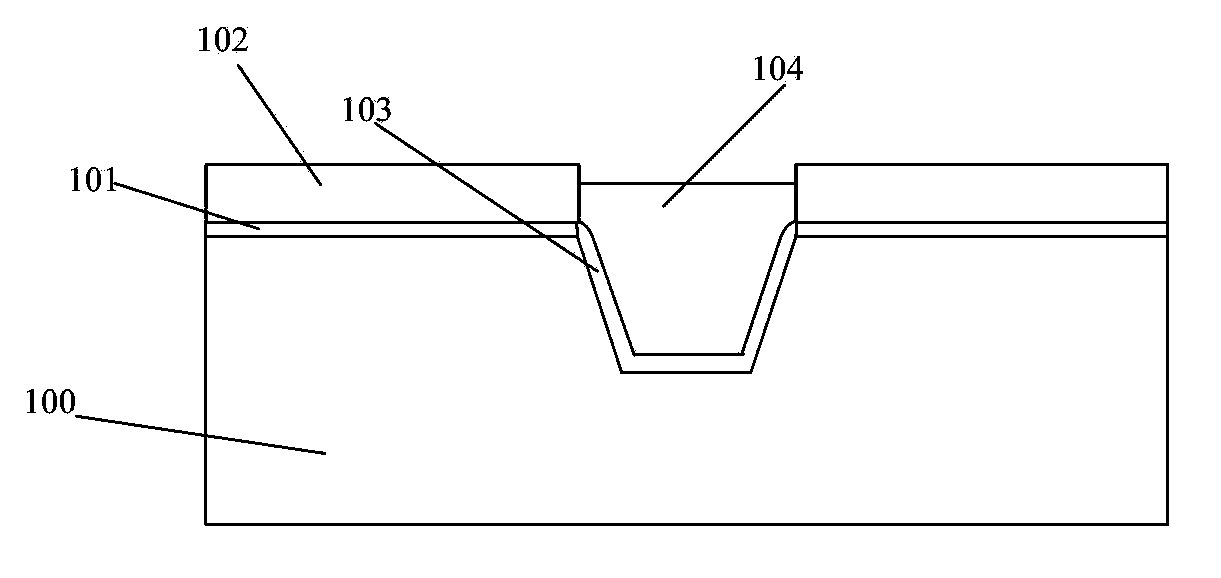

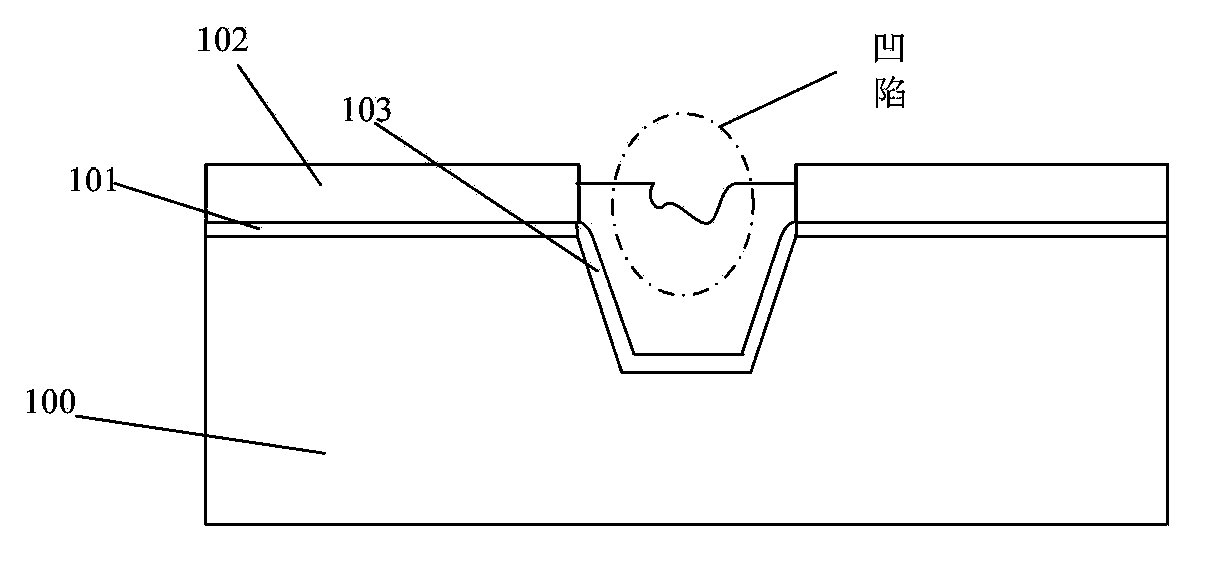

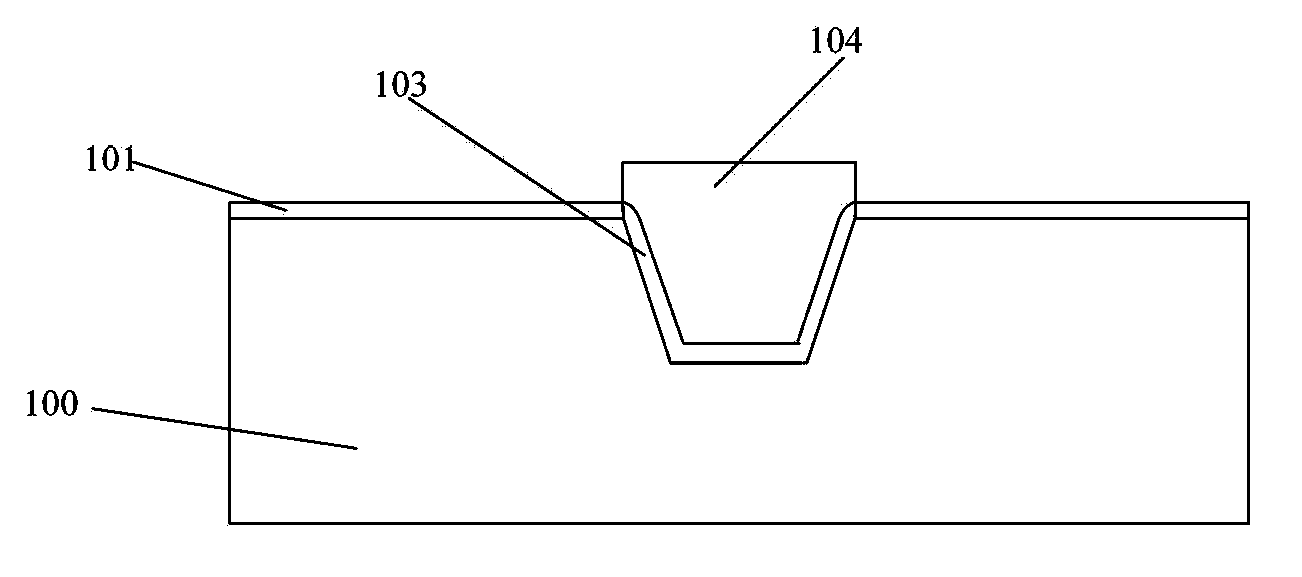

[0029] Please refer to the schematic diagram of the specific manufacturing process of the shallow trench isolation region of the present invention Figure 2a to Figure 2e , the flow chart of the specific production method is as follows figure 2 shown, including the following steps:

[0030] Step 21, sequentially forming an isolation oxide layer 101 and a silicon nitride layer 102 on the semiconductor substrate 100;

[0031] Specifically, an isolation oxide layer 101 is thermally oxidized and grown on the semiconductor substrate 100 to protect the active region from chemical contamination during the subsequent removal of the silicon nitride layer, and to serve as a barrier between the silicon nitride layer and the silicon substrate. Stress buffer laye...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com