Clock synchronization error compensation method of FC network

A clock synchronization and synchronization error technology, which is applied in the field of computer communication, can solve problems such as increasing the complexity of upper-layer software for time information application, client clock jumping forward or backward, reducing the generality of clock synchronization functions, etc., to achieve Achieve smooth transition and linear monotonous incremental change, realize monotonous linear change, and facilitate application

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

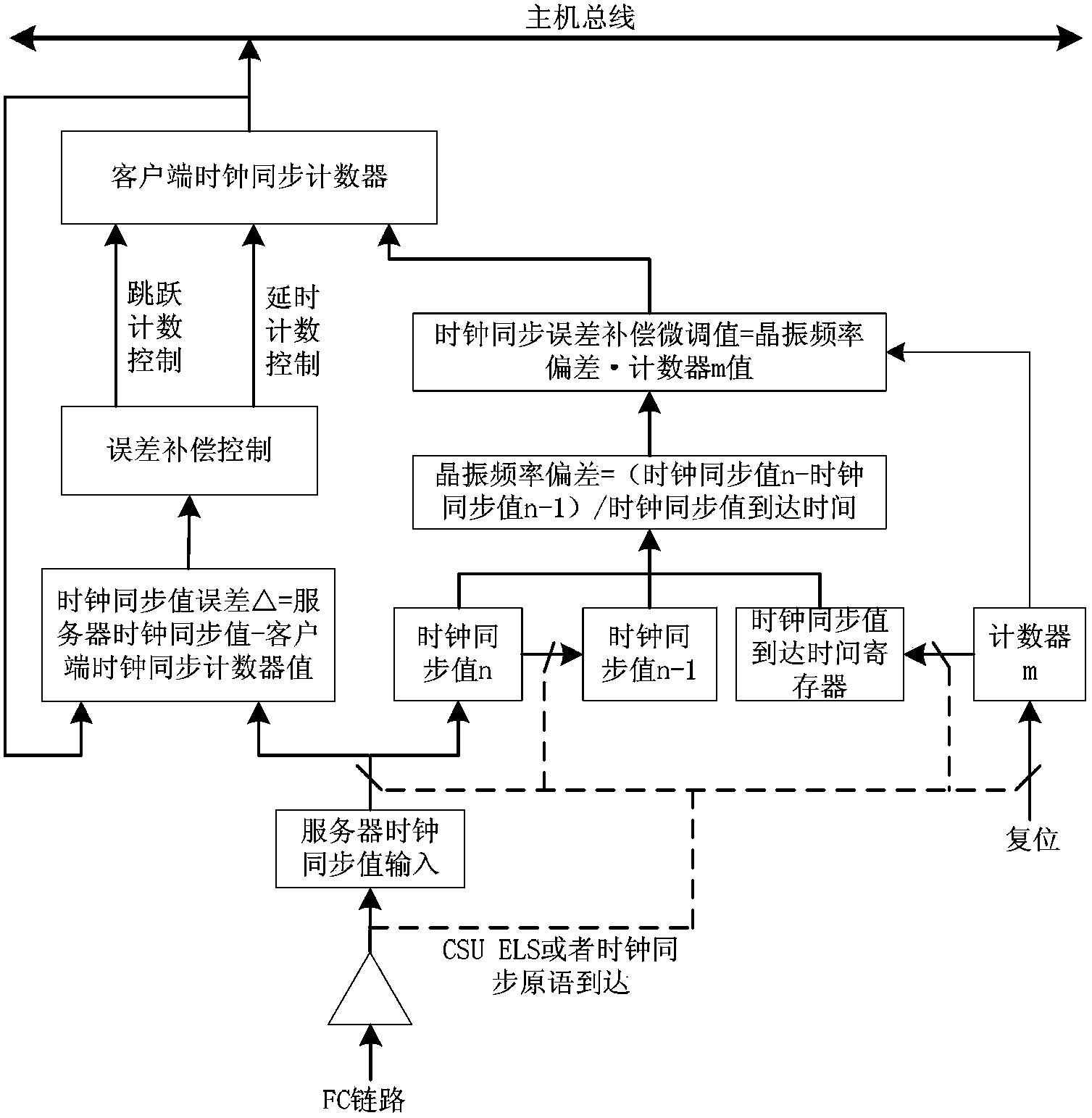

[0041] The present invention provides a kind of FC network clock synchronization error compensation method, and this method comprises the following steps:

[0042] 1) The client receives the CSU ELS frame or the clock synchronization primitive signal sent by the server;

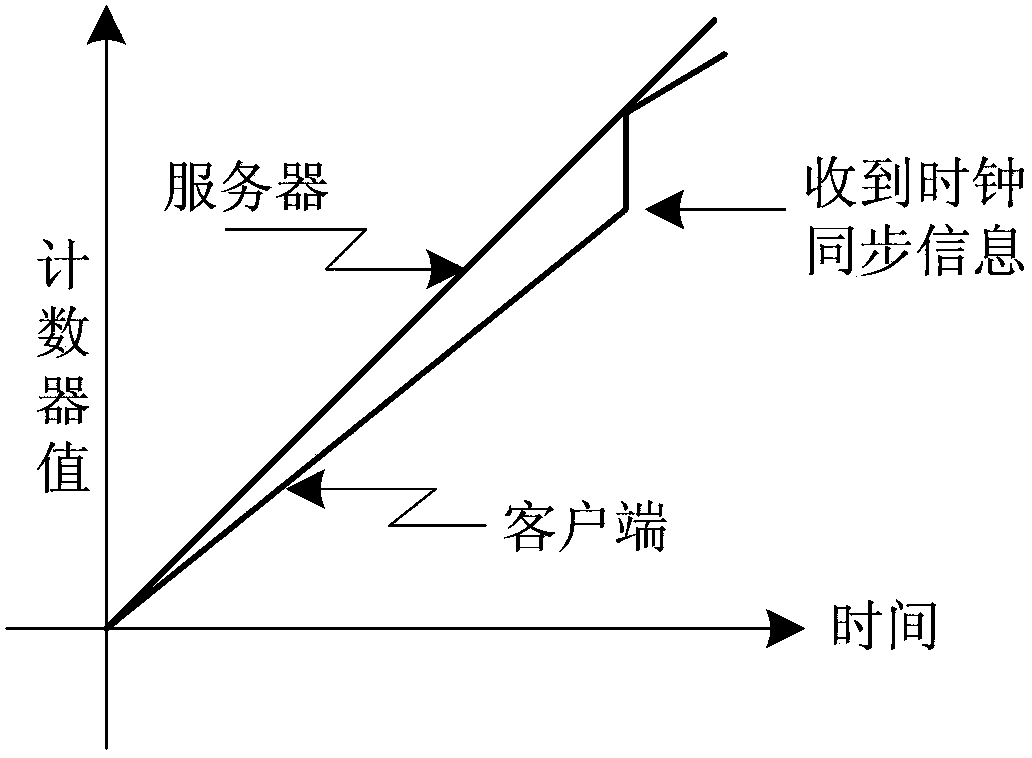

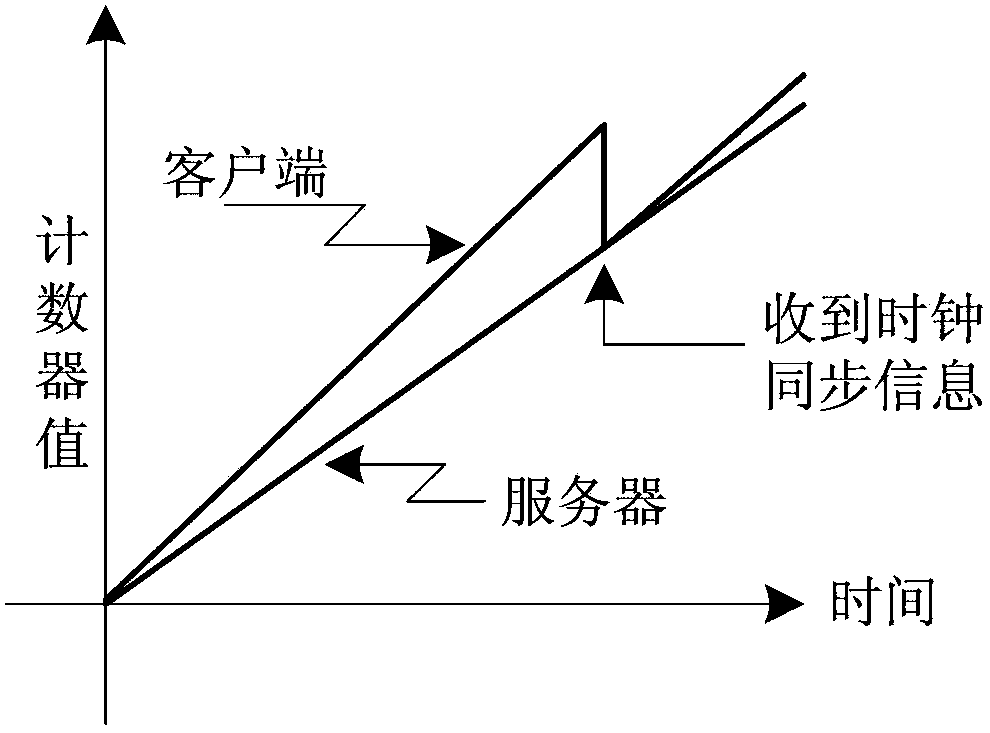

[0043] 2) Determine whether the client clock synchronization counter is consistent with the server clock synchronization counter according to the CSU ELS frame or the clock synchronization primitive signal. If they are consistent, exit the compensation; if they are not consistent, proceed to step 3); Inconsistent synchronization counters include: the clock frequency of the client clock synchronization counter is slower than that of the server clock synchronization counter or the clock frequency of the client clock synchronization counter is faster than the clock frequency of the server clock synchronization counter;

[0044] 3) Obtain the theoretical difference between the server clock synchronization counter...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More