MTP memory cell

A technology of memory cells and capacitors, which is used in information storage, static memory, read-only memory, etc., and can solve problems such as punchthrough and punch-through.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

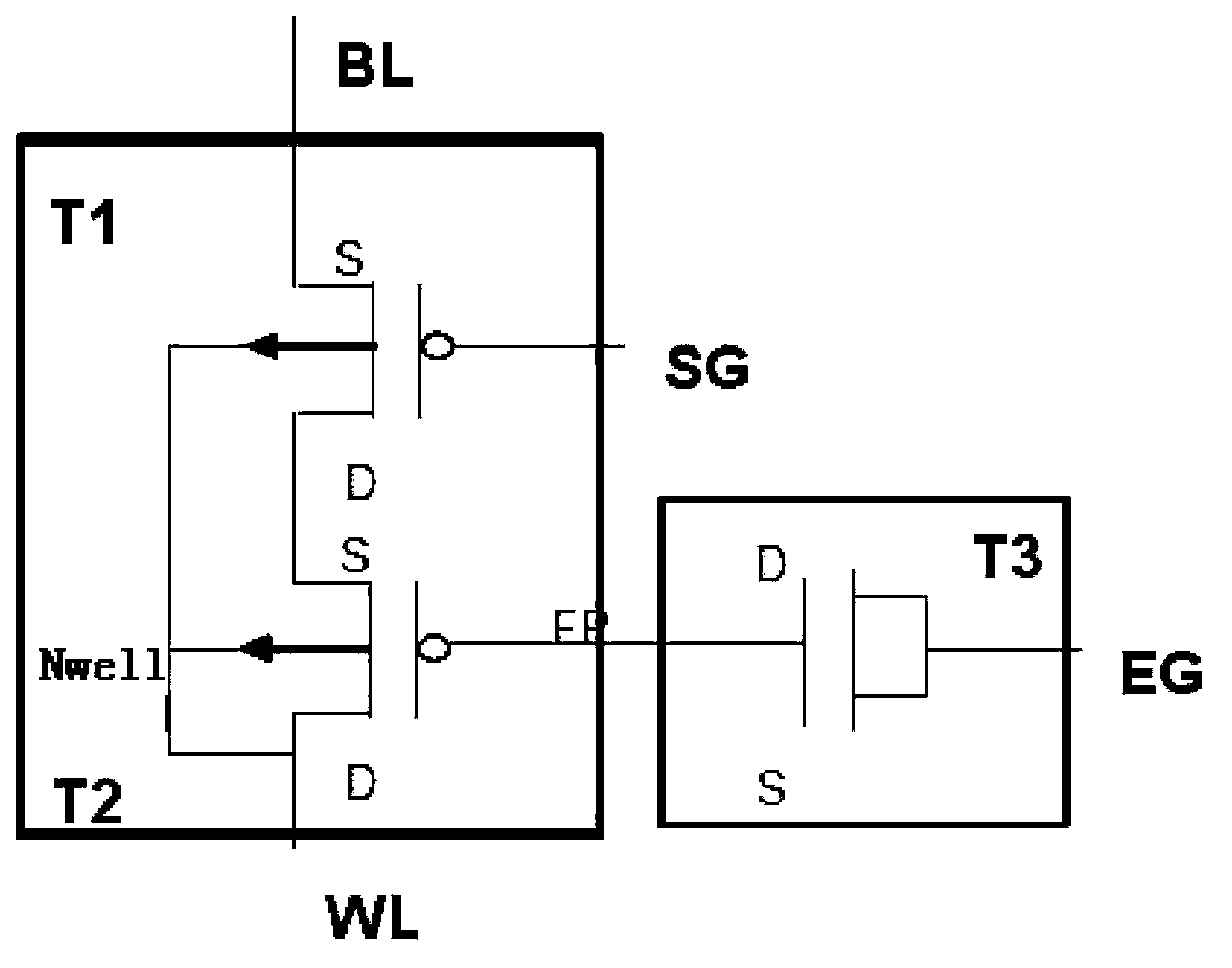

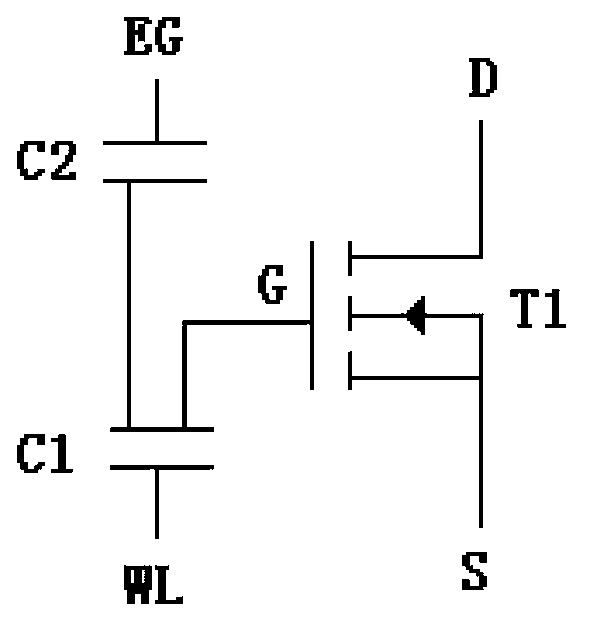

[0051] Such as image 3 As shown, the MTP storage unit of the present invention includes: the selection transistor N1 is an NMOS transistor, the programming capacitor C1 is an NWC capacitor, and the erasing capacitor C2 is a MIP capacitor;

[0052] Selecting the drain terminal D of the transistor N1 as the bit line BL of the MTP storage unit, and selecting the source terminal S of the transistor N1 as the source terminal SG of the entire MTP storage unit;

[0053] The upper plate of the programming capacitor C1 is connected to the gate G of the selection transistor N1, which is the same floating gate;

[0054] The lower plate of the programming capacitor C1 is the word line WL of the entire MTP memory cell.

[0055] The upper plate of the erasing capacitor C2 is used as the erasing terminal EG of the MTP;

[0056] The lower plate of the erasing capacitor C2 is connected to the upper plate of the programming capacitor C1, which are the same floating gate.

[0057] Wherein, the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More