Transistors and methods of forming them

A technology of transistors and semiconductors, which is applied in the manufacture of transistors, semiconductor devices, semiconductor/solid-state devices, etc., can solve problems such as unfavorable transistor performance, and achieve the effects of easy control, simple process, and improved performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

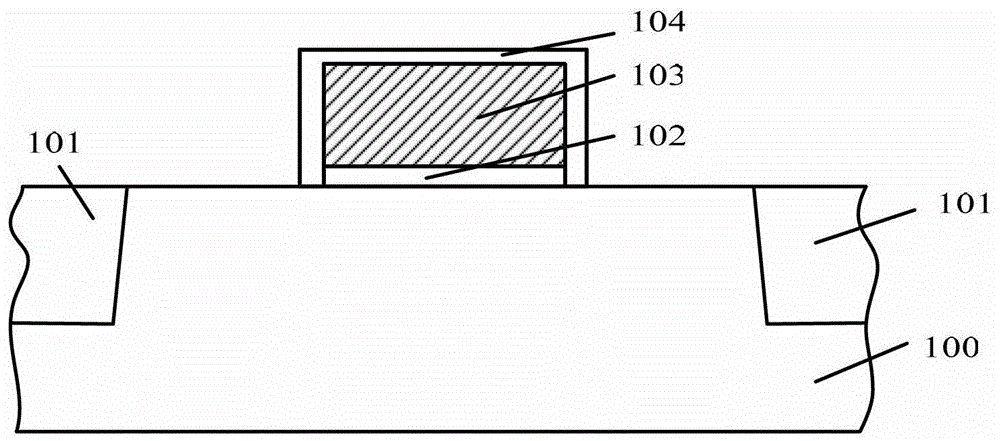

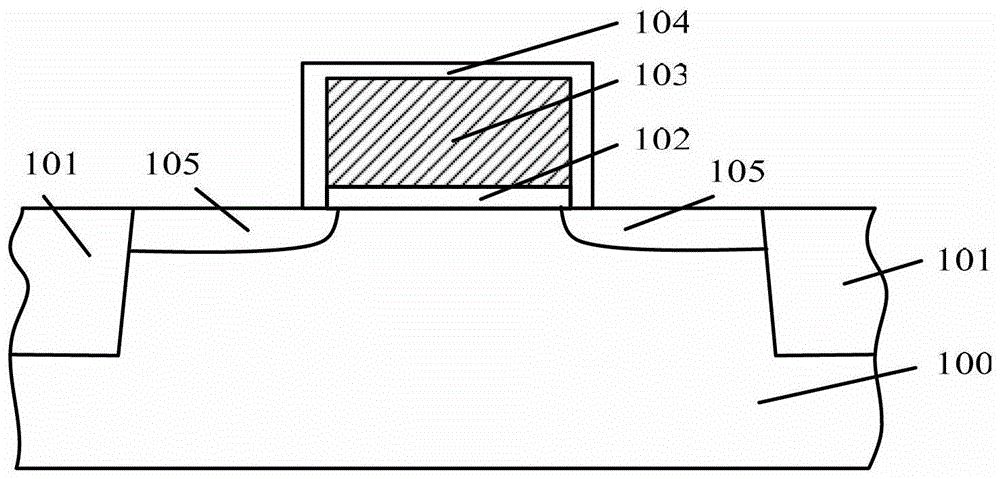

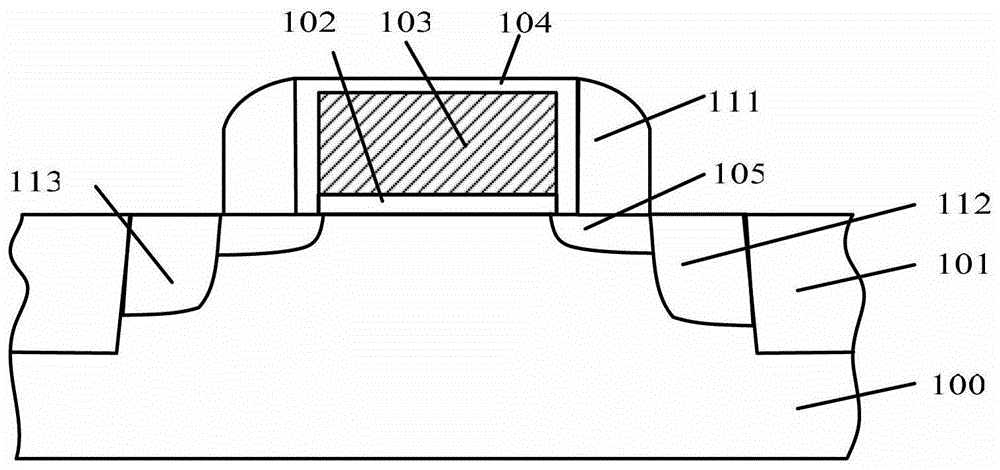

[0034] The work function of the gate electrode of the conventionally formed transistor is constant across the channel region from the source region to the drain region, so that the threshold voltage from the source region to the drain region is constant, and at a fixed gate voltage, the channel The density of carriers in the channel region is the same, which is not conducive to the improvement of transistor performance.

[0035] To this end, the inventor proposes a transistor, the gate electrode of the transistor has a middle region and edge regions located on both sides of the middle region, the gate electrode of the middle region is doped with work function adjusting ions, so that the middle region of the gate electrode The work function of the gate electrode is different from the work function of the edge region of the gate electrode, so that the threshold voltage from the source region to the drain region is different, and at a fixed gate voltage, the total number of carrie...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More