Cache design method for reducing STT-RAM power consumption by utilizing temperature difference on three-dimensional integrated circuit chip

A technology of an integrated circuit and a design method, applied in the design field of magnetic tunnel junction power consumption, can solve the problems of large write power consumption and large write delay, reduce write power consumption, improve performance, optimize write current and write effect of time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

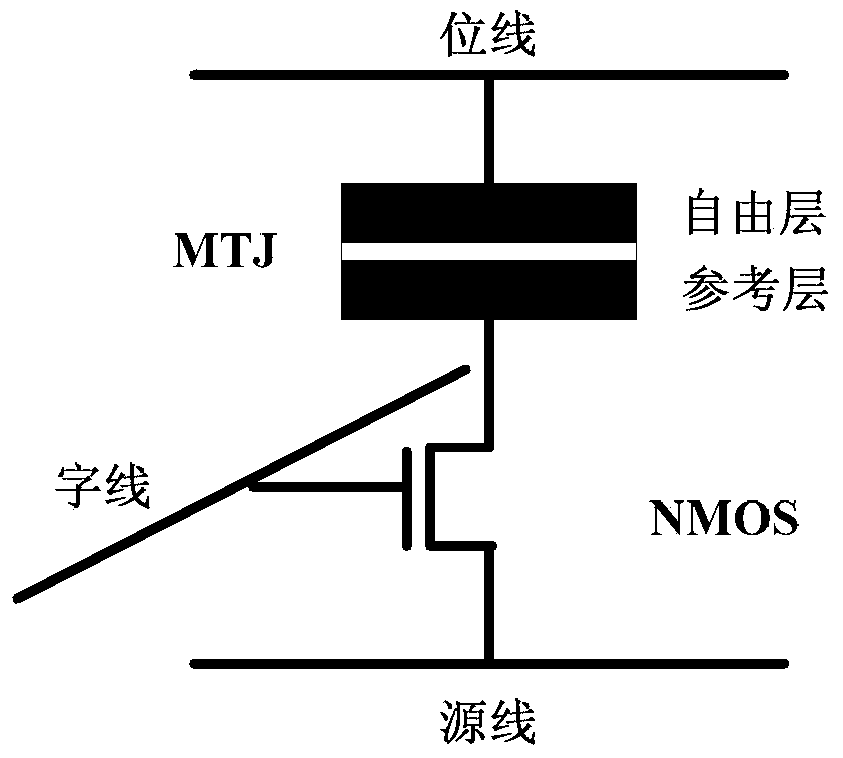

[0027] The working principle of the STT-RAM storage unit involved in the present invention is as follows: figure 1 shown. STT-RAM storage unit generally adopts 1T1J (1Transistor and 1MTJ). Transistors control access to MTJ data. The structure of MTJ is divided into free layer, reference layer and intermediate oxide layer. Wherein the magnetization direction of the reference layer is fixed. By applying currents in different directions to the MTJ, the magnetization direction of the free layer can be changed. If the magnetization direction of the free layer is the same as that of the reference layer, the resistance value of the MTJ becomes smaller, and it can be regarded as storing logic "0". Otherwise, a logic "1" is stored. When reading the data of the memory cell, the word line is set to be valid, and all small voltages of 0.1V are applied between the bit line BL and the source line SL. According to the similarities and differences of the magnetization directions of the ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More