Writing acceleration method and system for phase change memory

A technology of phase change memory and acceleration system, applied in static memory, digital memory information, information storage, etc., can solve the problems of slow SET operation speed and performance degradation of phase change memory, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

specific Embodiment 1

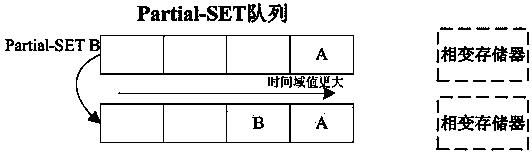

[0166] Such as Figure 13A , the initial state of the Partial-SET queue is: only one item contains the information of A, and there are three empty items. When B's write request is written according to the Partial-SET method, the corresponding Partial-SET queue is not full, and there is no item with the same address as B in the current queue, therefore, insert B into the Partial-SET queue, and B The time field of the item is initialized to zero. After performing this series of operations, the status of the Partial-SET queue is: two items are occupied, the value of the time domain of item A is the largest, and the value of the time domain of item B is the second, which is placed in the second item.

specific Embodiment 2

[0167] Such as Figure 13B , the initial state of the Partial-SET queue is: there are three items containing the information of A, B, and C respectively, the time domain values of these three items decrease in turn, and there is one empty item. The write request of A chooses to use the pulse of Partial-SET to execute the write "1" operation. The item of A in the current queue already exists, so the item of A is deleted from the current position, and the new item of A is inserted at the end of the queue. At this time, the item of A The time domain value is zero. After executing this series of operations, the state of the Partial-SET queue is: there are items B, C, and A, and the values of the time domains of these three items decrease in turn, and the value of the time domain of item B is the largest.

specific Embodiment 3

[0168] Such as Figure 13C , the initial state of the Partial-SET queue is: the information of A, B, and C is stored, and the value of the time domain decreases in turn, and the value of the time domain of A is the largest. The memory storage bank is in the idle state, the request queue status is empty, and the prediction result of the predictor is that the current memory storage bank idle interval is long, delete item A from the Partial-SET queue, and execute the corresponding row A in the phase change memory Compensation for SET operations. After executing this series of operations, the state of the Partial-SET queue is: there are items B and C, and the time domain values of these two items decrease in turn, and the value of the time domain of item B is the largest. The state of row A in the phase change memory is a reliable complete SET state.

[0169] In summary, compared with the prior art, the write acceleration method of the phase change memory of the present invent...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More