Through silicon via repair circuit

A TSV and circuit technology, applied in the field of chip stacking, can solve problems such as transmission errors and achieve the effect of preventing drift

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

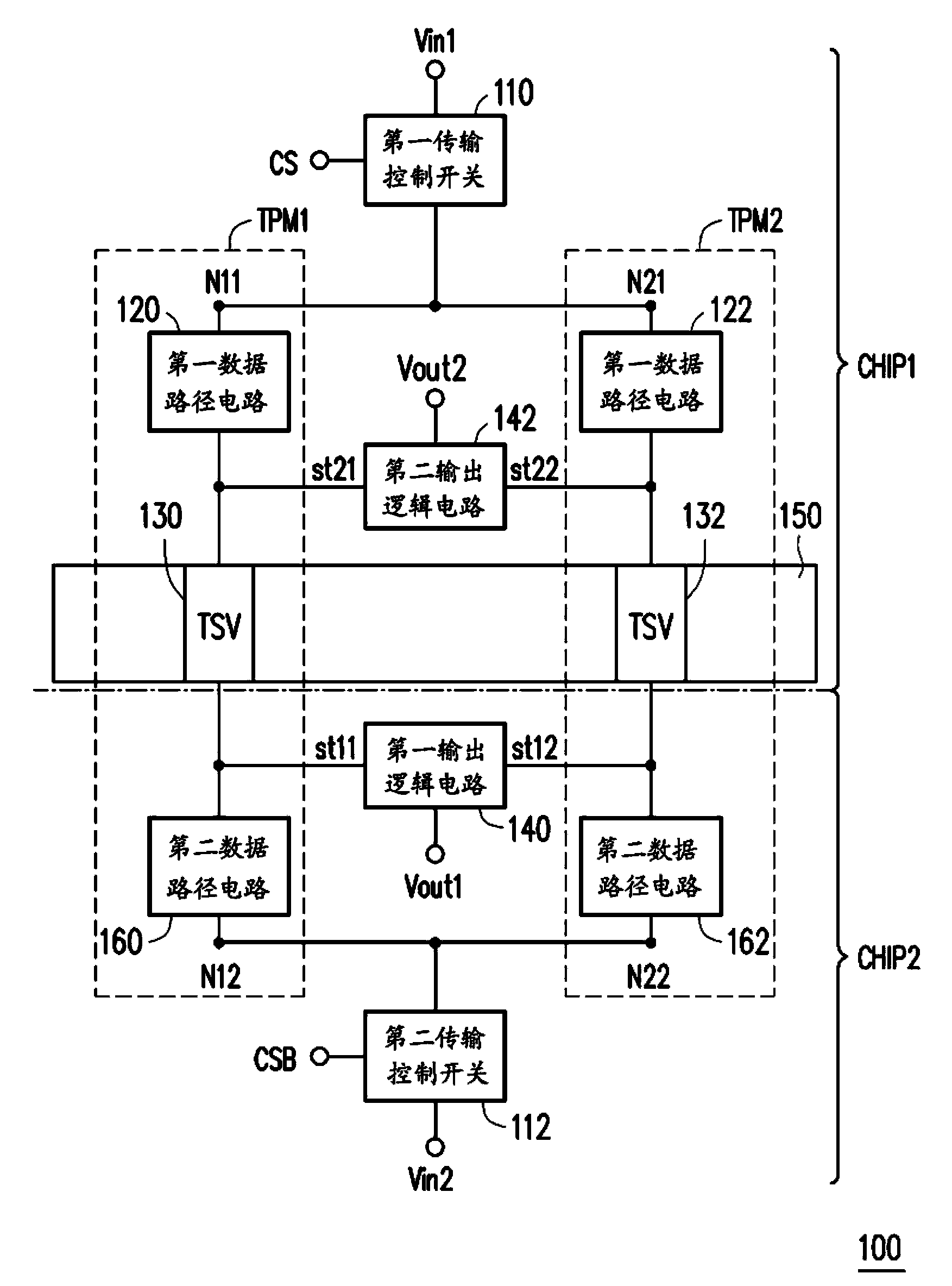

[0075] figure 2 It is a schematic diagram illustrating a TSV repair circuit 100 according to the first embodiment of the present application. Such as figure 2 As shown, the TSV repair circuit 100 that can be used in semiconductor devices includes at least two chips CHIP1, CHIP2 stacked up and down, a first transmission control switch 110 and a second transmission control switch 112, at least two transmission path modules TPM1 and TPM2, the first output logic circuit 140 and the second output logic circuit 142 .

[0076] figure 2 Although it is disclosed that the first chip CHIP1 and the second chip CHIP2 are stacked on top of each other, those who apply the embodiment of the present application should be able to form a semiconductor device (for example, a three-dimensional chip) by stacking a plurality of chips on top of each other, and let two of them think The chips to transmit data are respectively the first chip CHIP1 and the second chip CHIP2, and one or more layers...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More