Mixed interconnection Mesh topological structure for on-chip network and routing algorithm thereof

A topology and network-on-chip technology, applied in data exchange networks, computing, computers, etc., can solve problems such as suboptimal bandwidth, delay performance, large delay, and central area congestion, and reduce network hotspots and congestion.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

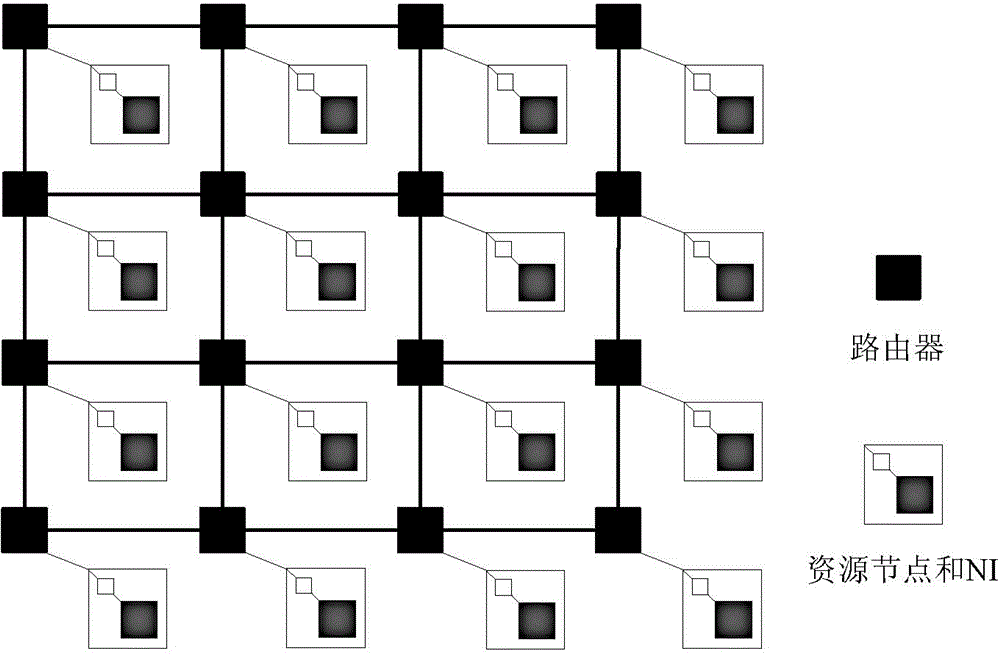

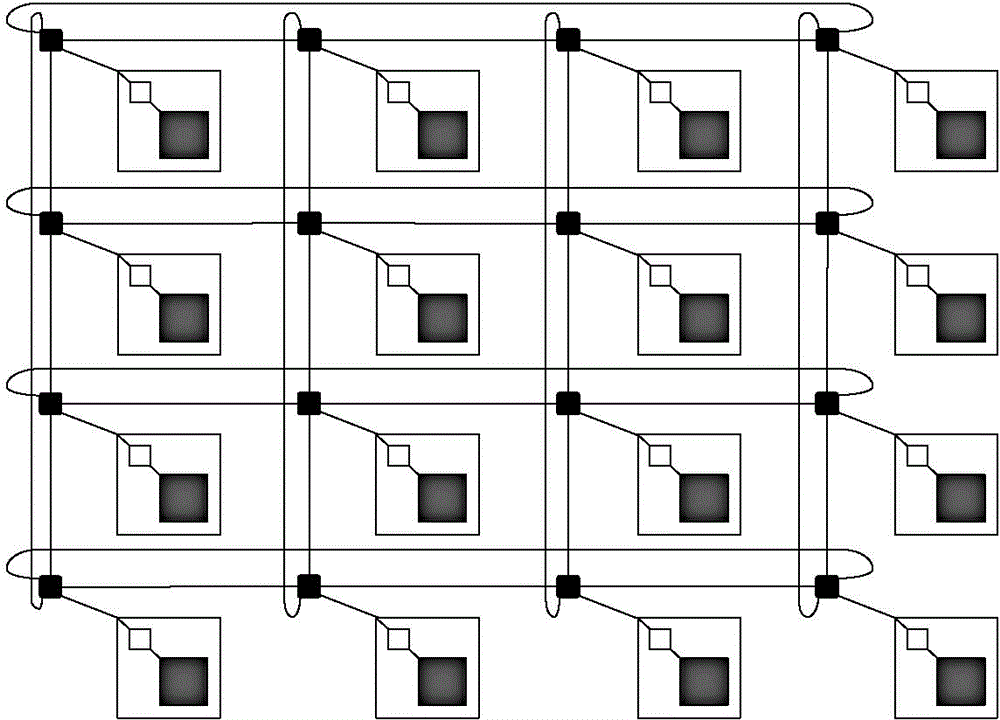

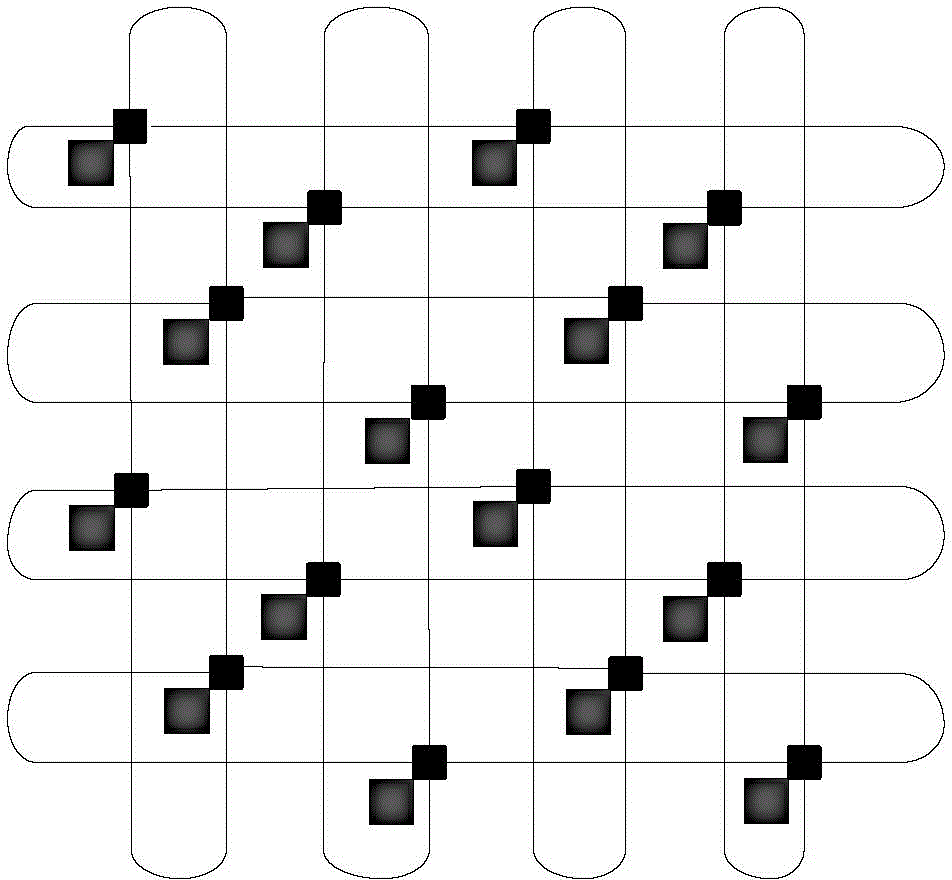

[0052] Such as Figure 8 As shown, the present invention is a hybrid interconnection Mesh topology for on-chip network, which adds a shared bus to ease network congestion and hot spot formation on the basis of traditional Mesh topology. When the Mesh network is not congested, data packets are passed through Mesh topology for transmission; when the Mesh network is relatively congested, it is transmitted through the shared bus, and each routing node corresponds to a pair of input and output ports (B_i and B_o) and a bus interface, and the routing node is connected to the shared bus through the bus interface, such as Figure 9 As shown, a two-bit signal line is added between the output port of the upper-level routing node and the input port of the lower-level routing node to identify the buffer state of the input port of the lower-level routing node.

[0053] The shared bus is only used when the network is congested, that is, only a part of the communication traffic is transmitte...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More