A digital multi-channel analog signal generation method

An analog signal and digital signal technology, which is applied in the field of digital multi-channel analog signal generation, can solve the problems of increased hardware scale and development cost, occupied hardware resources, high filter performance index requirements, and reduced implementation complexity, The effect of reducing complexity and saving I/O resources

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

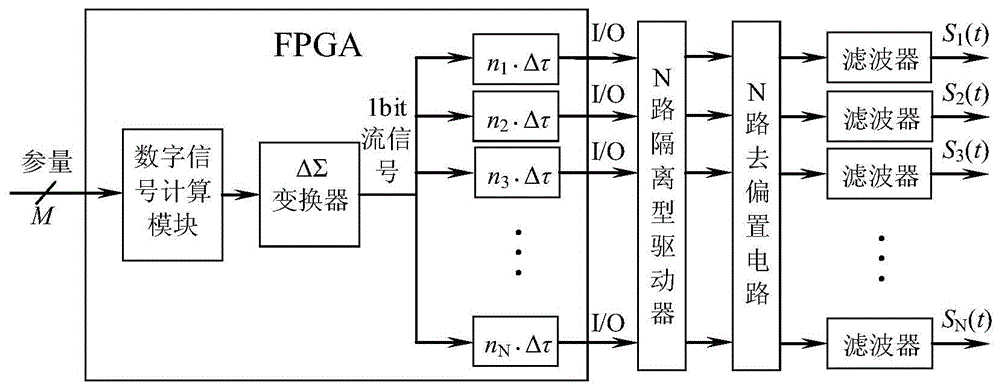

[0024] Such as figure 1 As shown, the FPGA generates N channels of 1-bit stream signals with different delays, and the delay weight is n i The value can be designed according to the needs, i∈[1,2,...,N], the aforementioned N-channel signals pass through N-channel isolated drivers, N-channel debiasing circuits and N-channel filters in sequence, and output N-channel high signal analog signal to noise ratio.

[0025] The FPGA generates N channels of 1-bit stream signals with different delays, which can be realized by the following method,

[0026] M signal parameters are input to the digital signal calculation module, and the digital signal calculation module calculates and obtains a digital signal corresponding to the analog signal to be generated. The aforementioned digital signal is input to the ΔΣ converter, and the 1-bit stream signal generated by the ΔΣ converter undergoes N time delays. After the device, it is output by N I / O pins.

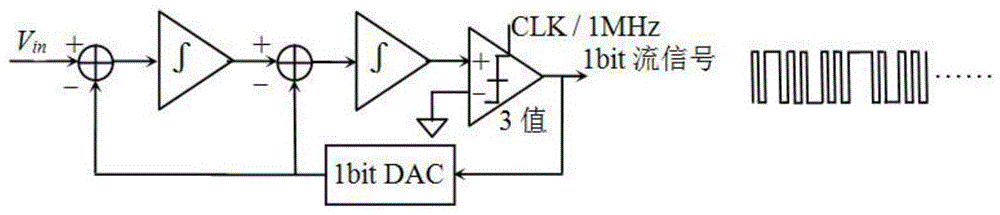

[0027] Delta-sigma converters can be...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More