Storage controller

A storage controller and memory technology, used in instruments, electrical digital data processing, energy-saving computing, etc., can solve the problems of reduced reading speed and high power consumption, and achieve the effects of small unit size, low power consumption, and low cost

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

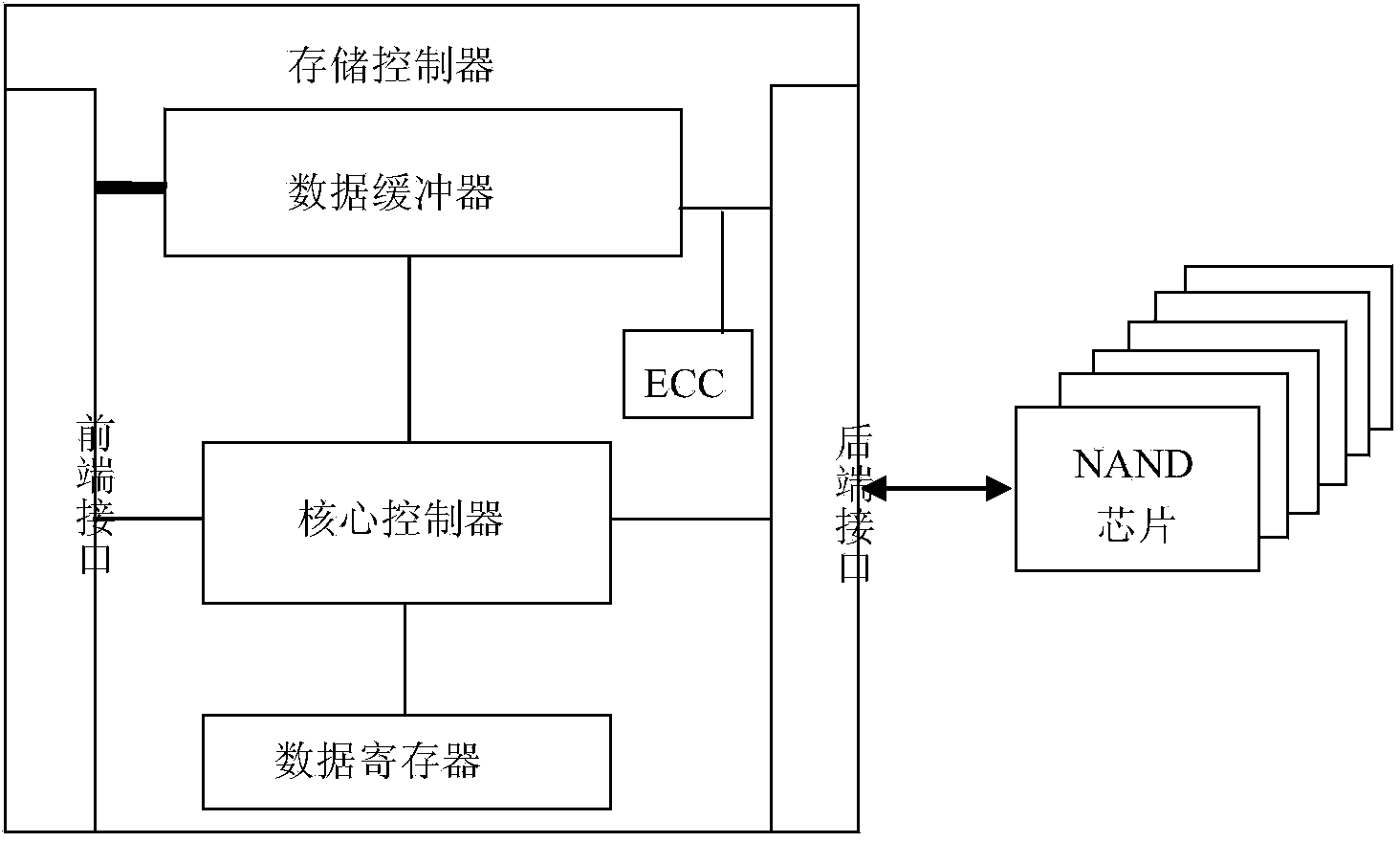

[0026] The invention discloses a storage controller, which is suitable for an operating system to process data on an external storage device. refer to image 3 As shown, it includes a data buffer module (buffer), a data register module (register) and a core controller module (MCU). Both the data buffer module and the data register module are connected to the core controller module. The operating system sends operating instructions to the controller core module, and the core controller module performs data reading, writing, erasing and / or address mapping on the NAND chipset according to the instructions it receives, and performs data processing on the external storage device. Balanced loss control and DMA control operations, further, the controller core module optimizes the data interaction between the operating system and the external memory through the data buffer module according to the received operation instructions.

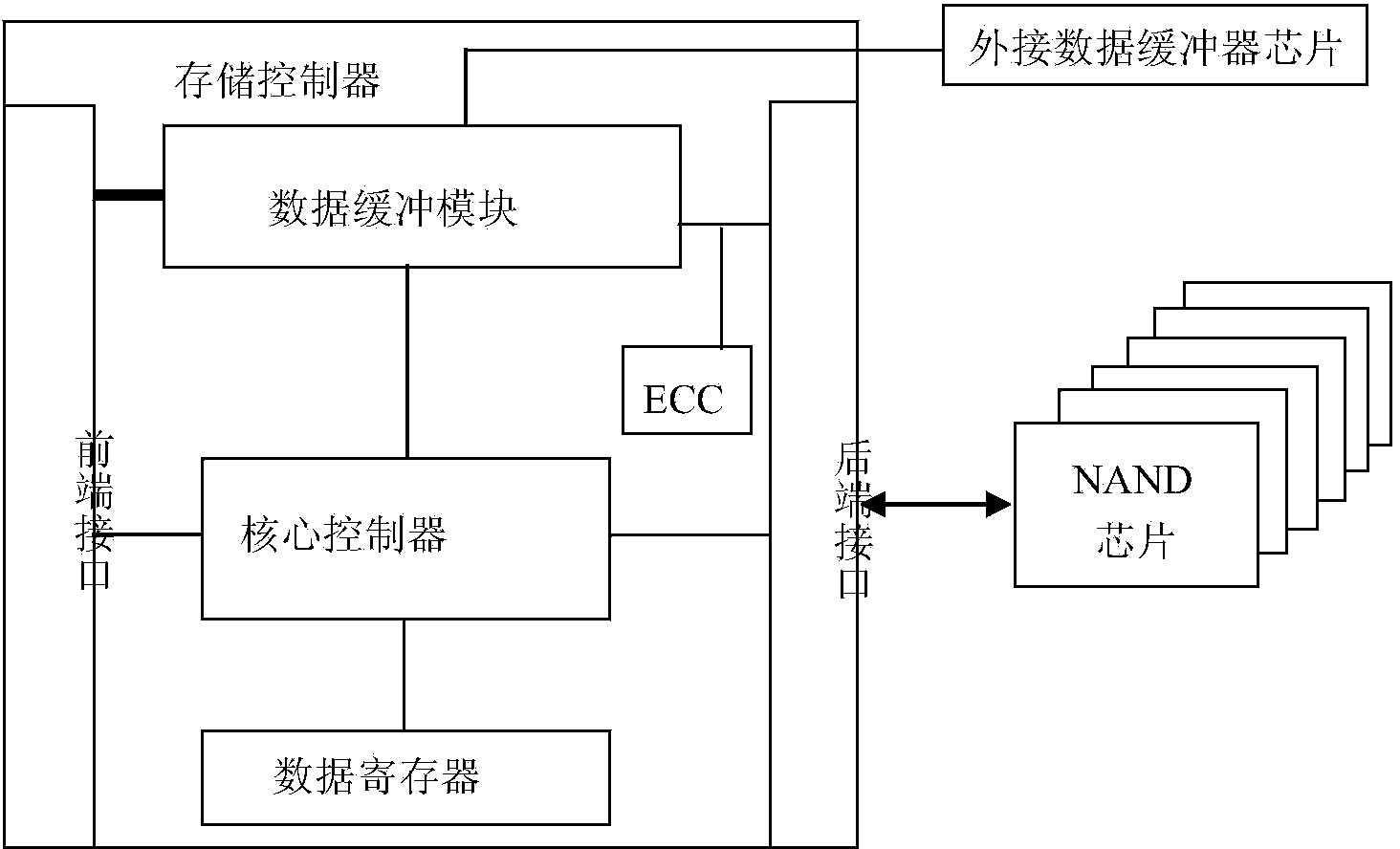

[0027] The storage controller is also provided with a...

Embodiment 2

[0039] A specific embodiment is given below for further elaboration.

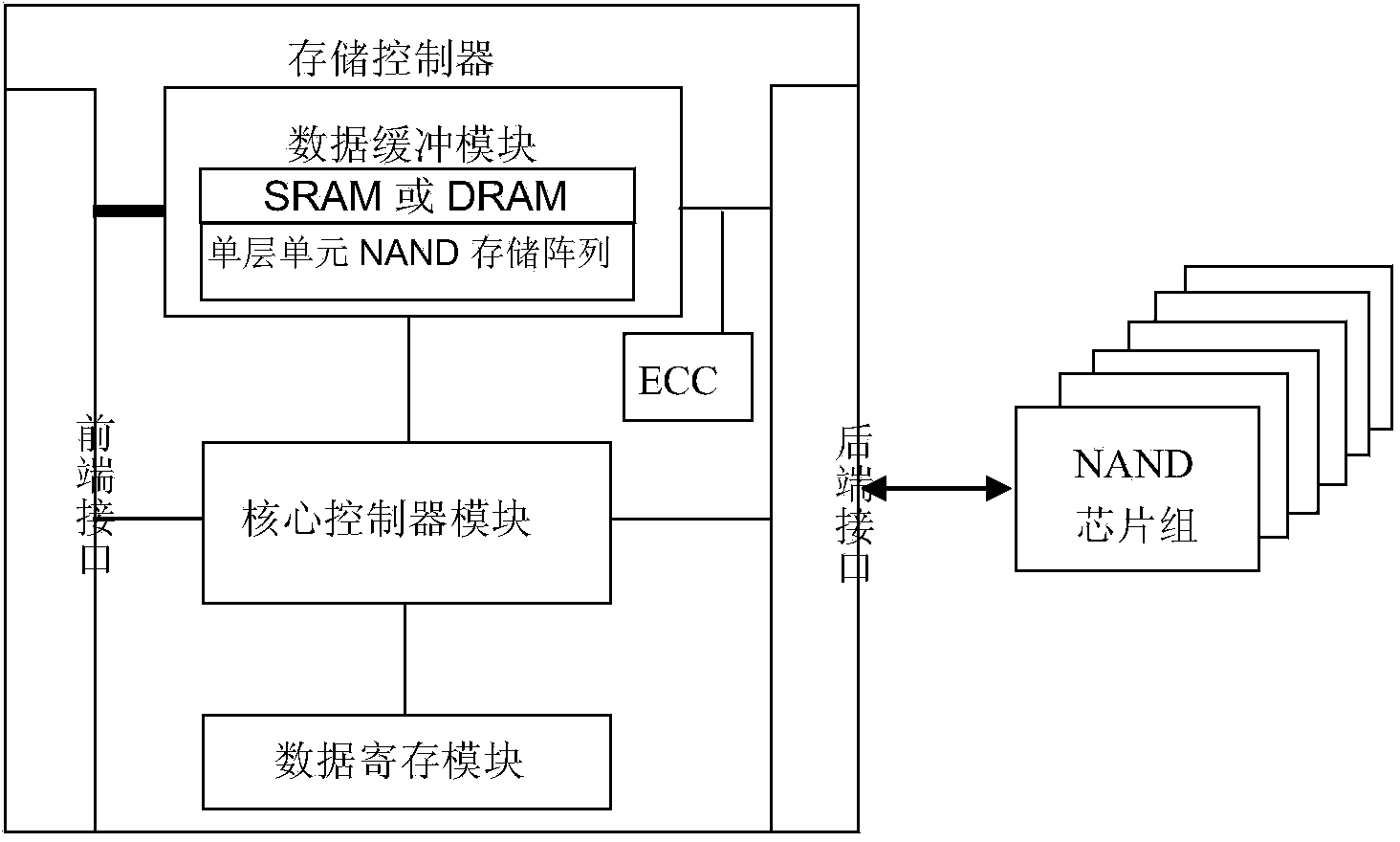

[0040] Assuming that for a 2bit multi-level cell NAND solid state drive per unit, the internal storage controller chip can integrate a single-level cell NAND storage array to replace all traditional data buffers. The structure of the entire solid state drive is as follows: Figure 4 shown. When the system reads data from the SSD, the sequence is: (1) the storage controller accepts the command and reads the page data from the 2bit multi-layer unit NAND chip per unit through the back-end bus; (2) saves the page data to the single (3) The system reads I / O data from the NAND data buffer of the single-layer unit through the front-side bus. When the system writes data to the SSD, the sequence is: (1) the system transmits the data to be written through the front-side bus; (2) saves the I / O data to be written into the single-layer unit NAND data buffer; (3) The storage controller accepts the command and writes th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More