Double-receiving double-emitting programmable ARINC 429 communication interface chip

A technology of double receiving and double sending, communication interface, applied in the field of ARINC429 interface chip, can solve the problems of high power consumption, no receiving FIFO, poor versatility, etc., to achieve the effect of reducing requirements and difficulties, excellent performance and perfect function

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

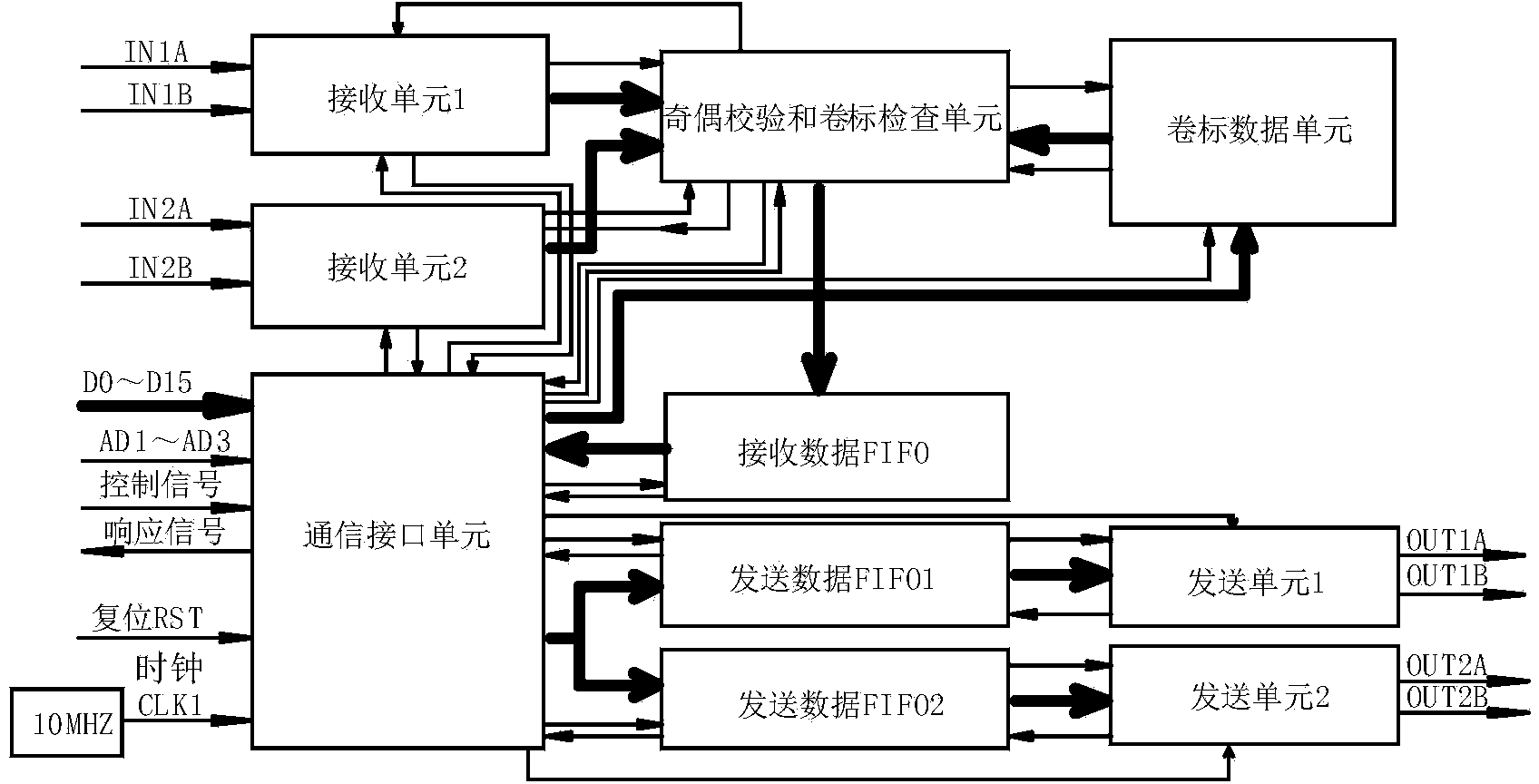

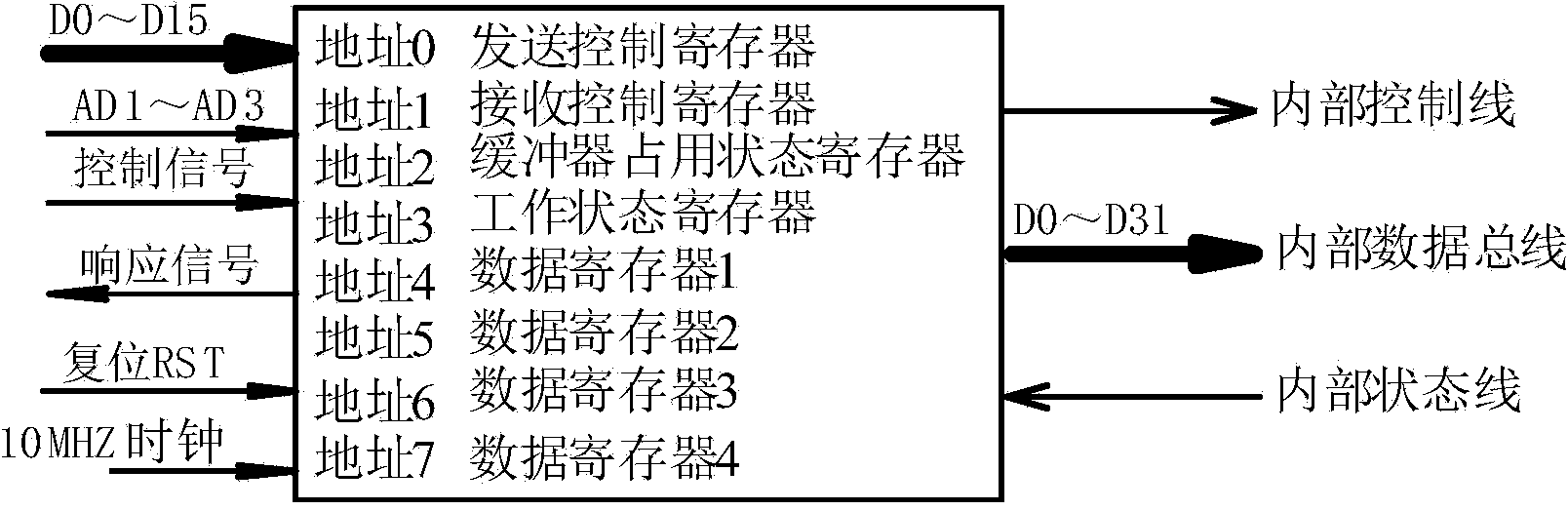

[0018] exist figure 1 The HT429 programmable communication interface chip for double receiving and double sending is an ARINC429 communication chip with programmable control. The HT429 chip has two receiving units, two sending units, a parity check and label checking unit, a communication interface unit, a 64×16bit label data unit, a 32×32 receiving data FIFO, two 16× 32bit send data FIFO. The controller CPU performs data communication with the communication interface unit of the HT429 chip through the bidirectional three-state data bus D0~D15 and the three-bit address line AD1~AD3. The HT429 chip has a data space of 8 addresses. The 16-bit bidirectional data bus and control bus read and write the sending control register, receiving control register, buffer occupation status register and working status register of the HT429 chip to complete the initialization setting and status reading; the two receiving units of the HT429 chip will receive The serial data is converted into ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More