High-speed low-imbalance dynamic comparator for high-speed analog-digital converter

A technology of analog-to-digital converters and dynamic comparators, applied in the direction of analog-to-digital converters, multiple input and output pulse circuits, etc., can solve the problems that affect the comparator's accuracy, limitations, and lack of attention to preamplifiers, etc., to achieve high speed , The effect of reducing the offset voltage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

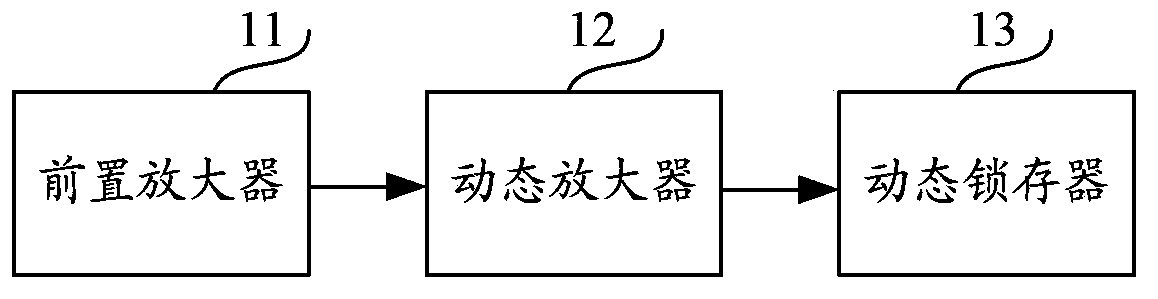

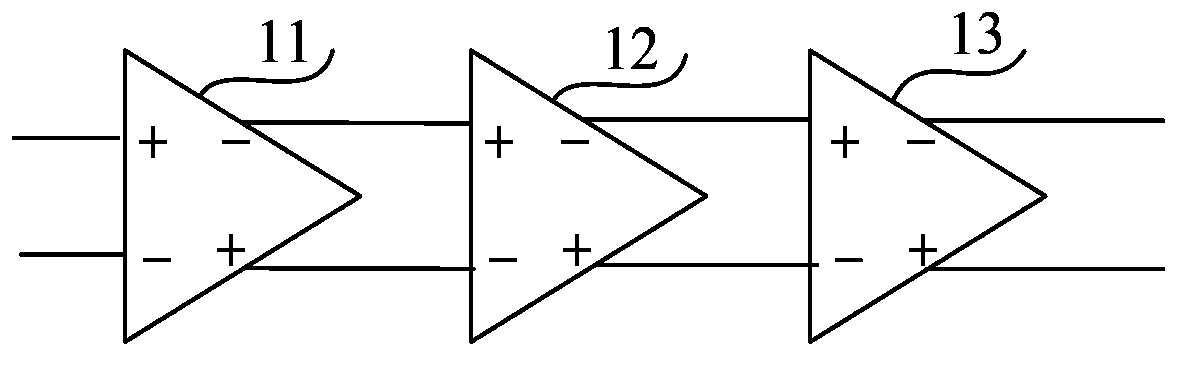

[0061] Such as figure 1 As shown, the high-speed low-offset dynamic comparator for high-speed analog-to-digital converter described in the embodiment of the present invention includes:

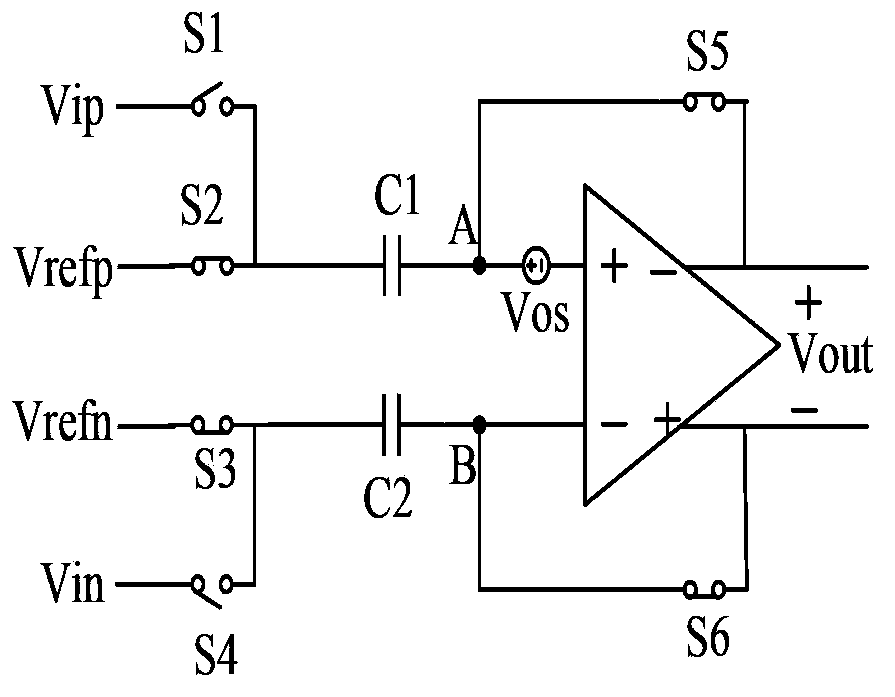

[0062] A preamplifier 11, including a static amplifier, a first input offset storage capacitor and a second input offset storage capacitor;

[0063] The first input offset storage capacitor and the second input offset storage capacitor are respectively connected in series with the non-inverting input terminal of the static amplifier and the inverting input terminal of the static amplifier, so as to store the the offset voltage;

[0064] The dynamic amplifier 12 is used to amplify the output signal of the preamplifier 11, so that the equivalent input offset voltage of the subsequent stage is further reduced;

[0065] The dynamic latch 13 is used to amplify the output signal of the dynamic amplifier 12 and convert the amplified signal into a digital logic level.

[0066] The high-speed low-of...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More