Improved optional grid driving circuit

A driving circuit and selection gate technology, applied in information storage, static memory, instruments, etc., can solve the problems affecting circuit performance, memory reading speed, affecting the speed of SG voltage drop, etc., to speed up the discharge speed, provide reading The effect of taking performance and improving overall performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

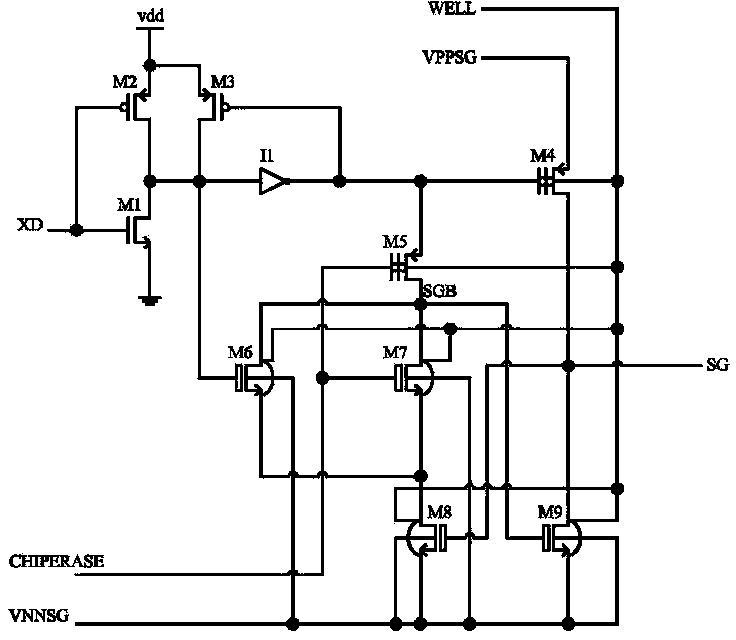

[0028] The present invention will be described in detail below with reference to the accompanying drawings and in combination with embodiments.

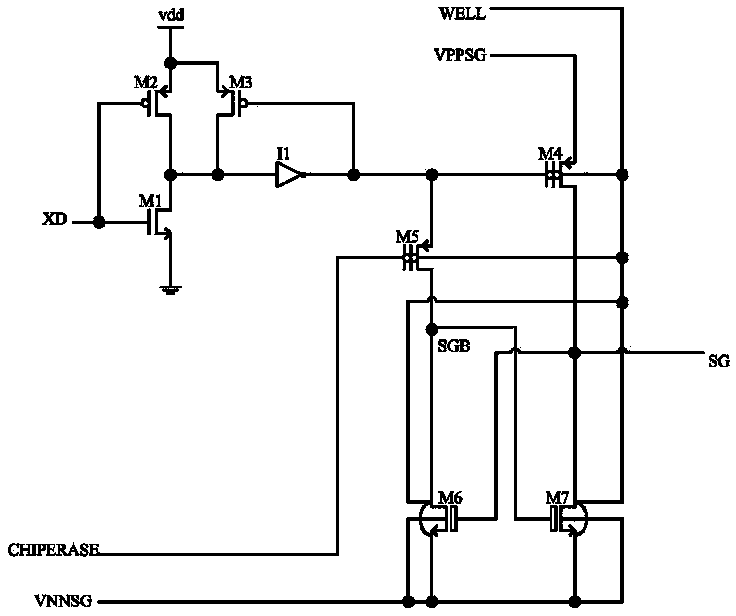

[0029] Such as image 3 As shown, an improved selection gate drive circuit includes a first signal terminal WELL, a second signal terminal VPPSG, a third signal terminal CHIPERASE, a fourth signal terminal VNNSG, a decoder output terminal XD and a signal output terminal SG.

[0030] Wherein, the gate of the first NMOS transistor M1 is connected to the decoder output signal XD, the source of the first NMOS transistor M1 is grounded, the drain of the first NMOS transistor M1 is connected to the drain of the first PMOS transistor M2, and the first PMOS The gate of the transistor M2 is connected to the decoder output signal XD, and the source of the first PMOS transistor M2 is connected to the power supply voltage vdd. The gate of the second PMOS transistor M3 is connected to the output terminal of the first inverter I1, the source of t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More