Chip-type digital relay protection system

A relay protection and chip technology, applied in the field of power system, can solve problems such as limiting the reliability and stability improvement of relay protection devices

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0016] The present invention is further described below in conjunction with accompanying drawing and embodiment:

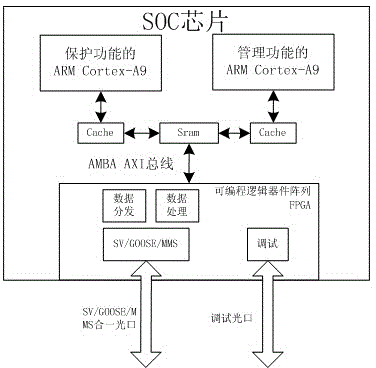

[0017] Such as figure 1 As shown, the SOC chip includes a Cortex-A9 processor with a protection function, a Cortex-A9 processor with a management function, a programmable logic device array FPGA, an AMBA AXI bus, a cache memory Cache, and an on-chip static random access memory SRAM. SOC chip can provide DDR3, DDR3L, DDR2, LPDDR2, SRAM, FLASH memory interface.

[0018] Programmable logic device array FPGA (Field-Programmable Gate Array), that is, field programmable gate array, is a product of further development on the basis of programmable devices such as PAL, GAL, and CPLD. In the present invention, the programmable logic device array FPGA is used as the core part of the digital relay protection device. The advantages of the programmable logic device array FPGA are that it contains abundant external programmable interfaces, and has strong expansion capability. ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More