Method of forming semiconductor device

A semiconductor and device technology, applied in the field of semiconductor device formation, can solve problems such as poor TDDB performance of NMOS metal gate transistors, and achieve the effect of improving TDDB performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

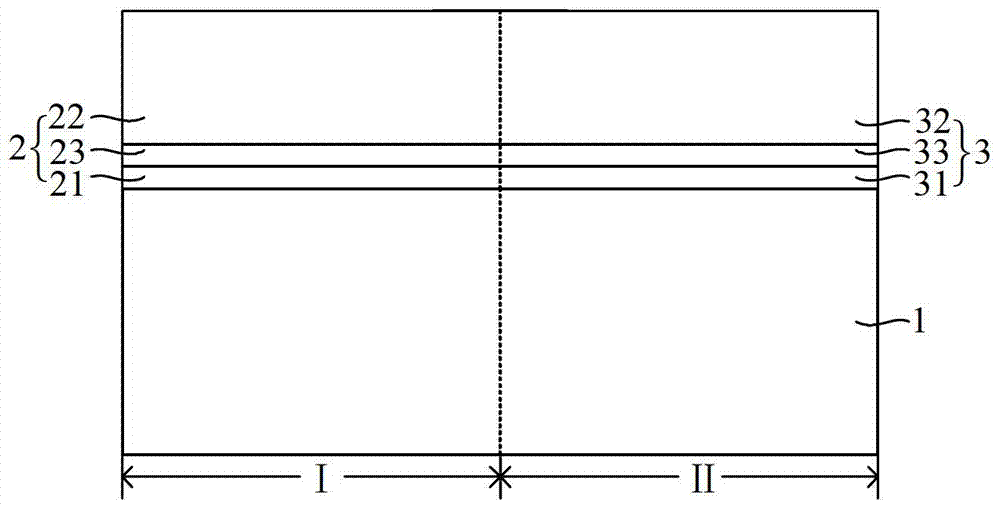

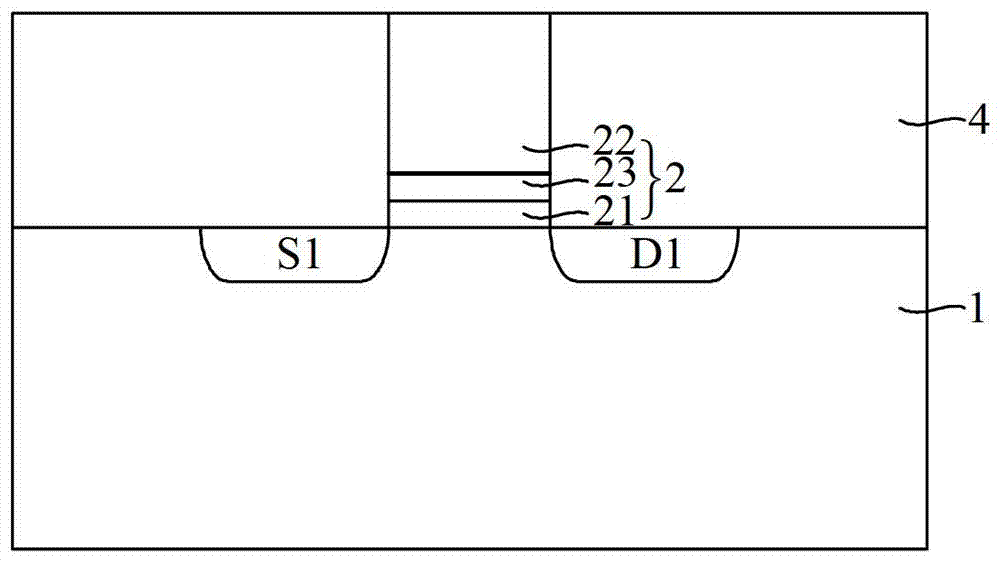

[0065] like Figure 6A and Figure 6B As shown, a substrate 100 is provided, and the substrate 100 includes a PMOS transistor region I and an NMOS transistor region II.

[0066] The substrate 100 may be a common substrate such as a silicon substrate, a silicon germanium substrate, gallium arsenic, and the like. The PMOS transistor region I of the substrate 100 is used to form a PMOS metal gate transistor, and the NMOS transistor region II of the substrate 100 is used to form an NMOS metal gate transistor.

[0067] Then, continue to refer to Figure 6A and Figure 6B As shown, a first dummy gate structure 110 is formed on the PMOS transistor region I of the substrate 100, and a second dummy gate structure 120 is formed on the NMOS transistor region II. The first dummy gate structure 110 includes a first gate dielectric layer 111 and the first dummy gate 112 on the first gate dielectric layer 111, the second dummy gate structure 120 includes the second gate dielectric layer ...

no. 2 example

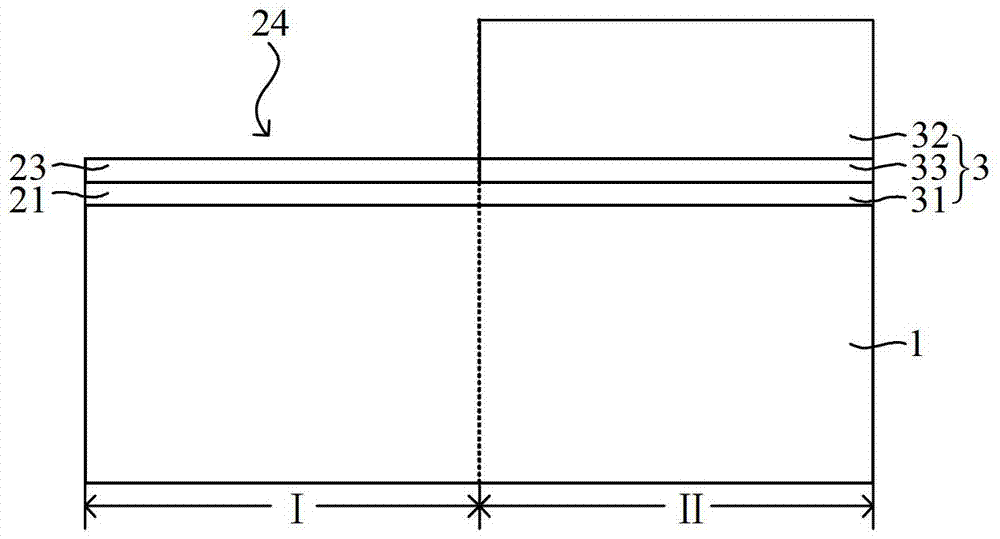

[0108] The difference between the second embodiment and the first embodiment is that in the second embodiment, there is no metal hard mask layer between the silicon oxide layer and the photoresist layer during the step of removing the first dummy gate.

[0109] In other words, in the second embodiment, the method for removing the first dummy gate includes: forming a silicon oxide layer on the interlayer dielectric layer, the first dummy gate, and the second dummy gate, and forming a silicon oxide layer on the silicon oxide layer. Resist layer; patterning the photoresist layer and the silicon oxide layer to form openings in the photoresist layer and the silicon oxide layer, the opening corresponds to the position of the first dummy gate, and the bottom of the opening exposes the first dummy gate A dummy gate; using the patterned photoresist layer and the patterned silicon oxide layer as a mask to perform dry etching to remove the first dummy gate and form a first dummy gate at t...

no. 3 example

[0112] The difference between the third embodiment and the first embodiment is that in the third embodiment, the plasma treatment step is performed in an ashing machine, and the process parameters of the plasma treatment include: N 2 The flow rate is 500 to 10000sccm (inclusive), the pressure is 100 to 2000mTorr (inclusive), the power supply is 500 to 5000W (inclusive), the time is 10 to 600s (inclusive), and the temperature is 100 to 400°C (inclusive endpoint).

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More