Forming method of transistor

A transistor and gas technology, applied in the field of semiconductor manufacturing, can solve the problems such as the quality of embedded germanium and silicon needs to be improved, and achieve the effects of reducing the time for entering and exiting epitaxy equipment, reducing the generation cycle, and improving production efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

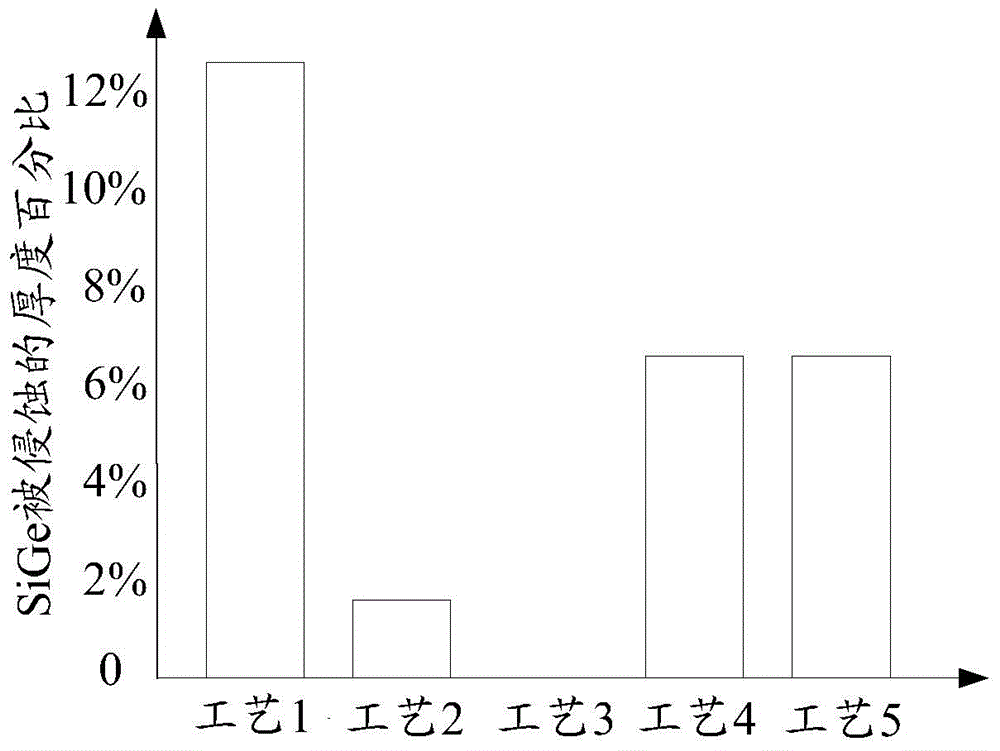

[0034] It can be seen from the background art that the quality of the germanium-silicon stress layer in the transistor formed in the prior art needs to be improved.

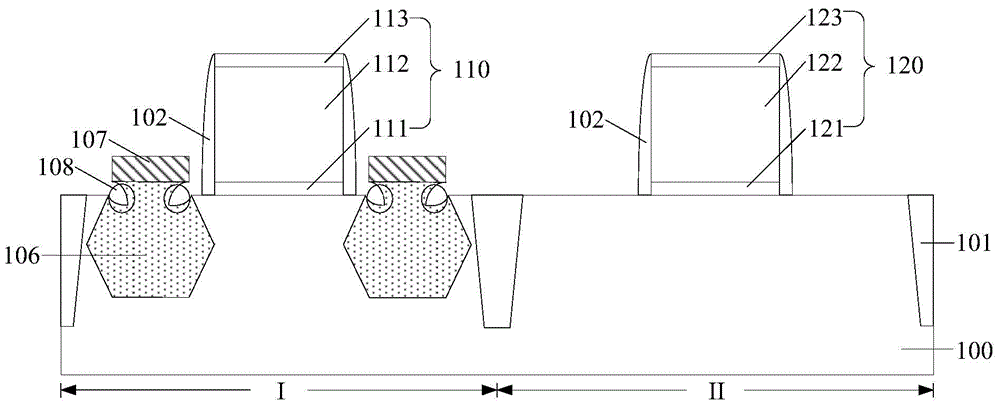

[0035] For this reason, the formation process of the transistor is studied, and the formation process of the transistor is used as an example. The formation process of the transistor includes the following steps, please refer to figure 1 :

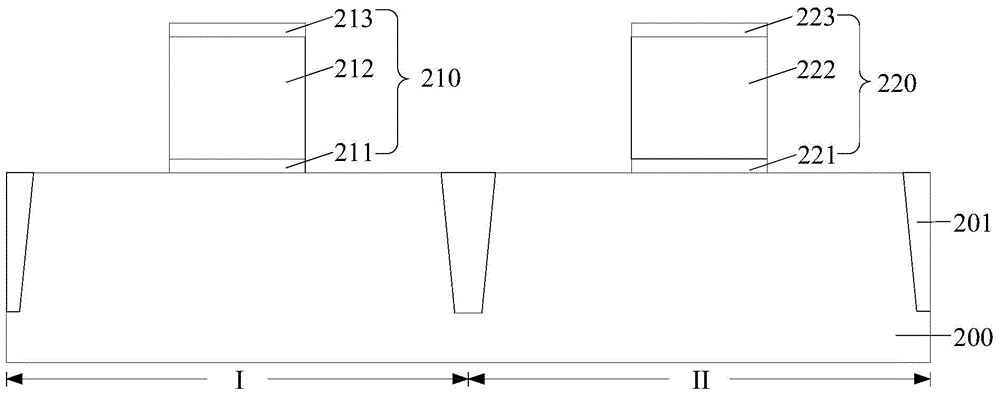

[0036] Provide a semiconductor substrate 100, an isolation structure 101 is formed in the semiconductor substrate 100, the semiconductor substrate 100 includes a PMOS region and an NMOS region, and a first gate structure 110 is formed on the surface of the semiconductor substrate 100 in the PMOS region , the second gate structure 120 is formed on the surface of the semiconductor substrate 100 in the NMOS region, and the first gate structure 110 includes a first gate oxide layer 111 located on the surface of the semiconductor substrate 100, a gate oxide layer located on the fi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More