Method for adding redundancy patterns to photoetching map

A technology of redundant graphics and layout, applied in special data processing applications, instruments, electrical digital data processing, etc., can solve problems such as graphics depression, reduce defects, avoid copper wire damage, and improve product qualification rates.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0031] The invention provides a method for designing a lithographic layout, which can be applied to processes with technology nodes of 90nm, 65 / 55nm, 45 / 40nm, 32 / 28nm, greater than or equal to 130nm, and less than or equal to 22nm; it can be applied to the following technical platforms : Logic, Memory, RF, HV, Analog / Power, MEMS, CIS, Flash and eFlash.

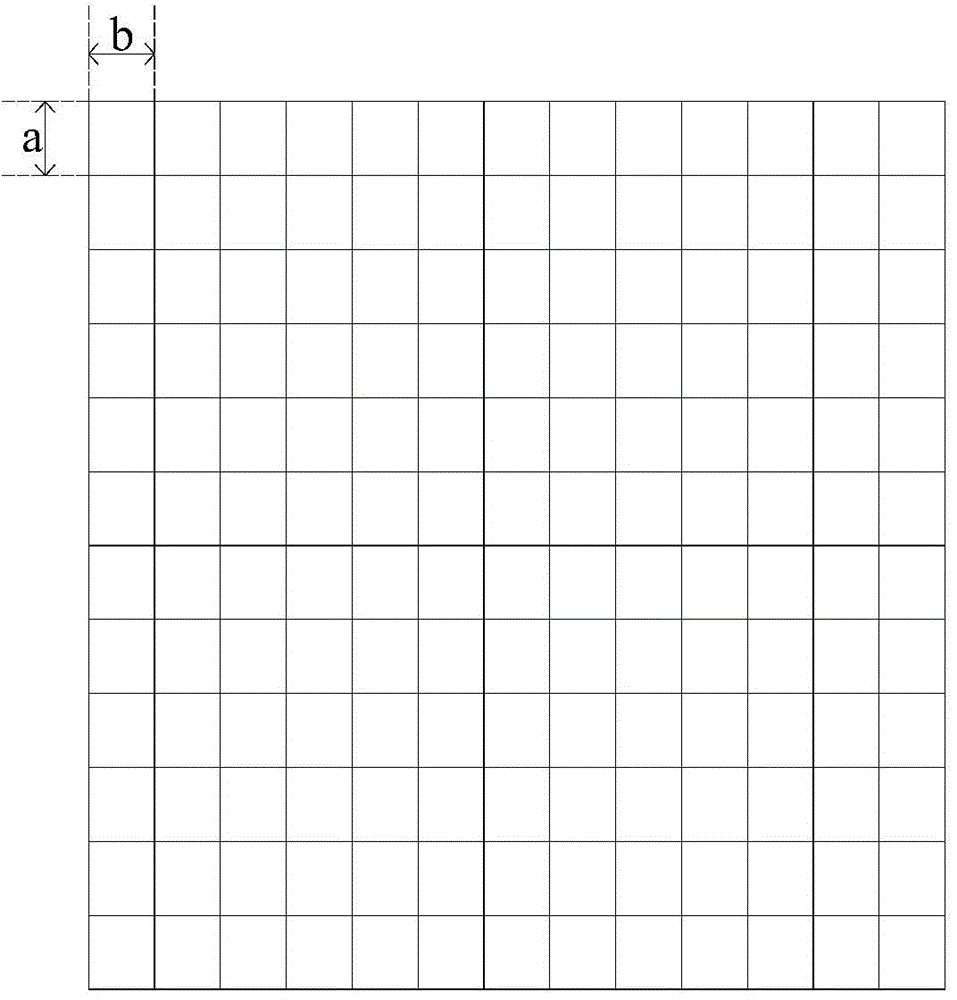

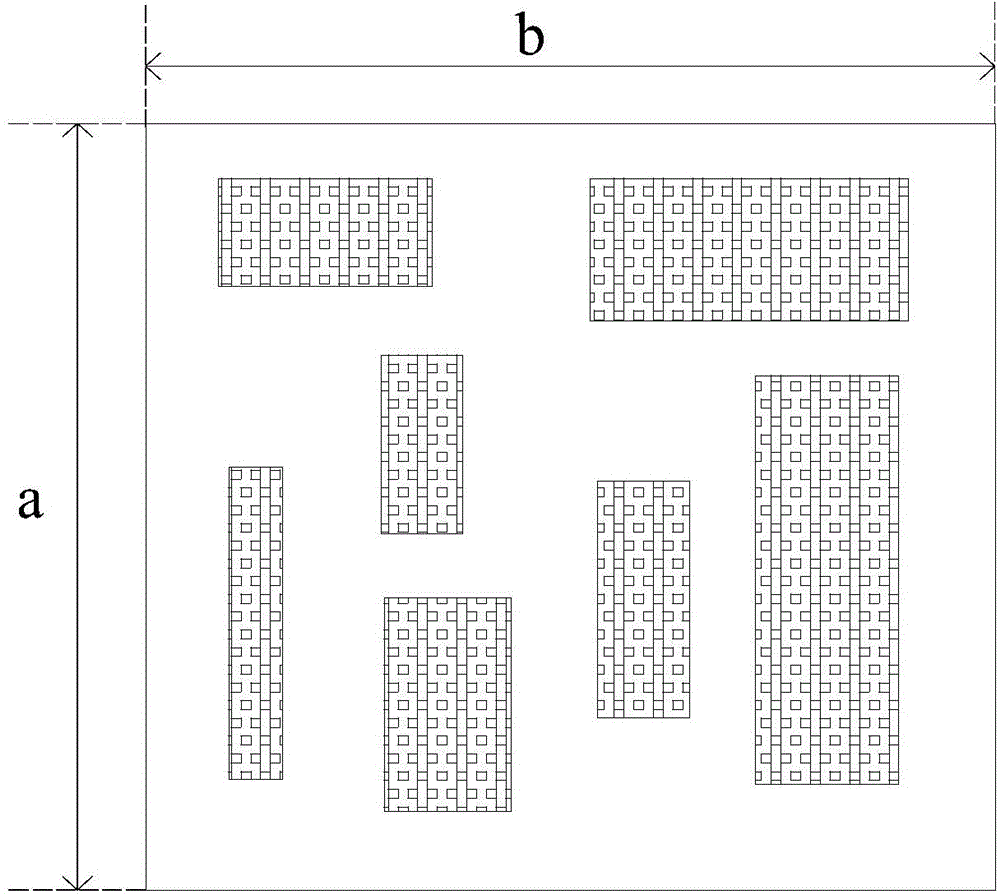

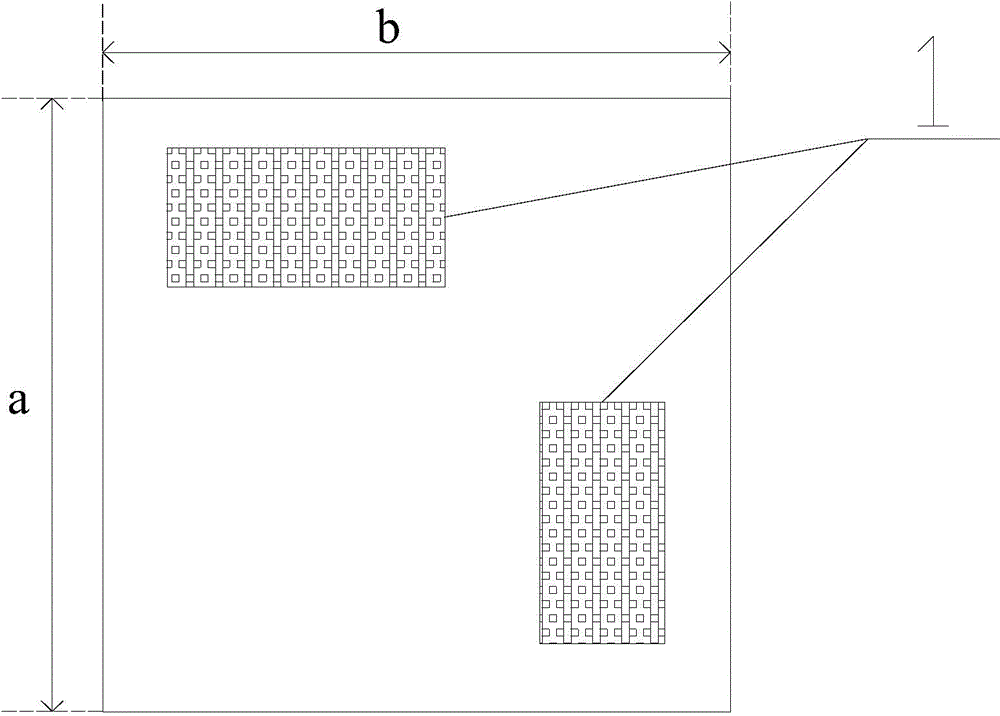

[0032] The core idea of the present invention is by dividing the layout of the completed device design into several areas, and obtaining the ratio of the area occupied by all design graphics on each area to the total perimeter of all design graphics, and then respectively passing The above data of each area judge whether to add redundant graphics to each area separately, and finally make the area density and number density distribution of the graphics on the entire wafer uniform, so that when the wafer is undergoing the CMP process, the grinding The speed is consistent, avoiding the problems of erosion and dishing on the waf...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More