Drive device for image collecting system of interline transfer CCD sensor

A technology of an image acquisition system and a driving device, which is applied in the parts of TV systems, image communication, and color TV parts, etc., can solve the problems of difficult driver programming and circuit debugging, transmission distance and speed restrictions, and complex timing adjustment. And other issues

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0030] The present invention will be described in further detail below in conjunction with the accompanying drawings.

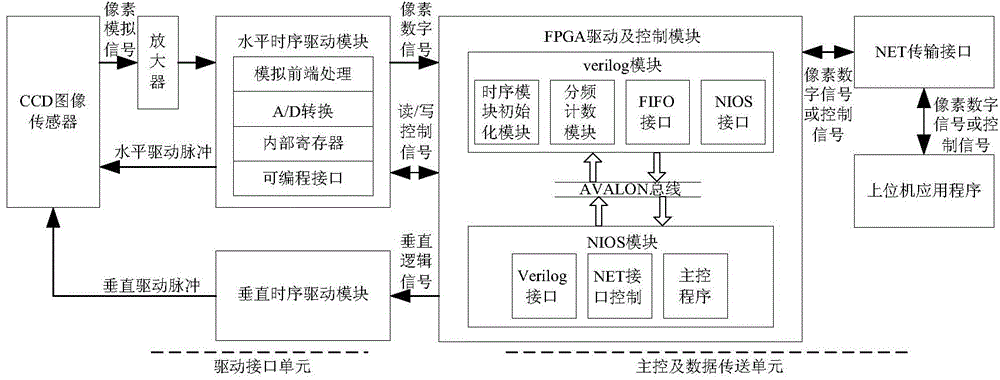

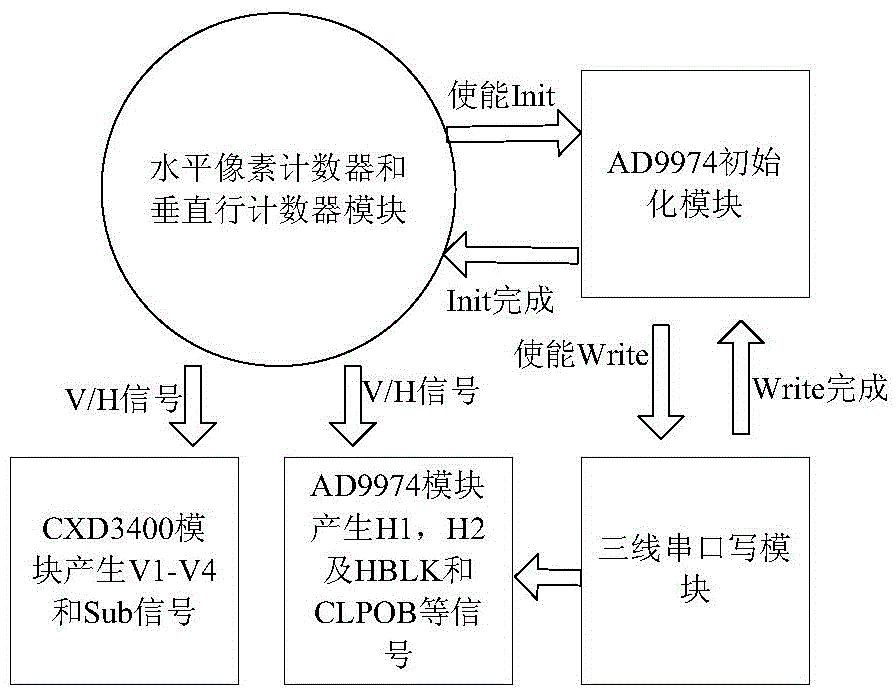

[0031] The design idea proposed by the invention can be applied to the driving design of inter-line transfer CCD image sensors that have different timing requirements. Such as figure 1As shown in the block diagram of the drive circuit, this design divides the circuit into two parts: the drive interface unit and the main control and data transmission unit. The drive interface unit outputs horizontal drive pulses and vertical drive pulses to the CCD image sensor. The pixel analog signal output by the CCD image sensor is amplified by the amplifier and then input to the horizontal timing drive module for analog front-end processing and analog-to-digital conversion. The converted pixel digital signal Send back to the FIFO interface sub-module inside the FPGA chip and wait for the host computer to accept the data. The FPGA chip of the main control and data transm...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com