Three-dimensional on-chip optical network topology and routing path calculation method

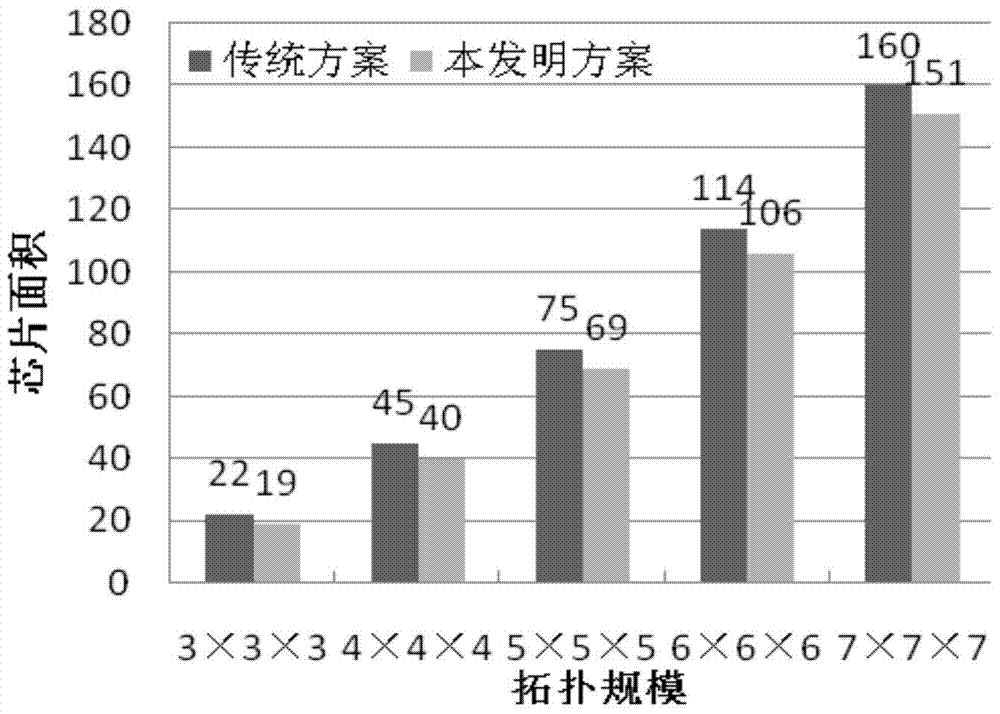

A technology of network topology and path calculation, applied in the field of communication, can solve the problems of waste of chip resources, redundant deployment of optical router components, large transmission delay at zero load, etc., and achieve the effect of reducing chip area and reducing chip resource consumption.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

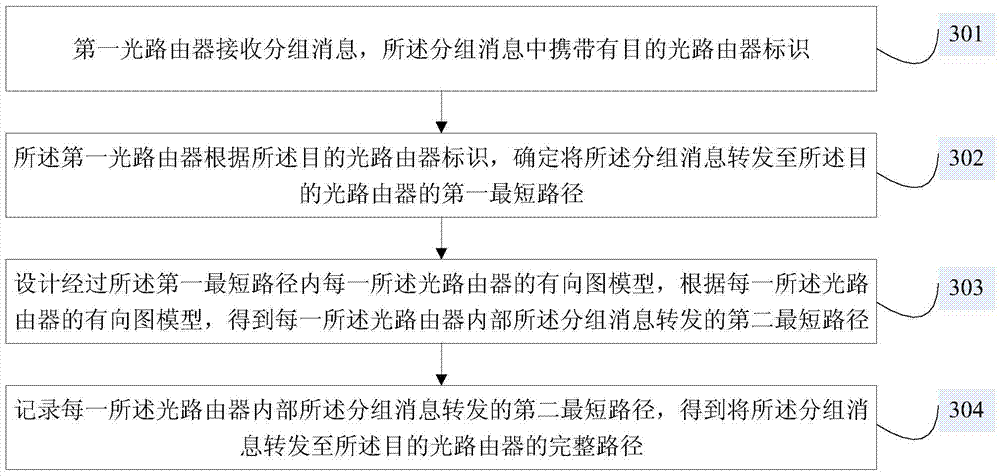

[0044] The specific implementation manners of the present invention will be further described below in conjunction with the drawings and examples. The following examples are used to illustrate the present invention, but are not intended to limit the scope of the present invention.

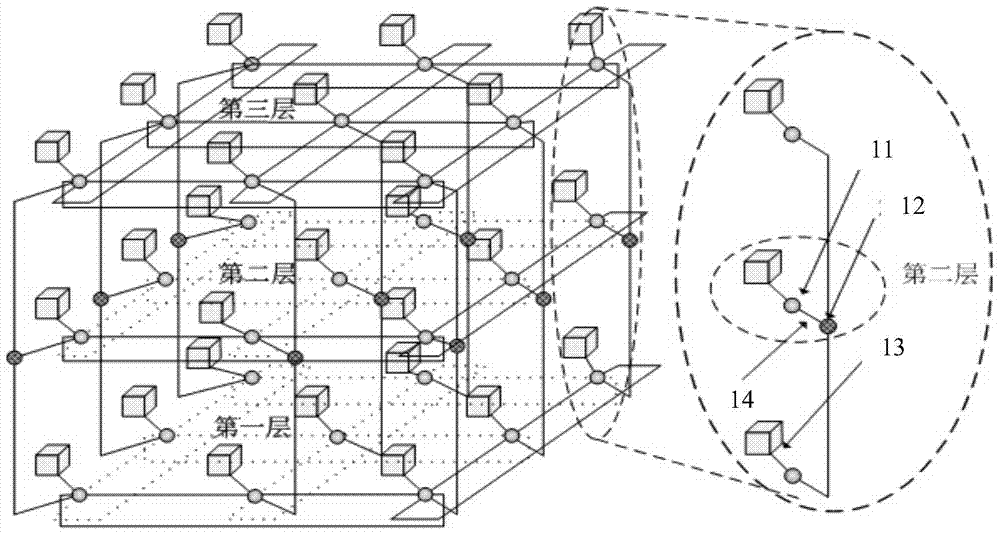

[0045] The three-dimensional on-chip optical network topology of this embodiment may include: N optical routing layers, each of which includes N rows×N columns of optical routers, each of which is connected to an IP core, at least one Each of the optical routers in the optical routing layer is also connected to a vertical optical router;

[0046] Wherein, the N is a natural number greater than or equal to 3.

[0047] Further, each of the optical routing layers is a loop topology, and the connection of the optical routers in each of the optical routing layers is:

[0048] Each of the optical routers is connected to adjacent optical routers, and the first optical router in each row or column is als...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More